1

Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и автоматики для получения противофазных импульсов с симметричными фронтами регулируемой крутизны.

Известен генератор противофаз-.. ных импульсов на МОП-транзисторах| 1.

Основными недостатками устройства является сложность, а также, отсутствие симметрии выходных противофазных импульсов и невозможность регулирования крутизны их фронтов.

Наиболее близким техническим решением к изобретению является формирователь импульсов на комплементарных МОП-транзисторах, содержащий управляющую, первую и вторую выходные шины, шины питания разряда и выходные каскады, первый и второй конденсаторы и зарядные транзисторы 2 .

Недостатками, известного формирователя также являются сложность схемного решения, отсутствие симметрии и возможности регулирования крутизны фронтов выходных противофазных импульсов. Несимметрия выходных противофазнь1х импульсов связана с тем, что из-за наличия обратных связей

переход сигнала на одном из выходов от высокого уровня к низкому начинается лишь после того, как потенциал на другом выходе достигнет уровня порогового напряжения п-канального транзистора.

Целью изобретения является .повышение надежности путем упрощения устройства, сокращения числа

10 элементов, а также обеспечения взаимной симметрии выходных импульсов н возможности регулировки крутизны их фронтов.

Поставленная цель достигается -тем,

15 что в формирователь парафадных импульсов, содержащий 5{правляющую, входную, первую и вторую выходные шины, первую и- вторую шины питания, первый и второй выходные каскады на допол20няющих МДП-транзисторах, первый и второй конденсаторы, первый и второй зарядные МДП-транзисторы, подключенные к соответствующим конденсаторам и входам выходшлх каскадов, введен 25 дополнительный МДП-трйнзистрр, сток. ,и исток которого .подключены к входам выходных каскадов, причем об.щая шина первого выходного каскада подключена к входу второго выходного

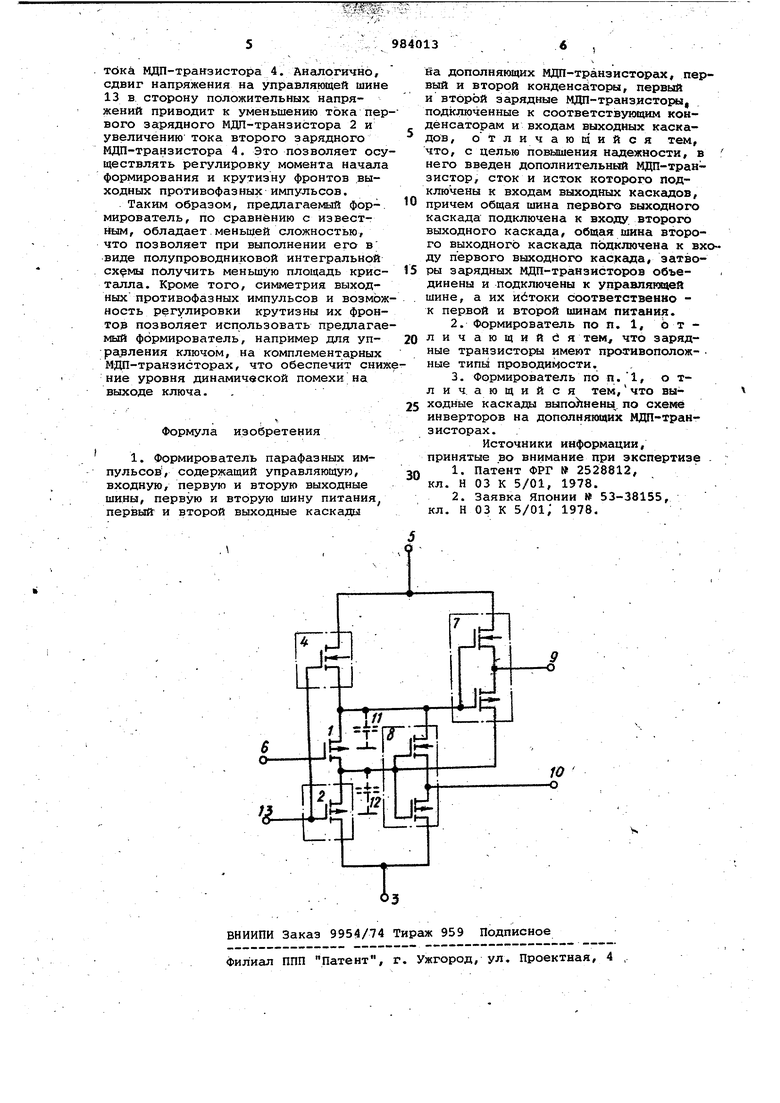

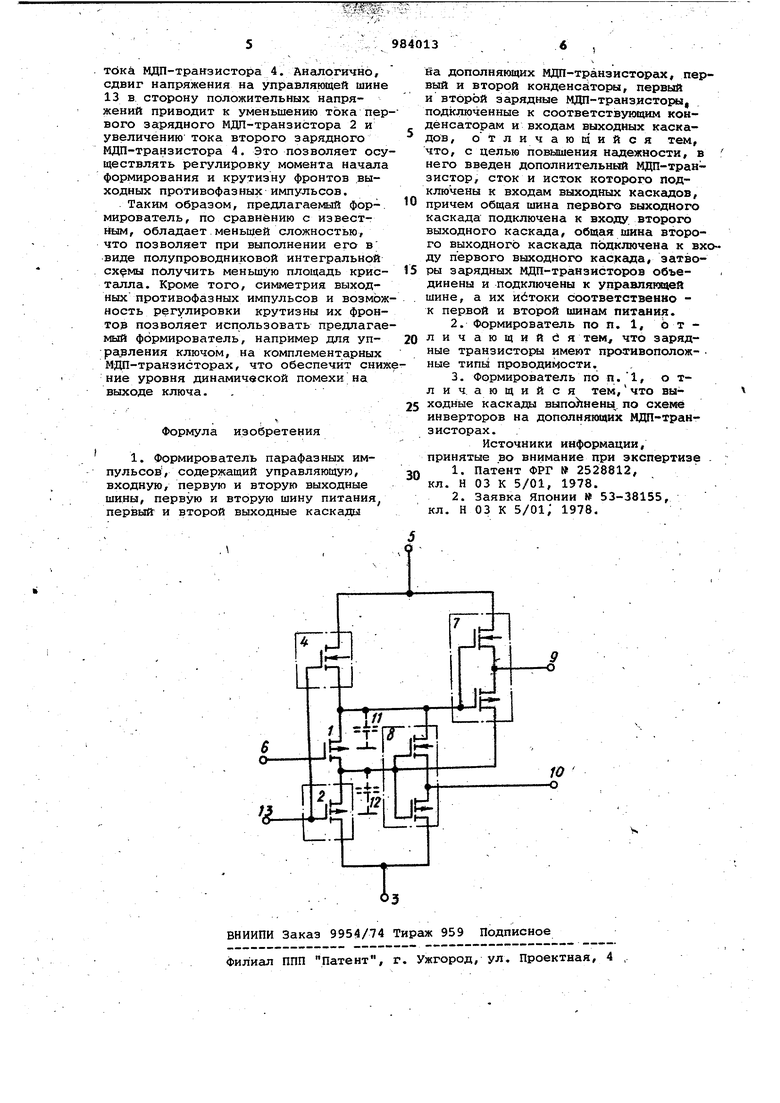

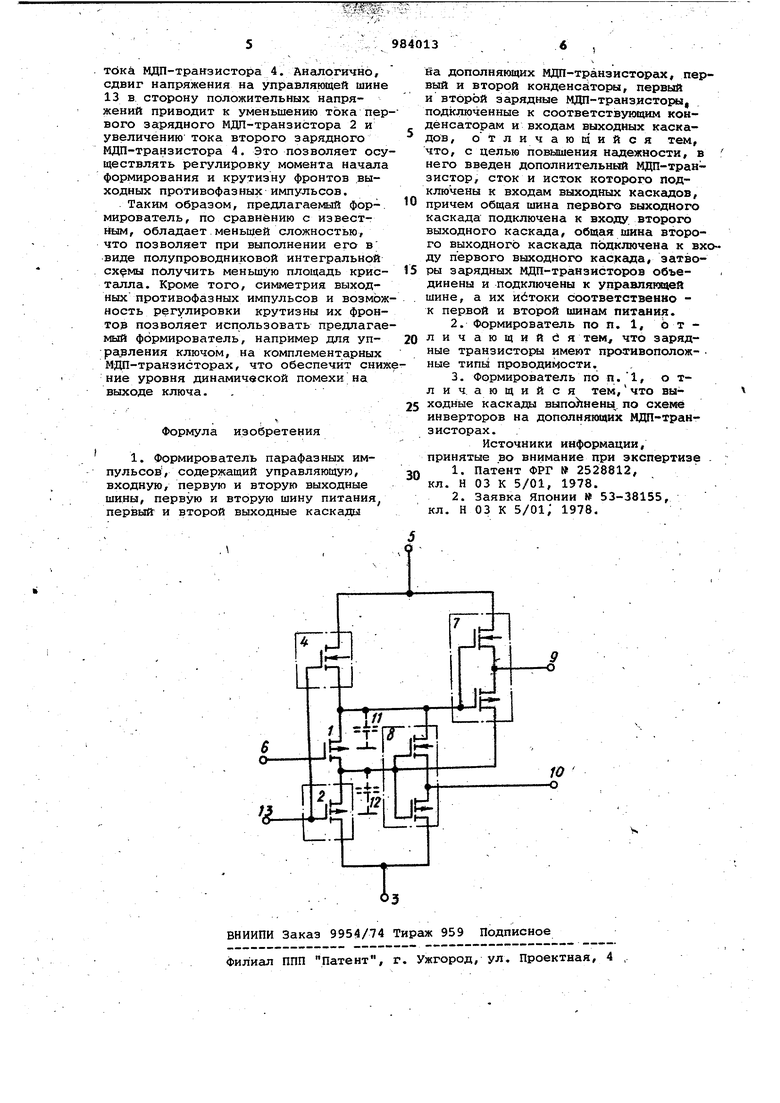

30 каскада, общая шина второго выходного каскада подключена к входу пер вого выходного каскада, затворы зар ных МДП-транзисторов объединены и подключены к управляющей шине, а их истоки соответственно - к первой и второй шинам питания, Зарядные транзисторы имеют проти воположные типы проводимости. Выходные каскады выполнены по сх ме-инверторов на дополняющих МДП-тр зисторах. Крутизна п-канального транзистор первого выходного каскада выбрана равной крутизне р-канального транзи тора второго выходного каскада, крутизна р-канального транзистора первого выходного каскада выбрана равной крутизне п-канального-транзистора второго выходного каскада, Токи зарядных транзисторов и пороговые напряжения р- и п-канальных транзисторов равны между собой.. Такое выполнение устройства позволяет упростить его путем сокра щения числа элементов, добиться высокой степени взаимной симметричнос ти выходных противофазных.импульсов и обеспечить возможность регулировки крутизны их фронтов. На чертеже приведена схема предлагаемО1 о генератора противофазных импульсов на МДП-транзисторах. .Генератор содержит дополнительны р-канальный ЙДП-транзистор 1, исток которого через первый зарядный МДП,транзистор 2 соединен с шиной положительного напряжения питания 3, сток через второй зарядный МЛП-тран зистор 4 соединен с шиной отрицател ного напряжения питания 5, а затвор соединен с входной шиной 6. Первый выходной каскад 7 включен между шиной отрицательного напряжения питания 5 и входом второго выходного-ка када 8, который, в свою очередь, включен между входом nepBOt-o выходного каскада 7 .и шиной положительно го напряжения питания 3, причем вход первого выходного каскада 7 соединен со стоком дополнительно1 о -МДИ-транзистора 1, а его выход - с первой выходной ш|1ной 9, вход второ го выходного каскада 8 соединен с истоком дополнительного МДЩ-транзис тора 1, а его выход - со второй выходной шиной 10, вход первого выход ного каскада 7 связан с первым конденсатором 11, а вход второго выход ного каскада, ,8 - с вторым конденсато ром 12. . , Затвори МДП-транзисторов 2 и 4. объединены и подключены к управляющей шине 13. Устройс1:во работает следующим образом. В исходном состоянии на управляющую шину 13 подается потенциал, близ КИЙ к нулевому, при этом МДП-транзис;торы 2 и 4открыты. Пр.и поступлении на входную Шину б положительногб сигнала, уровень которого близок к положительному напряжению питания, МДП-транзистор 1 запирается и конденсаторы 11 и 12, связанные с его истоком и .стоком, начинают заряжаться одинаковыми токами через открытые .МДП-транзисторы 2 и 4. При разности потенциалов между стоком и истоком МДП-транзистора 1, равной пороговому напряжению,р-канальный транзистор первого выходного каскада 7 и п-канальной транзистор второго выходного каскада 8 открываются, и на первой 9 и второй 10 выходных шинах формируются соответственно положительный и отрицательный уровни первого и второго выходных сигналов. При поступлении на входную шину б отрицательного сигнала МДП-транзистор 1открывается и конденсаторы 11 и 12, связанные сузлами его истока и стока, заряженные до напряжения соответственно положительного и отрицательного источников питания, начинают перезаряжаться через открытый МДПтранзистор 1 и соответственно первый 2и второй 4 зарядные МДП-транзисторы. При изменении потенциалов истока и стока МДП-транзистора 1 относительно соответствующих напряжений питания на величины, превышающие пороговые напряжения, соответственно п-канального транзистора первого выходного каскада 7 и р-канального транзистора выходного каскада 8 упомянутые МДП-транзисторы открываются и на первой 9 и второй 10.выходных шинах начинают формироваться соответственно отрицательный и положительный уровни первого и второго выходных сигналов. Поскольку конденсаторы 11 и 12, связанные с узлами истока и стока МДП-транзистора 1, близки друг к другу/ в силу симметрии схемы, а крутизны п- и р-канального транзисторов: первого выходного каскада 7 равны крутизне/соответственно р- и п-канального транзисторов второго и выходного каскада 8, абсолютные величины пороговых напряжений упомянутых МДП-транзисторов и токи МДП-транзисторов 2 и 4 равны между собой, моменты начала формирования и скорости измерения сигналов на первой 9 и второй 10 выходных шинах совпадают, что обеспечивает симметрию выходных парафазных импульсов. Сдвиг напряжения на управляющей шине 13 в сторону отрицательного напряжения приводит к увеличению тока МДП-транзистора 2 за счет большего отпирания р-канального МДП-транзистора и соответственно - к уменьшеиюо тока МДП-транзистора 4. Аналогично, сдвиг напряжения на управляющей шин 1J в сторону положительных напряжений приводит к уменьшению тока пе вого зарядного МДП-транзистора 2 и увеличению тока второго зарядного МДП-транзистора 4. Это позволяет ос ществлять регулировку момента начал формирования и крутизну фронтов выходных противофазных импульсов. Таким образом, предлагаемый формирователь, по сравнению с известным, обладает.меньшей сложностью, что позволяет при выполнении его в виде полупроводниковой интегральной схемы получить меньшую площадь крис талла. Кроме того, симметрия выходных противофазных импульсов и возмо ность регулировки крутизны их фрон тов позволяет использовать предлага мый формирователь, например для упрадления ключом, на комплементарных мдп-транзисторах, что обеспечит сни ние уровня динамической помехи на выходе ключа. . Формула изобретения 1. Формирователь парафазных импульсов, содержащий управляющую, входную, первую и вторую выходные шины, первую и вторую шину питания первый- и второй выходные каскады а дополняющих МДП-транзисторах, первый и второй конденсаторы, первый и второй зарядные МДП-транзисторы подключенные к соответствующим конденсаторам и входам выходных каскадов, отличающийся тем, что, с «елью повышения надежности, в него введен дополнительный МДП-транзистор, сток и исток которого подключены к входам выходных каскадов, причем общая шина первбго выходного каскада подключена к входу второго выходного каскада, общая шина второго выходного каскада пЬдключена к входу первого выходного каскада, затворы зарядных МДП-транзисторов объединены и подключены к управлягачей шине, а их ибтоки соответственно к первой и второй шинам питания. 2.Формирователь по п. 1, 6тличающий 5 я тем, что зарядные транзисторы имеют противополож- . ные типы проводимости. 3.Формирователь по п.1, отличающийся тем,что выходные каскады выпо 1нены,. по схеме инверторов на дополнянмцих МДП-транзисторах. .. Источники информации, принятые во внимание при экспертизе Патент ФРГ 2528812, кл. Н 03 К 5/01, 1978. 2. Заявка Японии 53-38155 кл. Н 03 К 5/Oi; 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1984 |

|

SU1170599A1 |

| Формирователь импульса по включению напряжения питания | 1985 |

|

SU1272496A1 |

| Аналоговый ключ | 1980 |

|

SU928645A1 |

| Формирователь импульсов на мдп-транзисторах | 1974 |

|

SU503353A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Усилитель-формирователь на металло= диэлектрических полупроводниковых транзисторах | 1974 |

|

SU531284A2 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ | 2013 |

|

RU2545325C1 |

Авторы

Даты

1982-12-23—Публикация

1981-02-23—Подача