Изобретение относится к автоматике и вычр слительной технике, в частности к запоминающим элементам цифровых устройств.

Известна запоминающая ячейка для регистра сдвига, выполненная на МДП-транзистоpax и содержащая четыре щииьт импульсного питания 1. Достоинство ее - малая потребляемая мопдиость, недостаток - низкое быстродействие.

Наиболее близким техиическим решением является запоминающая ячейка памяти для регистра сдвига, содержащая каскады, каждый из них состоит из зарядного МДП-транзистора, затвор которого подключен к информационному входу ячейки и к первой обкладке МДИ-конденсатора, сток - к второй обкладке МДП-кондеисатора и к первой щине импульсного питания, разрядного МДП-транзистора, затвор которого подключен к второй щние имиульсного питания, исток - к щине нулевого потенциала, сток - к затвору зарядного МДП-транзистора последующего каскада 2. Однако такая ячейка не обеспечивает высокой надежности работы, так как при сдвиге нескольких следующих одна за другой единиц носледующая логическая единица разрушает предыдущую.

Цель изобретения - иовыщение надежности работы ячейки. Это достигается тем, что запоминающая

ячейка содержит в каждом каскаде разделительный МДП-транзнстор, затвор и сток которого подключены к стоку и истоку зарядного МДП-транзнстора соответственно, а исток разделительного МДИ-транзистора - к стоку разрядного МДП-транзистора.

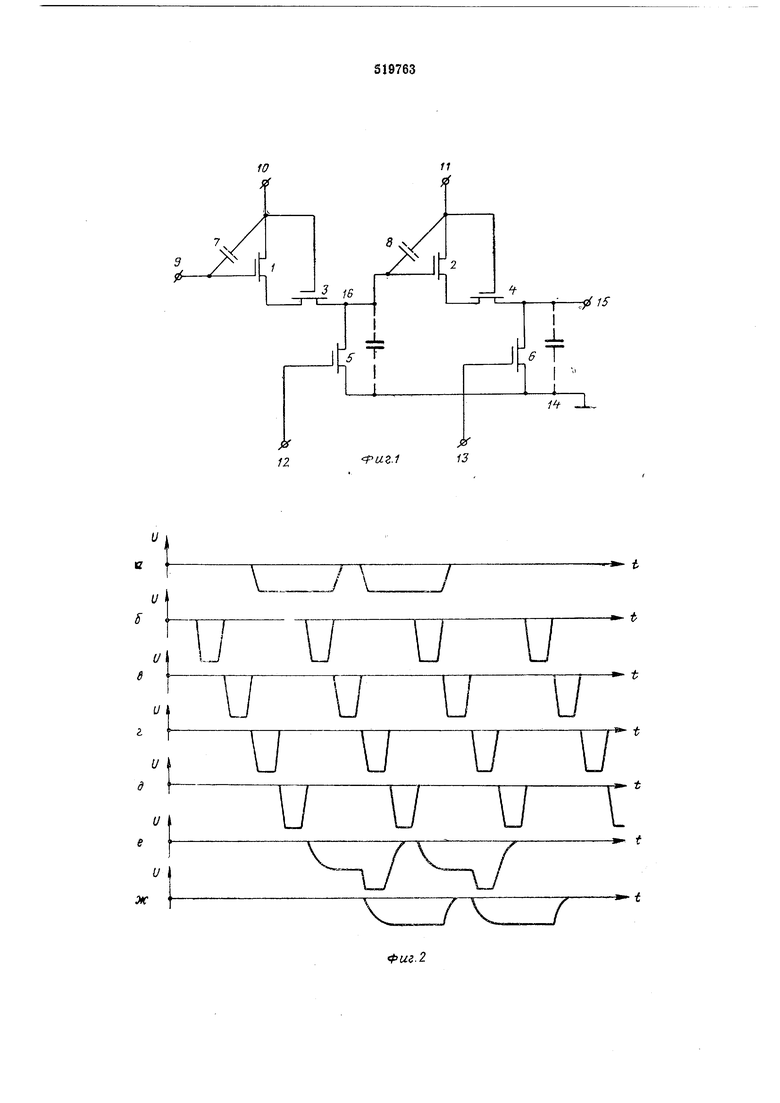

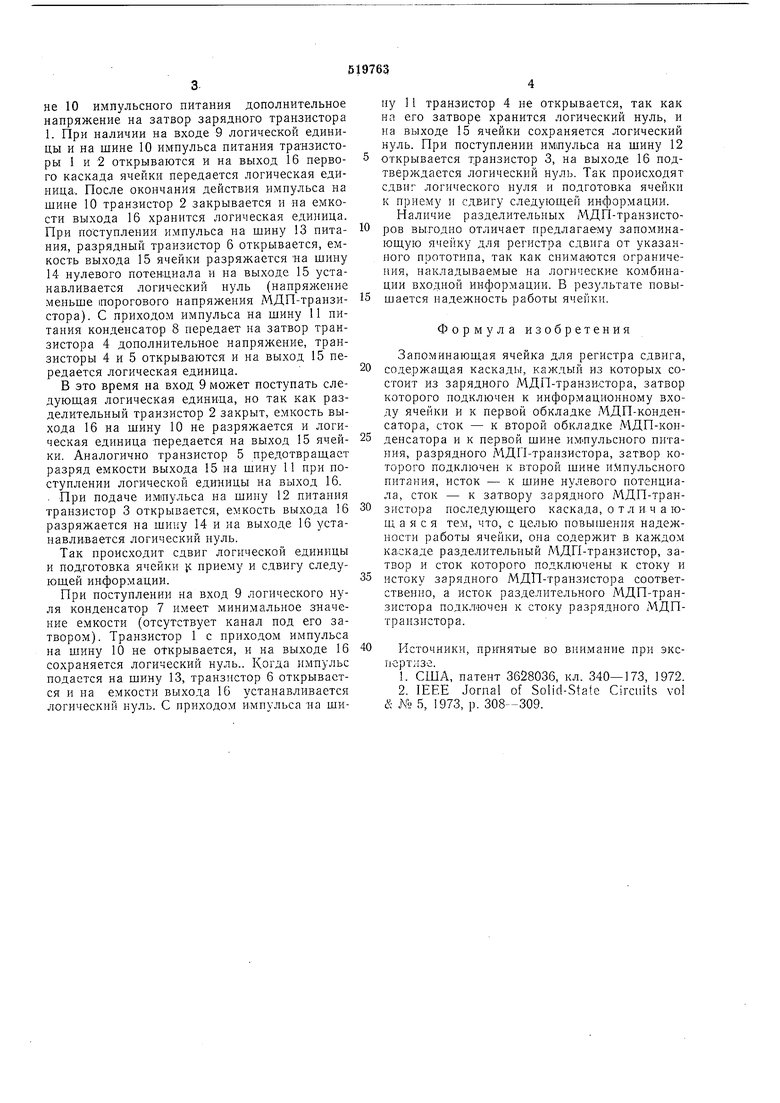

На фиг. 1 представлена принципиальиая электрическая схема запоминающей ячейки для регистра сдвига; на фиг. 2 - временные диаграммы входных си.гиалов (о.), импульсного питания (б-д), сигналов на выходе первого каскада (с) и выходе ячейки (ж).

Заиомннающая ячейка для регистра сдвига, выполненная }ia шести МДП-транзисторах с индицированным каналом, содер-жит зарядные транзисторы 1 Н 2; разделительное транзисторы 3 и 4; разрядные транзисторы 5 и 6; МДПконденсаторы 7 и 8. На фиг. 1 обозначено: 9- вход ячейки; 10-13 - щины нмиульсного питания; 14 - щииа нулевого потенциала; 15- выход ячейки; 16 - выход первого каскада.

При поступлении на вход 9 ячейки логической единицы (напряжение, нревыщающее пороговое напряжение МДП-транзистора) под затвором конденсатора 7 индуцируется канал, служап ий одной из обкладок этого конденсатора.

Полученный таким образом конденсатор используется в качестве ускоряющей емкости, передающей при появлении импульса на щине 10 импульсного питания дополнительное напряжение на затвор зарядного транзистора 1. При наличии на входе 9 логической единицы и на шине 10 импульса питания транзисторы 1 и 2 открываются и на выход 16 первого каскада ячейки передается логическая единица. После окончания действия импульса на шине 10 транзистор 2 закрывается и на емкости выхода 16 хранится логическая единица. При поступлении импульса на шину 13 питания, разрядный транзистор 6 открывается, емкость выхода 15 ячейки разряжается на шину 14 нулевого потенциала и на выходе 15 устанавливается логический нуль (напряжение меньше порогового напряжения А ДП-транзистора). С приходом импульса на шину 11 питания конденсатор 8 передает на затвор транзистора 4 дополнительное напряжение, транзисторы 4 и 5 открываются и на выход 15 передается логическая единица.

В это время на вход 9 может поступать следуюш,ая логическая единица, но так как разделительный транзистор 2 закрыт, емкость выхода 16 на шину 10 не разряжается и логическая единица -передается на выход 15 ячейки. Аналогично транзистор 5 предотвращает разряд емкости выхода 15 на шину 11 при поступлении логической единицы на выход 16. . При подаче имлульса на шину 12 питания транзистор 3 открывается, емкость выхода 16 разряжается на шину 14 и на выходе 16 устанавливается логический нуль.

Так происходит сдвиг логической единицы и подготовка ячейки j приему и сдвигу следующей информации.

При поступлении на вход 9 логического нуля конденсатор 7 имеет минимальное значение емкости (отсутствует канал под его затвором). Транзистор 1 с приходом импульса на шину 10 не обрывается, и на выходе 16 сохраняется логический нуль.. Когда импульс подается на шину 13, транзистор 6 открывается и на емкости выхода 16 устанавливается логический нуль. С приходом импульса на шину 11 транзистор 4 не открывается, так как на его затворе хранится логический нуль, и на выходе 15 ячейки сохраняется логический нуль. При поступлении импульса на шину 12

открывается транзистор 3, на выходе 16 подтверждается логический нуль. Так происходят сдвиг логического нуля и подготовка ячейки к приел1у и сдвигу следующей информации. Наличие разделительных Л1ДП-транзисторов выгодно отличает предлагаему запоминающую ячейку для регистра сдвига от указанного прототипа, так как снимаются ограничения, накладываемые на логические комбинации входной информации. В результате повышается надежность работы ячейки.

Формула изобретения

Запоминающая ячейка для регистра сдвига, содержащая каскады, каждый из которых состоит из зарядного МДП-транзистора, затвор которого подключен к информационному входу ячейки и к первой обкладке МДП-конденсатора, сток - к второй обкладке МДП-конденсатора и к первой шине импульсного питания, разрядного МДП-транзистора, затвор которого подключен к второй шине импульсного питания, исток - к шине нулевого потенциала, сток - к затвору зарядного МДП-транзистора последующего каскада, о тл ич а ющ а я с я тем, что, с целью повышения надежности работы ячейки, она содержит в каждом ка-скаде разделительный МДП-транзистор, затвор и сток которого подключены к стоку и

истоку зарядного МДП-транзистора соответственно, а исток разделительного МДП-транзистора подключен к стоку разрядного МДПтранзистора.

Источники, принятые во внимание при экспертлзе.

1.СШу, патент 3628036, кл. 340-173, 1972

2.IEEE Jornal of Solid-State Circuits vo & N« 5, 1973, p. 308-309.

Ю

11 f

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Буферное устройство на мдп-транзисторах | 1973 |

|

SU458099A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

9 f

1 16

J

12

I JL

I JU

T I

т I

,L:i.

/

Ж

13

fuz.t

Авторы

Даты

1976-06-30—Публикация

1974-07-26—Подача