Область техники

Изобретение относится к микроэлектронике, более конкретно к интегральным микросхемам со структурой кремний-на-изоляторе (КНИ), образованным комплементарными N-канальными и P-канальными транзисторами со структурой металл-окисел-полупроводник (КМОП).

Уровень техники

Известна КМОП КНИ интегральная микросхема (КМОП КНИ ИМС), образованная N-канальными и P-канальными КМОП транзисторами, каждый из которых имеет затвор, сток, исток и область тела транзистора, с каждым из этих транзисторов общей областью стока и истока неотделимо связан подложечный соответственно N-канальный или P-канальный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка КНИ структуры, которая является одним из выводов КМОП КНИ ИМС. Известная КМОП КНИ ИМС содержит систему-на-кристалле (СнК), образованную транзисторами названного типа, выполняющую функции преобразования и/или хранения информации, вывод подложки КМОП КНИ ИМС подключен к общей шине.

Подключение вывода подложки КМОП КНИ ИМС к общей шине является типовым и применяется в практике проектирования КМОП КНИ ИМС как стандартное техническое решение. Примером использования известного устройства являются серийно выпускаемые КМОП КНИ ИМС 1830ВЕ32У, 1830ВЕ52У («Микросхемы интегральные 1830ВЕ32У, 1830ВЕ52У. Техническое описание». - http://www.sigma-project.ru/files/products/57.pdf. - [1]; В.А. Смерек, А.И. Яньков, А.В. Крюков. «Микроконтроллер 1830ВЕ32У - 8-ми разрядная архитектура MCS-51 в радиационно-стойком исполнении». - http://www.mes-conference.ru/data/year2010/papers/m10-304-40093.pdf [2]).

Микросхемы в соответствии с известным устройством размещаются в 48-выводном корпусе, в котором обратная сторона КНИ структуры, являющаяся выводом подложки, через соединение с металлизированной монтажной площадкой корпуса электрически связана общей шиной.

Подложечные транзисторы в КМОП КНИ ИМС, поведение которых аналогично поведению традиционных МОП транзисторов, имеют структуру полупроводник-заглубленный окисел-полупроводник подложки, являющейся общим затвором всех подложечных транзисторов.

Для обеспечения работоспособности КМОП КНИ ИМС, исключения избыточного статического тока потребления подложечные N-канальные и P-канальные транзисторы должны находиться в закрытом состоянии. В общем случае закрытое состояние P-канальных подложечных транзисторов обеспечивается при условии, что сумма порогового напряжения подложечного P-канального транзистора (Vsp) и напряжения питания КМОП КНИ ИМС (Ucc) меньше напряжения на подложке КМОП КНИ ИМС (Ug), а закрытое состояние N-канальных подложечных транзисторов - при условии, что пороговое напряжение подложечного N-канального транзистора (Vsn) больше напряжения на подложке КМОП КНИ ИМС (Ug).

Иначе говоря, N-канальные и подложечные P-канальные транзисторы остаются закрытыми при условии, что

Подложечные транзисторы микросхем, изготовленных в соответствии с известным устройством, находятся в закрытом состоянии для значений Ucc=5.0 В и технологических параметров Vsp<-6 В, Vsn>0, при напряжении на подложке Ug=0 В.

КМОП КНИ ИМС привлекательны для применения в оборудовании, требующем стойкости к воздействию радиации, например в составе космических аппаратов. За время службы космического аппарата - обычно порядка 15 лет, микросхемы получают большую дозу радиационного облучения.

Воздействие радиации является причиной накопления в заглубленном окисле КНИ структуры положительного заряда, который приводит к уменьшению порогового напряжения подложечных транзисторов. При этом пороговое напряжение N-канального подложечного транзистора смещается в область отрицательных значений, что, как описано в статье [2], при достижении определенного уровня радиационного облучения приводит сначала к нарастанию потребляемого тока в микросхеме 1830ВЕ32У, а затем, из-за большого статического тока потребления, к отказу ее функционирования.

Кроме того, большой ток потребления микросхем в составе управляющих и вычислительных устройств космических аппаратов перегружает бортовой источник питания, мощность которого ограничена, что также является одной из причин отказа функционирования.

За счет повышенного статического тока потребления КМОП КНИ интегральные микросхемы конструкции, известной из источников [1, 2], даже при умеренном радиационном воздействии обладают узкой областью работоспособности и невысокой надежностью.

Наиболее близкой к заявляемому изобретению является интегральная микросхема, описанная в докладе Скотта А. Джексона и др. «Формирователь напряжения смещения подложки для КНИ системы-на-кристалле нескольких уровней напряжения питания» / Юго-западный Симпозиум по Аналого-Цифровому Проектированию. - 27 февраля 2000 года. - http://trs-new.jpl.nasa.gov/dspace/bitstream/2014/13864/1/00-0237.pdf. [3].

В докладе [3] раскрыта КМОП КНИ ИМС, образованная N-канальными и P-канальными транзисторами, с каждым из которых неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, имеет вывод питания, общий вывод и вывод подложки, сформированной слоем полупроводника КНИ структуры и являющейся общим затвором всех подложечных транзисторов. КМОП КНИ ИМС содержит СнК, образованную транзисторами названного типа, выполняющую функции преобразования и/или хранения информации, и источник положительного напряжения, в состав которого входят источник тока, усилитель положительного напряжения, N-канальный транзистор и генератор отрицательного напряжения, который включает формирователь тактовых импульсов и блок накачки заряда. Выход формирователя тактовых импульсов соединен с входом блока накачки заряда, выход которого является выходом генератора отрицательного напряжения.

Первый вывод источника тока соединен с выводом питания, а второй вывод источника тока соединен с первым входом усилителя положительного напряжения и со стоком N-канального транзистора, затвор которого соединен с его истоком и с выходом генератора отрицательного напряжения, второй вход усилителя положительного напряжения соединен с общим выводом КМОП КНИ ИМС, а его выход - с выводом подложки.

Устройство КМОП КНИ ИМС согласно [3] обеспечивает закрытое состояние подложечных P-канальных транзисторов, отрицательное пороговое напряжение которых по абсолютной величине ниже напряжения питания за счет подачи на подложку КМОП КНИ ИМС определенной величины положительного напряжения от источника положительного напряжения, выход которого соединен с подложкой КМОП КНИ ИМС.

При этом предотвращение открывания N-канальных подложечных транзисторов, положительное пороговое напряжение которых ниже напряжения питания, в известной КМОП КНИ ИМС обеспечивается путем ограничения величины положительного напряжения Ug, подаваемого на подложку от источника положительного напряжения, таким образом, чтобы по уровню тока 1 мкА значение Ug оставалось на 5 В ниже порогового напряжения N-канального подложечного транзистора Vsn, т.е. при условии, что

С этой целью в КМОП КНИ ИМС в схеме источника положительного напряжения, как показано в [3], используется генератор отрицательного напряжения, вырабатывающий напряжение минус 5 В, построенный традиционно для таких устройств с использованием формирователя тактовых импульсов и выходного блока на основе емкостной накачки заряда.

КМОП КНИ ИМС, реализованные согласно [3], обладают расширенной областью работоспособности и большей надежностью по сравнению с известными микросхемами [1, 2], однако - в применении только к высоковольтным КМОП КНИ ИМС, имеющим следующие типовые значения параметров: Vsp=-18 В; Vsn=28 В; Ucc=40 В. Согласно вышеуказанному условию работы (2) в этом случае значение напряжения на подложке Ug составляет 23 В.

Таким образом, известное устройство [3] в условиях воздействия радиации применимо для высоковольтных КМОП КНИ ИМС и может соответствовать условию работоспособности (2) только в случае отрицательного порогового напряжения P-канальных подложечных транзисторов, по абсолютной величине меньшего напряжения питания, и заведомо положительного порогового напряжения N-канальных подложечных транзисторов, по величине всегда меньшего, чем напряжение питания.

Известное из [3] устройство КМОП КНИ ИМС непригодно для использования в условиях воздействия радиации вне указанной области параметров и не обеспечивает работоспособности субмикронных КМОП КНИ ИМС, в которых пороговые напряжения P-канальных транзисторов могут находиться в диапазоне отрицательных значений, превосходящих по абсолютной величине напряжение питания; пороговые напряжения N-канальных транзисторов до воздействия радиации - в диапазоне как положительных, так и отрицательных значений, а после воздействия радиации - в области отрицательных значений.

Другим существенным недостатком устройства [3] является его неспособность минимизировать суммарный ток утечки и суммарный ток потребления КМОП КНИ СБИС (статический ток) до уровня, приемлемого для микросхем бортовой аппаратуры космических аппаратов, имеющих естественные ограничения по мощности бортовых источников питания.

Заявленное изобретение ориентировано на субмикронные КМОП КНИ ИМС и направлено на минимизацию статического тока потребления, расширение области работоспособности и повышение надежности субмикронной КМОП КНИ ИМС в условиях воздействия радиационного излучения.

Сущность изобретения

Заявляемое изобретение характеризуется тем, что в КМОП КНИ ИМС, образованной N-канальными и P-канальными КМОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, включающей систему-на-кристалле (СнК), выполняющую функции преобразования и/или хранения информации, и содержащей генератор отрицательного напряжения, включающий формирователь тактовых импульсов и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения, формирователь тактовых импульсов имеет первый и второй выходы противофазных тактовых импульсов, которые соединены с соответствующими входами противофазных тактовых импульсов блока накачки заряда, генератор отрицательного напряжения содержит блок управления и пороговое устройство, а формирователь тактовых импульсов имеет управляющий вход, управляющий вход реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от логического уровня напряжения на этом входе, блок управления содержит источник нормированного тока утечки подложечных P-канальных транзисторов и источник нормированного тока утечки подложечных N-канальных транзисторов, соединение которых в составе блока управления реализует функцию сравнения нормированных токов утечки подложечных P-канальных и N-канальных транзисторов и формирует результат сравнения в виде большего или меньшего уровня напряжения на выходе блока управления, выход блока управления соединен с входом порогового устройства, выход порогового устройства соединен с управляющим входом формирователя тактовых импульсов, выход генератора отрицательного напряжения соединен с выводом подложки.

В варианте реализации изобретения генератор отрицательного напряжения дополнительно имеет первый и второй внешние входы, реализующие внешнюю логику работы генератора отрицательного напряжения, в соответствии с которой при первой комбинации логических уровней напряжения на этих входах генератор отрицательного напряжения функционирует в соответствии с его внутренней логикой, определяемой уровнем напряжения на управляющем входе формирователя тактовых импульсов, при второй комбинации логических уровней напряжения на этих входах генератор отрицательного напряжения включен, при третьей - выключен.

В соответствии с изобретением формирователь тактовых импульсов построен на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов, у которых вход последующего элемента соединен с выходом предыдущего элемента, и имеет первый и второй выходы противофазных тактовых импульсов, один из инвертирующих элементов кольцевого генератора выполнен в виде элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента, первый вход элемента 2ИНЕ соединен с выходом предыдущего инвертирующего элемента кольцевого генератора, а второй вход элемента 2ИНЕ является управляющим входом формирователя тактовых импульсов, который реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от уровня напряжения на этом входе.

В варианте реализации изобретения формирователь тактовых импульсов, построенный на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов, у которых вход последующего элемента соединен с выходом предыдущего элемента, имеет первый и второй выходы противофазных тактовых импульсов, один из инвертирующих элементов кольцевого генератора выполнен в виде первого элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента кольцевого генератора, а первый вход соединен с выходом предыдущего инвертирующего элемента, формирователь тактовых импульсов включает второй, третий и четвертый логические элементы 2ИНЕ и дополнительный инвертирующий элемент, второй вход первого элемента 2ИНЕ соединен с выходом второго логического элемента 2ИНЕ, входы которого соединены с выходами третьего и четвертого логических элементов 2ИНЕ, первый вход третьего элемента 2ИНЕ является управляющим входом формирователя тактовых импульсов, который реализует внутреннюю логику функционирования генератора отрицательного напряжения, второй вход третьего элемента 2ИНЕ соединен с выходом дополнительного инвертирующего элемента, вход которого соединен с первым входом четвертого элемента 2ИНЕ и является вторым входом формирователя тактовых импульсов, второй вход четвертого элемента 2ИНЕ является третьим входом формирователя тактовых импульсов, второй и третий входы формирователя тактовых импульсов являются, соответственно, первым и вторым внешними входами генератора отрицательного напряжения.

В варианте реализации КМОП КНИ ИМС в соответствии с изобретением блок управления генератора отрицательного напряжения содержит P-канальный и N-канальный токозадающие транзисторы, N-канальный и P-канальный нагрузочные транзисторы, N-канальный и P-канальный выходные транзисторы, затвор и исток P-канального токозадающего транзистора соединены с источником питания, а его сток соединен с затвором и стоком N-канального нагрузочного транзистора и с затвором выходного N-канального транзистора, исток которого соединен с общим выводом, затвор и исток N-канального токозадающего транзистора соединены с общим выводом, а его сток соединен со стоком P-канального нагрузочного транзистора и с затвором выходного P-канального транзистора, исток которого соединен с выводом питания, стоки выходных P-канального и N-канального транзисторов объединены и образуют выход блока управления.

В варианте реализации изобретения блок управления генератора отрицательного напряжения в соответствии с изобретением содержит P-канальный и N-канальный токозадающие транзисторы, затвор и исток P-канального токозадающего транзистора соединены с источником питания, затвор и исток N-канального токозадающего транзистора соединены с общим выводом, стоки токозадающих P-канального и N-канального транзисторов объединены и образуют выход блока управления.

В соответствии с изобретением пороговое устройство в заявляемой КМОП КНИ ИМС выполнено на основе триггера Шмитта.

В варианте реализации изобретения блок накачки заряда может быть выполнен на основе двух идентичных каскадов емкостной накачки заряда, каждый из которых имеет первый и второй входы противофазных тактовых импульсов, положительный вывод и отрицательный вывод, образующие блок накачки заряда каскады соединены между собой последовательно таким образом, что отрицательный вывод предыдущего каскада соединен с положительным выводом последующего каскада, положительный вывод первого каскада соединен с общим выводом КМОП КНИ ИМС, отрицательный вывод последнего из каскадов соединен с выходом генератора отрицательного напряжения, одноименные входы противофазных тактовых импульсов образующих блок накачки заряда каскадов объединены и являются, соответственно, первым и вторым входом противофазных тактовых импульсов блока накачки заряда.

Краткое описание чертежей

Изобретение иллюстрируют следующие чертежи.

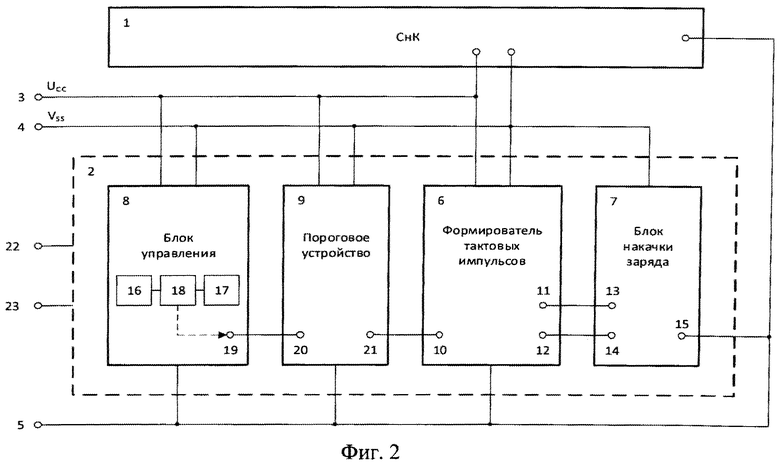

На Фиг.1 приведена структурная схема КМОП КНИ ИМС с системой-на-кристалле (СнК) и генератором отрицательного напряжения, содержащим формирователь тактовых импульсов, блок накачки заряда, блок управления, пороговое устройство.

На Фиг.2 приведена структурная схема КМОП КНИ ИМС в варианте реализации, согласно которому генератор отрицательного напряжения содержит два дополнительных внешних входа.

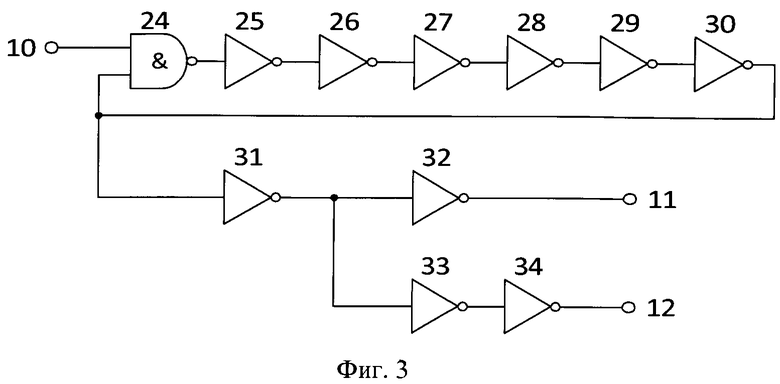

На Фиг.3 приведена схема формирователя тактовых импульсов в составе генератора отрицательного напряжения в КМОП КНИ ИМС в варианте реализации согласно Фиг.1.

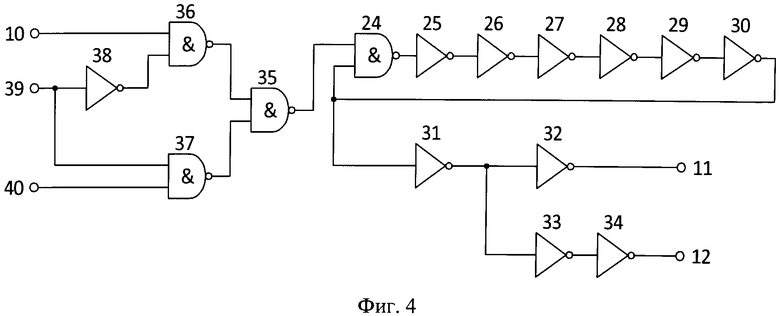

На Фиг.4 приведена схема формирователя тактовых импульсов в составе генератора отрицательного напряжения в КМОП КНИ ИМС в варианте реализации согласно Фиг.2

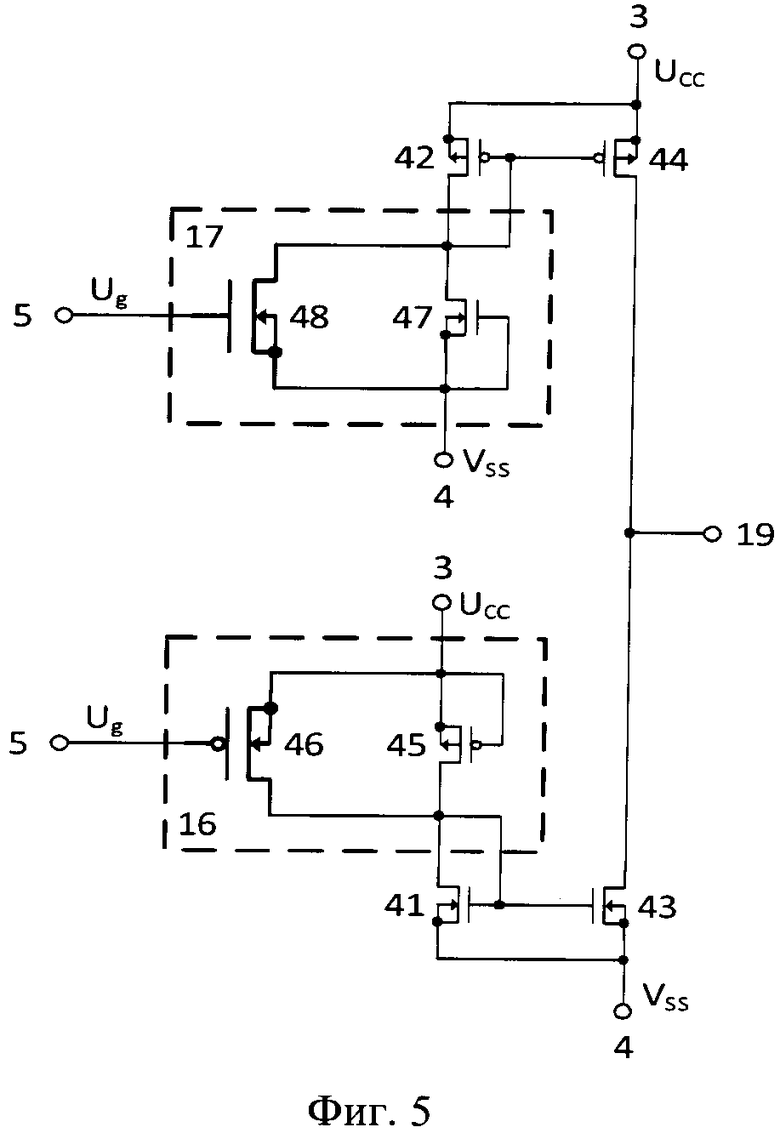

На Фиг.5 приведена схема блока управления в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

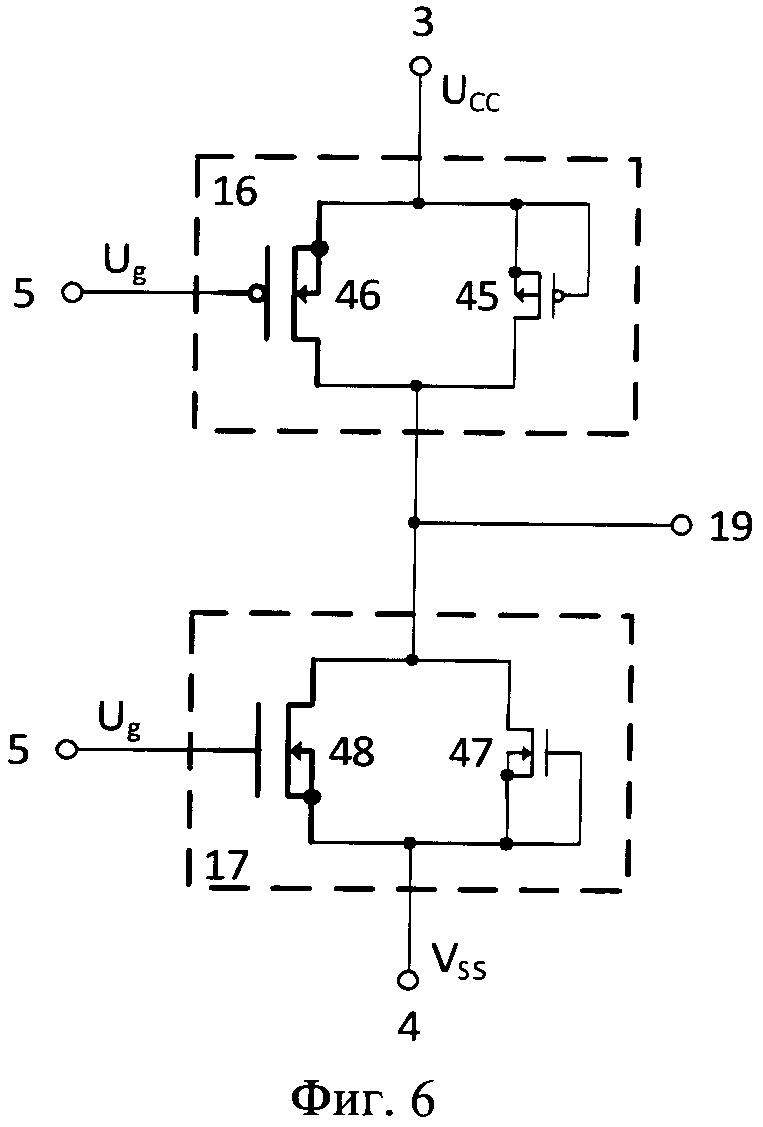

На Фиг.6 приведен вариант схемы блока управления в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

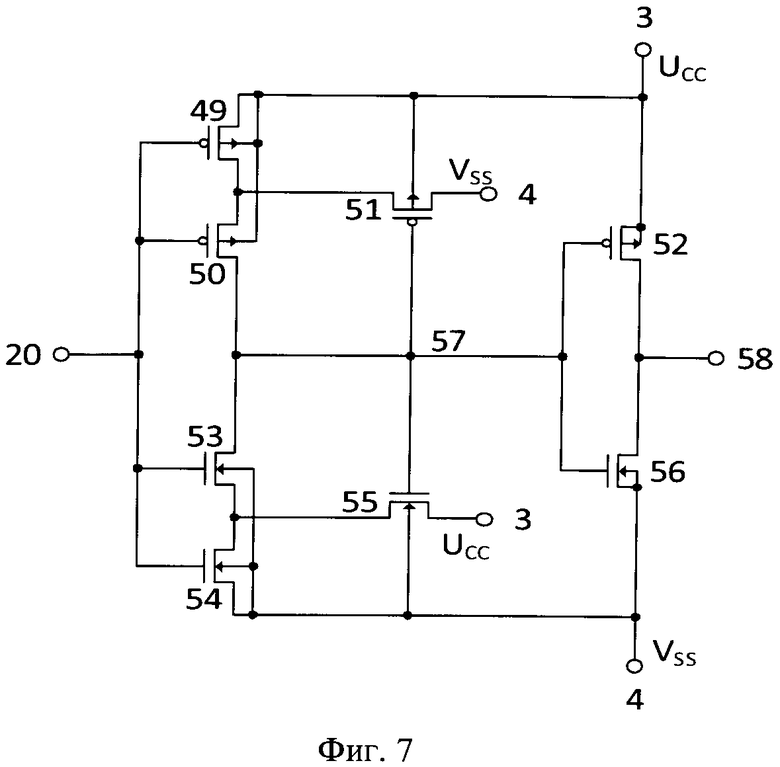

На Фиг.7 приведена схема порогового устройства на основе триггера Шмитта в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

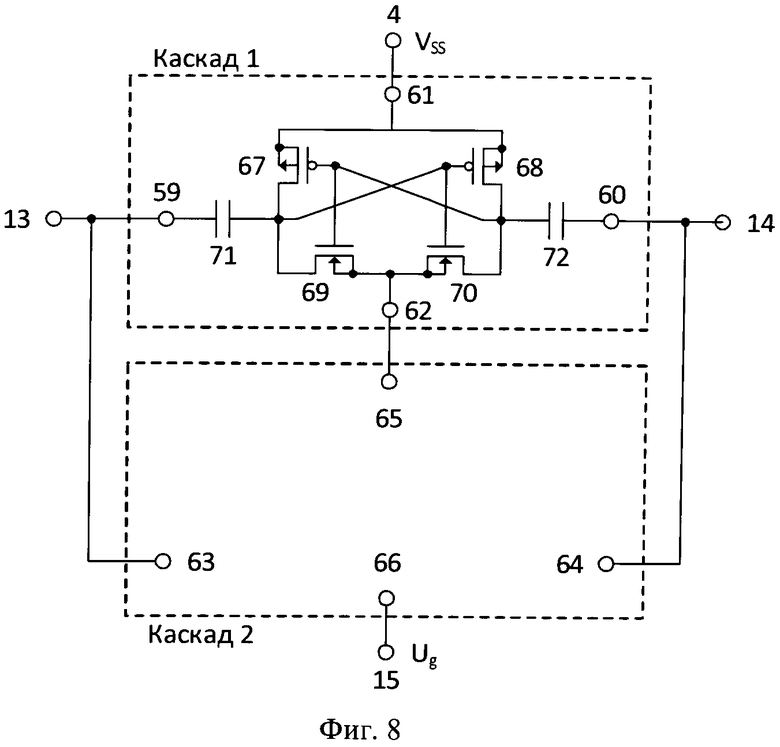

На Фиг.8 приведена схема блока накачки заряда в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

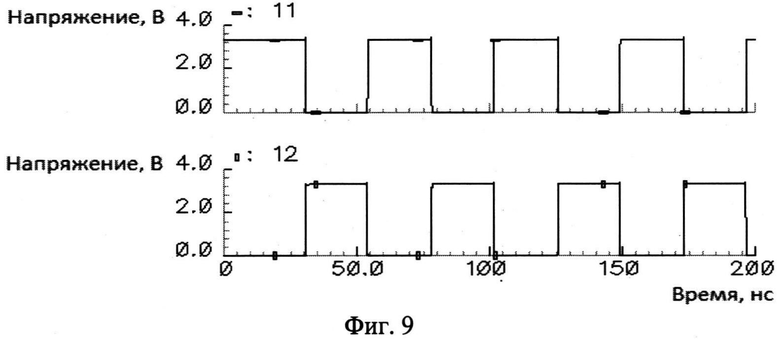

На Фиг.9 приведена временная диаграмма работы формирователя тактовых импульсов в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

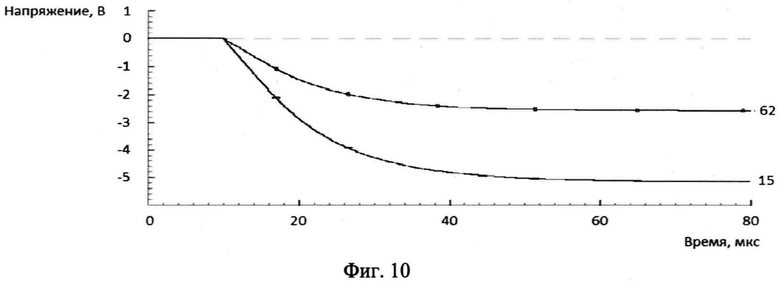

На Фиг.10 приведена временная диаграмма напряжения на выходе блока накачки заряда в составе генератора отрицательного напряжения в КМОП КНИ ИМС в соответствии с Фиг.1 и 2.

Осуществление изобретения

Интегральная микросхема в соответствии с изобретением изготавливается на КМОП транзисторах по технологии КНИ. Каждый из образующих заявляемую КМОП КНИ ИМС N-канальных и P-канальных КМОП транзисторов неотделимо связан областью стока, истока и тела транзистора с соответствующим подложечным транзистором, общим затвором всех подложечных транзисторов и одним из выводов КМОП КНИ ИМС является полупроводниковая подложка.

КМОП КНИ ИМС, показанная на структурной схеме Фиг.1, содержит систему-на-кристалле (СнК) 1, связанную с выводом питания и с общим выводом, выполняющую функции преобразования и/или хранения информации, и генератор отрицательного напряжения 2, подключенные к выводу питания 3, общему выводу 4 и выводу подложки 5. Генератор отрицательного напряжения включает формирователь тактовых импульсов 6, блок накачки заряда 7, блок управления 8 и пороговое устройство 9.

Формирователь тактовых импульсов имеет управляющий вход 10 и первый 11 и второй 12 выходы противофазных тактовых импульсов, соединенные с первым 13 и вторым 14 входами противофазных тактовых импульсов блока накачки заряда. Выход блока накачки заряда 15 является выходом генератора отрицательного напряжения.

Управляющий вход формирователя тактовых импульсов 10 реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от логического уровня напряжения на этом входе.

Блок управления 8 генератора отрицательного напряжения содержит источник нормированного тока утечки подложечных P-канальных транзисторов 16 и источник нормированного тока утечки подложечных N-канальных транзисторов 17, схема соединения 18 которых в составе блока управления реализует функцию сравнения нормированных токов утечки подложечных P-канальных и N-канальных транзисторов и формирует результат сравнения в виде большего или меньшего уровня напряжения на выходе 19 блока управления. Выход блока управления 19 соединен с входом 20 порогового устройства, выход 21 порогового устройства соединен с управляющим входом 10 формирователя тактовых импульсов, выход генератора отрицательного напряжения 15 соединен с выводом подложки 5.

В варианте реализации изобретения, показанном на Фиг.2, генератор отрицательного напряжения имеет первый 22 и второй 23 внешние входы, реализующие внешнюю логику работы, в соответствии с которой при первой комбинации логических уровней напряжения на указанных внешних входах генератор отрицательного напряжения функционирует в соответствии с его внутренней логикой, т.е. включает и выключает формирователь тактовых импульсов в зависимости от логического уровня напряжения на управляющем входе 10, при второй комбинации логических уровней напряжения на внешних входах 22 и 23 генератор отрицательного напряжения включен, при третьей комбинации на внешних входах 22 и 23 - генератор отрицательного напряжения выключен.

Формирователь тактовых импульсов 6, схема которого показана на Фиг.3, построен на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов 24, 25-30, вход последующего инвертирующего элемента соединен с выходом предыдущего инвертирующего элемента. Формирователь тактовых импульсов 5 имеет образованные инвертирующими элементами 31-34 первый 11 и второй 12 выходы противофазных тактовых импульсов, инвертирующий элемент 24 кольцевого генератора выполнен в виде элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента, первый вход элемента 2ИНЕ соединен с выходом предыдущего инвертирующего элемента кольцевого генератора, а второй вход элемента 2ИНЕ является управляющим входом 10 формирователя тактовых импульсов 6, реализующим внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от уровня напряжения на этом входе.

В варианте реализации изобретения, показанном на Фиг.4, формирователь тактовых импульсов построен на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов 24, 25-30, у которых вход последующего элемента соединен с выходом предыдущего элемента, имеет образованные инвертирующими элементами 31-34 первый 11 и второй 12 выходы противофазных тактовых импульсов, инвертирующий элемент 24 выполнен в виде первого элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента кольцевого генератора, а первый вход соединен с выходом предыдущего инвертирующего элемента. Формирователь тактовых импульсов включает второй 35, третий 36 и четвертый 37 логические элементы 2ИНЕ и дополнительный инвертирующий элемент 38, второй вход первого элемента 2ИНЕ 24 соединен с выходом второго логического элемента 2ИНЕ 35, входы которого соединены с выходами третьего 36 и четвертого 37 логических элементов 2ИНЕ, первый вход третьего элемента 2ИНЕ является управляющим входом формирователя тактовых импульсов 10, который реализует внутреннюю логику функционирования генератора отрицательного напряжения, второй вход третьего элемента 2ИНЕ соединен с выходом дополнительного инвертирующего элемента 38, вход которого соединен с первым входом четвертого элемента 2ИНЕ 37 и является вторым входом 39 формирователя тактовых импульсов, второй вход четвертого элемента 2ИНЕ является третьим входом 40 формирователя тактовых импульсов, второй 39 и третий 40 входы формирователя тактовых импульсов являются, соответственно, первым и вторым внешними входами 22 и 23 генератора отрицательного напряжения 2. Инвертирующие элементы в составе формирователей тактовых импульсов, приведенных на Фиг.3, Фиг.4, представляют собой любые известные элементы, реализующие функцию инверсии выхода относительно его входа, построенные по известным правилам (НЕ, ИНЕ и т.п.)

Логические состояния формирователя тактовых импульсов, выполненного по схеме Фиг.4, поясняет таблица истинности формирователя тактовых импульсов (Таблица 1):

Блок управления генератора отрицательного напряжения, показанный на схеме Фиг.5, содержит источник нормированного тока утечки подложечных P-канальных транзисторов 16, источник нормированного тока утечки подложечных N-канальных транзисторов 17 и элементы схемы соединения 18 источников нормированного тока утечки, включая N-канальный 41 и P-канальный 42 нагрузочные транзисторы, N-канальный 43 и P-канальный 44 выходные транзисторы.

Источник нормированного тока утечки подложечных P-канальных транзисторов 16 образуют P-канальный токозадающий транзистор 45 и неотделимо связанный с ним подложечный P-канальный транзистор 46, который и выполняет функцию источника нормированного тока утечки подложечных P-канальных транзисторов КМОП КНИ ИМС. Источник нормированного тока утечки подложечных N-канальных транзисторов 17 образуют N-канальный токозадающий транзистор 47 и неотделимо связанный с ним подложечный N-канальный транзистор 48, который и выполняет функцию источника нормированного тока утечки подложечных N-канальных транзисторов КМОП КНИ ИМС.

Затвор и исток P-канального токозадающего транзистора 45 соединены с источником питания 3, а его сток соединен с затвором и стоком N-канального нагрузочного транзистора 41 и с затвором выходного N-канального транзистора 43, исток которого соединен с общим выводом 4, затвор и исток N-канального токозадающего транзистора 47 соединены с общим выводом 4, а его сток соединен со стоком P-канального нагрузочного транзистора 42 и с затвором выходного P-канального транзистора 44, исток которого соединен с выводом питания 3, стоки выходных P-канального и N-канального транзисторов 43 и 44 объединены и образуют выход 19 блока управления.

Блок управления генератора отрицательного напряжения, показанный на схеме Фиг.6, в соответствии с вариантом реализации изобретения содержит источник нормированного тока утечки подложечных P-канальных транзисторов 16, источник нормированного тока утечки подложечных N-канальных транзисторов 17, которые соединены непосредственно. Источник нормированного тока утечки подложечных P-канальных транзисторов 16 образуют P-канальный токозадающий транзистор 45 и неотделимо связанный с ним подложечный P-канальный транзистор 46, который и выполняет функцию источника нормированного тока утечки подложечных P-канальных транзисторов КМОП КНИ ИМС. Источник нормированного тока утечки подложечных N-канальных транзисторов 17 образуют N-канальный токозадающий транзистор 47 и неотделимо связанный с ним подложечный N-канальный транзистор 48, который и выполняет функцию источника нормированного тока утечки подложечных N-канальных транзисторов КМОП КНИ ИМС. Затвор и исток P-канального токозадающего транзистора 45 соединены с источником питания 3, затвор и исток N-канального токозадающего транзистора 47 соединены с общим выводом 4, стоки P-канального токозадающего транзистора 45 и N-канального токозадающего транзистора 47 соединены и образуют выход 19 блока управления.

Пороговое устройство в заявляемой КМОП КНИ ИМС может быть выполнено на основе триггера Шмитта. В этом варианте, как показано на Фиг.7, пороговое устройство содержит первый 49, второй 50, третий 51 и четвертый 52 P-канальные транзисторы и пятый 53, шестой 54, седьмой 55 и восьмой 56 N-канальные транзисторы, затворы первого и второго P-канальных транзисторов 49 и 50 соединены с затворами пятого и шестого N-канальных транзисторов 53, 54 и образуют вход 20 порогового устройства, стоки транзисторов 49 и 51 соединены с истоком транзистора 50, истоки транзисторов 53 и 55 соединены со стоком транзистора 54, стоки транзисторов 50 и 53 объединены и соединены с затворами транзисторов 51, 52, 55 и 56, истоки транзисторов 49, 52 и 55 соединены с выводом питания 3, истоки транзисторов 51, 54 и 56 соединены с общим выводом 4, объединенные стоки транзисторов 52 и 56 образуют неинвертирующий выходной узел 58 порогового устройства, объединенные стоки транзисторов 50 и 53 образуют инвертирующий выходной узел 57 порогового устройства. Один из выходных узлов 57 или 58, в зависимости от варианта реализации - согласно Фиг.1 или Фиг.2, является выходом порогового устройства 21.

Блок накачки заряда генератора отрицательного напряжения заявляемой КМОП КНИ ИМС может содержать, как показано на Фиг.8, идентичные первый и второй каскады накачки заряда (каскад 1 и каскад 2). Каскад 1 (первый каскад) имеет первый 59 и второй 60 входы противофазных тактовых импульсов, положительный вывод 61 и отрицательный вывод 62. Каскад 2 (второй каскад) имеет первый 63 второй 64 входы противофазных тактовых импульсов, положительный вывод 65 и отрицательный вывод 66. Положительный вывод первого каскада 61 соединен с общим выводом 4 генератора отрицательного напряжения, отрицательный вывод 62 первого каскада соединен с положительным выводом 65 второго каскада, отрицательный вывод второго каскада 66 является выходом блока накачки заряда и, соответственно, выходом 15 генератора отрицательного напряжения. Первые входы 59 и 60 противофазных тактовых импульсов первого и второго каскадов объединены и являются первым 13 входом противофазных тактовых импульсов блока накачки заряда. Вторые входы 60 и 64 противофазных тактовых импульсов первого и второго каскадов объединены и являются вторым входом 14 противофазных тактовых импульсов блока накачки заряда. Каждый из каскадов накачки заряда содержит первый и второй P-канальные транзисторы 67 и 68, третий и четвертый N-канальные транзисторы 69 и 70, первый и второй конденсаторы накачки заряда 71 и 72. Сток транзистора 67 соединен со стоком транзистора 69, с затворами транзисторов 68 и 70 и первой обкладкой первого конденсатора накачки заряда 71, вторая обкладка которого является первым входом тактовых импульсов каскада накачки заряда 59 (63), сток транзистора 68 соединен со стоком транзистора 70, с затворами транзисторов 62 и 69 и с первой обкладкой второго конденсатора накачки заряда 72, вторая обкладка которого является вторым входом тактовых импульсов каскада накачки заряда 60 (64), объединенные истоки транзисторов 67 и 68 образуют положительный вывод 61 (65) каскада накачки заряда, объединенные истоки транзисторов 69 и 70 образуют отрицательный вывод 62 (66) каскада накачки заряда.

КМОП КНИ ИМС в соответствии с изобретением (Фиг.1) работает следующим образом.

При подаче на микросхему напряжения питания генератор отрицательного напряжения может находиться во включенном или выключенном состоянии, которое определяется наличием или отсутствием тактовых импульсов на выходах 11 и 12 формирователя тактовых импульсов (Фиг.3), обусловленным уровнем напряжения на управляющем входе 10 формирователя тактовых импульсов. При низком уровне напряжения на входе 10 формирователь тактовых импульсов не работает, генератор выключен, на его выходе состояние высокого импеданса.

Временные диаграммы Фиг.9, 10 работы формирователя тактовых импульсов 6 и блока накачки заряда 7 отражают работу генератора отрицательного напряжения 2 (Фиг.1) при установлении высокого уровня напряжения на управляющем входе 10.

При поступлении высокого уровня напряжения на управляющий вход 10 формирователя тактовых импульсов (Фиг.3) на его выходах 11 и 12 начинают вырабатываться противофазные тактовые импульсы (Фиг.9), которые поступают на первый 13 и второй 14 входы противофазных тактовых импульсов блока накачки заряда 7 (Фиг.1, Фиг.8). Формирование отрицательного уровня напряжения (Фиг.10) в каждом из двух каскадов блока накачки заряда (Фиг.8) осуществляется за счет передачи амплитуды среза тактового импульса через емкостной делитель, образованный конденсатором накачки заряда 71 (72) и паразитной емкостью нагрузки Сн, подключенной к первой обкладке конденсатора, образуемой суммарной емкостью затворов транзисторов 68 и 70 (67, 69) емкостью стоковых областей и емкостью сток-затвор транзисторов 67, 69 (68, 70). При этом напряжение Ug1 на выходе 62 первого каскада определяется выражением:

Ug1=Кс×Ut, где

Кс - коэффициент емкостной передачи напряжения,

Ut - амплитуда тактовых импульсов.

Кс=Св/(Св+Сн), где

Св - емкость конденсатора 71 (72),

Сн - паразитная емкость нагрузки.

При соответствующем выборе соотношения емкостей Св и Сн величина Кс может иметь типовое значение 0.9, соответственно, при амплитуде тактовых импульсов Ut, равной напряжению питания 3.3 В, величина напряжения на выходе первого каскада (Фиг.9) будет иметь значение около минус 3 В.

На выходе второго каскада относительно напряжения на его входе будет формироваться такое же отрицательное напряжение.

Соответственно, суммарное отрицательное напряжение Ug на выводе подложки (Фиг.9), формируемое двумя каскадами относительно общего вывода (напряжение на общем выводе Vss), будет иметь значение около минус 6 В.

Управление работой генератора отрицательного напряжения (Фиг.1) путем подачи разрешающего (высокого) или запрещающего (низкого) уровня напряжения на управляющий вход 10 формирователя тактовых импульсов осуществляется с помощью входящих в его состав блока управления 8 и порогового устройства 9 и обеспечивается следующим образом.

В блоке управления (Фиг.5) значения ширины канала N-канального 47 и P-канального 45 токозадающих транзисторов устанавливаются в одинаковой пропорции с шириной канала N-канальных и P-канальных транзисторов в КМОП КНИ ИМС в целом. Значение коэффициента пропорциональности может быть выбрано в диапазоне 0.005-0.001. При этом доля площади, занимаемая блоком управления, будет составлять незначительную (менее 1%) часть от общей площади всей КМОП КНИ ИМС. Токозадающие N-канальный 47 и P-канальный 45 транзисторы, затворы которых соединены с их истоками, всегда находятся в закрытом состоянии, а их собственные токи утечки на много порядков меньше токов утечки включенных параллельно с каждым из них подложечных транзисторов, соответственно 48 и 46 (Фиг.5). Проводимость каждого из подложечных транзисторов зависит от его геометрических параметров (ширины и длины канала, которые определяются соответствующим токозадающим транзистором), порогового напряжения и от напряжения на их общем затворе 5, которым является вывод подложки.

При подаче напряжения питания на КМОП КНИ ИМС и, соответственно, на блок управления в цепи транзисторов 48-42 и в цепи транзисторов 46-41 начинают протекать токи утечки подложечных транзисторов 48 и 46, которые сравниваются в цепи транзисторов 44-43, формируя на выходе 19 блока управления высокий или низкий уровень напряжения.

Если суммарный ток утечки подложечных N-канальных транзисторов КМОП КНИ ИМС меньше, чем ток утечки ее подложечных P-канальных транзисторов, то и в блоке управления ток утечки в цепи 48-42 N-канального подложечного транзистора будет меньше, чем ток утечки в цепи 46-41 P-канального подложечного транзистора, поэтому на выходе 19 блока управления будет установлен низкий уровень напряжения. С выхода 19 блока управления этот уровень напряжения поступает на вход 20 порогового устройства (Фиг.7). В этом варианте неинвертирующий выходной узел 58 порогового устройства используется в качестве выхода 21 порогового устройства и выход 21 порогового устройства является неинвертированным по отношению к его входу 20. Порог срабатывания по входу порогового устройства установлен на уровне напряжения, равном половине напряжения питания. Уровню сигнала на входе ниже половины напряжения питания (низкий уровень) соответствует на выходе порогового устройства логический ноль, уровню сигнала на входе выше половины напряжения питания (высокий уровень) соответствует на выходе 21 порогового устройства логическая единица.

Низкий уровень напряжения передается с входа порогового устройства 20 на его выход 21, с которого поступает на управляющий вход 10 формирователя тактовых импульсов, запрещая работу генератора отрицательного напряжения. На выводе подложки 5 поддерживается первоначальный (неотрицательный) уровень напряжения Ug.

Под воздействием радиации происходит сдвиг пороговых напряжений подложечных транзисторов в отрицательную область, приводя к уменьшению тока утечки P-канальных подложечных транзисторов и увеличению тока утечки N-канальных подложечных транзисторов. При достижении определенного уровня воздействия радиации ток подложечных N-канальных транзисторов окажется больше, чем ток подложечных P-канальных транзисторов. При этом на выходе 19 блока управления будет установлен уровень напряжения выше половины напряжения питания, что сформирует уровень логической единицы на выходе 21 порогового устройства, разрешающий включение формирователя тактовых импульсов, противофазные тактовые сигналы с выходов 11 и 12 которого начнут воздействовать на входы 13, 14 блока накачки заряда. С выхода блока накачки заряда генератора на подложке начнет формироваться отрицательный уровень напряжения, который при определенном его значении восстановит соотношение токов P-канальных и N-канальных подложечных транзисторов в сторону превышения тока подложечных P-канальных транзисторов над N-канальными. При этом на выходе 19 блока управления установится низкий уровень напряжения, который через пороговое устройство передастся на вход 10 формирователя тактовых импульсов, останавливая его работу и работу блока накачки заряда. На емкости подложки сохранится то значение отрицательного уровня напряжения, которое было достигнуто в предшествующий период работы генератора. Через некоторое время установившийся баланс токов подложечных транзисторов из-за частичного стекания отрицательного заряда с емкости подложки или за счет продолжающегося воздействия радиации будет снова сдвинут в сторону превышения тока подложечных N-канальных транзисторов над P-канальными. Выход блока управления перейдет в состояние высокого уровня, которое через пороговое устройство передастся на вход 10 формирователя тактовых импульсов. В результате включившийся генератор дополнительно уменьшит отрицательное напряжение на подложке и тем самым восстановит соотношение токов подложечных транзисторов на прежнем минимальном уровне. Соединение источников нормированного тока утечки подложечных P-канальных и N-канальных транзисторов 16 и 17 обеспечивает сравнение нормированных токов утечки этих транзисторов и формирование результата сравнения в виде большего или меньшего уровня напряжении на выходе блока управления.

Аналогично происходит управление работой генератора отрицательного напряжения в варианте использования блока управления, схема которого показана на Фиг.6. При подаче напряжения питания на КМОП КНИ ИМС и блок управления начинают протекать токи подложечных транзисторов 48 и 46, формируя на выходе 19 блока управления в зависимости от соотношения проводимостей этих транзисторов высокий или низкий уровень напряжения. Если проводимость N-канального подложечного транзистора 48 окажется меньше проводимости подложечного P-канального транзистора 46, на выходе блока управления 19 установится уровень напряжения, больше половины напряжения питания (высокий уровень напряжения).

С выхода 19 блока управления этот уровень напряжения поступает на вход 20 порогового устройства (Фиг.7). В этом варианте инвертирующий выходной узел 57 образует выход 21 порогового устройства, инвертированный по отношению к входу 20 порогового устройства. С выхода 21 установившийся на нем низкий уровень напряжения поступает на управляющий вход 10 формирователя тактовых импульсов, запрещая работу генератора отрицательного напряжения. На выводе подложки 5 поддерживается первоначальный (неотрицательный) уровень напряжения Ug. В остальном работа генератора отрицательного напряжения с блоком управления, приведенным на Фиг.6, аналогична описанному выше варианту с блоком управления, выполненным по схеме Фиг.5.

С возрастанием дозы радиации напряжение на подложке, при котором обеспечивается баланс токов P-канальных и N-канальных подложечных транзисторов, будет сдвигаться от начального уровня напряжения до максимального по абсолютной величине отрицательного напряжения, которое способен сформировать генератор, и может достигать значения минус 6 В, обеспечивая для каждого значения дозы радиации минимальный уровень суммарного тока утечки подложечных транзисторов КМОП КНИ ИМС.

Особенности работы КМОП КНИ ИМС, показанной на Фиг.2, заключаются в том, что в зависимости от логических уровней напряжения на дополнительных внешних входах 22 и 23 генератора отрицательного напряжения работа генератора осуществляется в трех разных режимах в зависимости от логического состояния формирователя тактовых импульсов, как показано выше в Таблице 1.

В первом режиме, при логическом уровне внешнего входного сигнала 22 генератора отрицательного напряжения, равном нулю, работа формирователя тактовых импульсов определяется уровнем сигнала на входе 10, поступающего с выхода 21 порогового устройства, и генератор отрицательного напряжения работает идентично тому, как это описано выше для КМОП КНИ ИМС согласно Фиг.1.

Во втором режиме, при логических уровнях внешних входных сигналов 22 и 23, равных единице, формирователь тактовых импульсов включен и генератор вырабатывает отрицательное напряжение независимо от сигнала с блока управления. Этот режим принудительного включения генератора отрицательного напряжения может быть использован при тестировании исправности генератора отрицательного напряжения в КМОП КНИ ИМС.

В третьем режиме, при комбинации внешних входных сигналов, согласно которой на входе 22 установлена логическая единица, а на входе 23 - логический ноль, формирователь тактовых сигналов и, соответственно, генератор отрицательного напряжения выключены. Этот режим принудительного выключения генератора может быть использован при испытаниях КМОП КНИ ИМС для исследования области работоспособности КМОП КНИ ИМС, в том числе в условиях воздействия радиации.

Реализация субмикронной КМОП КНИ ИМС в соответствии с изобретением позволяет повысить ее радиационную стойкость, расширить область ее работоспособности и повысить надежность в условиях воздействия радиационного излучения.

Заявляемое изобретение было реализовано и исследовано в условиях радиационного облучения в тестовой КМОП КНИ ИМС с минимальными размерами элементов 0.25 мкм при следующих параметрах:

Напряжение питания 3.0-4.0 В.

Количество транзисторов в тестовой КМОП КНИ ИМС - более 3 млн.

Результаты испытаний тестовых микросхем в двух разных режимах показаны в Таблице 2, где приняты следующие обозначения:

Iccs - статический ток, потребляемый микросхемой;

Iocc - динамический ток, потребляемый микросхемой при функционировании.

В микросхеме 1 генератор был принудительно выключен (на внешних входах 22 и 23 генератора были установлены единичный и нулевой логические уровни, как показано в Таблице 1), что соответствовало постоянному нулевому напряжению на подложке микросхемы (имитация отсутствия генератора отрицательного напряжения).

В микросхеме 2 генератор отрицательного напряжения согласно изобретению управлялся от блока управления (на внешних входах 22 и 23 генератора был установлен, как показано в Таблице 1, нулевой логический уровень), вырабатывая и подавая на подложку микросхемы увеличивающееся отрицательное напряжение по мере увеличения дозы облучения (в Таблице 2 доза облучения показана в относительных единицах).

Как видно из Таблицы 2, в микросхеме 2 с генератором отрицательного напряжения в соответствии с изобретением по мере увеличения дозы радиационного облучения на подложку подается вырабатываемое генератором отрицательного напряжения увеличивающееся по абсолютной величине отрицательное напряжение, благодаря чему минимизирован статический ток потребления во всем диапазоне радиационного воздействия, и микросхема сохраняет практически неизменными свои характеристики потребления тока - величина потребляемого статического тока Iccs во всем диапазоне воздействия радиации остается на уровне менее 0.5 мА.

В микросхеме 1, в которой генератор отрицательного напряжения отключен (сымитировано отсутствие генератора), на подложке поддерживается постоянный близкий к нулевому (20-50 мВ) уровень напряжения Ug, и по мере набора дозы облучения потребление статического тока увеличивается в 80 раз, достигая уровня 16, 82 мА, что в 35 раз превышает статический ток, потребляемый при этом же уровне облучения микросхемой 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ (ВАРИАНТЫ) | 2015 |

|

RU2601251C1 |

| СПОСОБ И СХЕМА УМЕНЬШЕНИЯ УТЕЧЕК И СТАБИЛИЗАЦИИ ПОРОГОВЫХ НАПРЯЖЕНИЙ МОП ТРАНЗИСТОРОВ В ИС | 2013 |

|

RU2520426C1 |

| Многоустойчивый КМОП-компаратор напряжения | 1988 |

|

SU1564722A1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| Частотнозадающий орган электронного прибора времени | 1989 |

|

SU1700534A1 |

| Кварцевый генератор | 1990 |

|

SU1762379A1 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| Способ изготовления высокотемпературных КМОП КНИ интегральных схем | 2016 |

|

RU2643938C1 |

Изобретение относится к субмикронным КМОП КНИ ИМС, действующим в условиях воздействия радиационного излучения. Усовершенствованная КМОП КНИ ИМС содержит систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и содержит генератор отрицательного напряжения, включающий последовательно соединенные блок управления, реализующий функцию сравнения нормированных токов утечки подложечных P-канальных и N-канальных транзисторов, пороговое устройство, формирователь тактовых импульсов и блок накачки заряда. Формирователь тактовых импульсов, имеющий управляющий вход, реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от логического уровня напряжения на этом входе. В варианте изобретения генератор отрицательного напряжения имеет первый и второй внешние входы, реализующие внешнюю логику функционирования генератора отрицательного напряжения, в соответствии с которой при первой комбинации логических уровней на этих входах генератор отрицательного напряжения функционирует в соответствии с его внутренней логикой, при второй комбинации логических уровней напряжения на этих входах генератор отрицательного напряжения включен, при третьей - выключен. Изобретение обеспечивает минимизацию статического тока потребления, расширение области работоспособности и повышенную радиационную стойкость. 7 з.п. ф-лы, 10 ил., 2 табл.

1. КМОП КНИ интегральная микросхема (КМОП КНИ ИМС), образованная N-канальными и P-канальными КМОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержащая систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, генератор отрицательного напряжения, включающий формирователь тактовых импульсов и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения, формирователь тактовых импульсов имеет первый и второй выходы противофазных тактовых импульсов, которые соединены с соответствующими входами противофазных тактовых импульсов блока накачки заряда, отличающаяся тем, что генератор отрицательного напряжения дополнительно содержит блок управления и пороговое устройство, а формирователь тактовых импульсов имеет управляющий вход, управляющий вход реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от логического уровня напряжения на этом входе, блок управления содержит источник нормированного тока утечки подложечных P-канальных транзисторов и источник нормированного тока утечки подложечных N-канальных транзисторов, соединение которых в составе блока управления реализует функцию сравнения нормированных токов утечки подложечных P-канальных и N-канальных транзисторов и формирует результат сравнения в виде большего или меньшего уровня напряжения на выходе блока управления, выход блока управления соединен с входом порогового устройства, выход порогового устройства соединен с управляющим входом формирователя тактовых импульсов, выход генератора отрицательного напряжения соединен с выводом подложки.

2. КМОП КНИ ИМС по п.1, отличающаяся тем, что генератор отрицательного напряжения имеет первый и второй внешние входы, реализующие внешнюю логику работы, в соответствии с которой при первой комбинации логических уровней напряжения на первом и втором внешних входах генератор отрицательного напряжения функционирует в соответствии с его внутренней логикой по п.1, при второй комбинации логических уровней напряжения на названных входах генератор отрицательного напряжения включен, при третьей комбинации на этих входах генератор отрицательного напряжения выключен.

3. КМОП КНИ ИМС по п.1, отличающаяся тем, что формирователь тактовых импульсов построен на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов, у которых вход последующего элемента соединен с выходом предыдущего элемента, и имеет первый и второй выходы противофазных тактовых импульсов, один из инвертирующих элементов кольцевого генератора выполнен в виде элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента, первый вход элемента 2ИНЕ соединен с выходом предыдущего инвертирующего элемента кольцевого генератора, а второй вход элемента 2ИНЕ является управляющим входом формирователя тактовых импульсов, который реализует внутреннюю логику функционирования генератора отрицательного напряжения путем включения и выключения формирователя тактовых импульсов в зависимости от уровня напряжения на этом входе.

4. КМОП КНИ ИМС по п.2, отличающаяся тем, что формирователь тактовых импульсов построен на основе кольцевого генератора, образованного последовательным соединением нечетного количества инвертирующих элементов, у которых вход последующего элемента соединен с выходом предыдущего элемента, имеет первый и второй выходы противофазных тактовых импульсов, один из инвертирующих элементов кольцевого генератора выполнен в виде первого элемента 2ИНЕ, выход которого соединен с входом последующего инвертирующего элемента кольцевого генератора, а первый вход соединен с выходом предыдущего инвертирующего элемента, формирователь тактовых импульсов включает второй, третий и четвертый логические элементы 2ИНЕ и дополнительный инвертирующий элемент, второй вход первого элемента 2ИНЕ соединен с выходом второго логического элемента 2ИНЕ, входы которого соединены с выходами третьего и четвертого логических элементов 2ИНЕ, первый вход третьего элемента 2ИНЕ является управляющим входом формирователя тактовых импульсов, который реализует внутреннюю логику функционирования генератора отрицательного напряжения, второй вход третьего элемента 2ИНЕ соединен с выходом дополнительного инвертирующего элемента, вход которого соединен с первым входом четвертого элемента 2ИНЕ и является вторым входом формирователя тактовых импульсов, второй вход четвертого элемента 2ИНЕ является третьим входом формирователя тактовых импульсов, второй и третий входы формирователя тактовых импульсов являются, соответственно, первым и вторым внешними входами генератора отрицательного напряжения.

5. КМОП КНИ ИМС по п.1 или 2, отличающаяся тем, что блок управления генератора отрицательного напряжения содержит P-канальный и N-канальный токозадающие транзисторы, N-канальный и P-канальный нагрузочные транзисторы, N-канальный и P-канальный выходные транзисторы, затвор и исток P-канального токозадающего транзистора соединены с источником питания, а его сток соединен с затвором и стоком N-канального нагрузочного транзистора и с затвором выходного N-канального транзистора, исток которого соединен с общим выводом, затвор и исток N-канального токозадающего транзистора соединены с общим выводом, а его сток соединен со стоком P-канального нагрузочного транзистора и с затвором выходного P-канального транзистора, исток которого соединен с выводом питания, стоки выходных P-канального и N-канального транзисторов объединены и образуют выход блока управления.

6. КМОП КНИ ИМС по п.1 или 2, отличающаяся тем, что блок управления генератора отрицательного напряжения содержит P-канальный и N-канальный токозадающие транзисторы, затвор и исток P-канального токозадающего транзистора соединены с источником питания, затвор и исток N-канального токозадающего транзистора соединены с общим выводом, стоки токозадающих P-канального и N-канального транзисторов объединены и образуют выход блока управления.

7. КМОП КНИ ИМС по п.1 или 2, отличающаяся тем, что пороговое устройство выполнено на основе триггера Шмитта.

8. КМОП КНИ ИМС по п.1 или 2, отличающаяся тем, что блок накачки заряда выполнен на основе двух идентичных каскадов емкостной накачки заряда, каждый из которых имеет первый и второй входы противофазных тактовых импульсов, положительный вывод и отрицательный вывод, образующие блок накачки заряда каскады соединены между собой последовательно таким образом, что отрицательный вывод предыдущего каскада соединен с положительным выводом последующего каскада, положительный вывод первого каскада соединен с общим выводом КМОП КНИ ИМС, отрицательный вывод последнего из каскадов соединен с выходом генератора отрицательного напряжения, одноименные входы противофазных тактовых импульсов образующих блок накачки заряда каскадов объединены и являются, соответственно, первым и вторым входами противофазных тактовых импульсов блока накачки заряда.

| СПОСОБ ОТБОРА СТОЙКИХ К ВОЗДЕЙСТВИЮ ПОЛНОЙ ПОГЛОЩЕННОЙ ДОЗЫ ИОНИЗИРУЮЩЕГО ИЗЛУЧЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР ТЕХНОЛОГИИ КМОП/КНД | 2011 |

|

RU2466417C1 |

| ТРАНЗИСТОР СО СТРУКТУРОЙ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК НА ПОДЛОЖКЕ КРЕМНИЙ НА ИЗОЛЯТОРЕ | 2011 |

|

RU2477904C1 |

| US 8530298 B2, 10.09.2013 | |||

| US 7524710 B2, 28.04.2009 | |||

| US 6531739 B2, 11.03.2003 | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 3862930 A, 28.01.1975 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Пространственный блок покрытия | 1978 |

|

SU727784A1 |

Авторы

Даты

2015-03-27—Публикация

2013-11-15—Подача