(5) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

1 .

Изобретение относится к радиотехнике и может быть использовано в системах передачи дискретной информации.

Известно устройство цикловой синхронизации, содержащее последовательно соединенные генератор тактовых импульсов, распределитель, первьй элемент И, интегратор и пороговый элемент, выход которого подключен к второму входу распределителя,сдвиговый регистр,выходы которого соединены с входами дешифратора и элемента равнозначности, а также nep-t вый блок сравнения, п.ервый накопитель и второй элемент И f 1J,

. .

Однако известное устройство обеспечивает малую помехоустойчивость, {так как не обеспечивает удержание синхронизма в условиях интенсивных помех.

Цель изобретения -повышение помехоустойчивости.

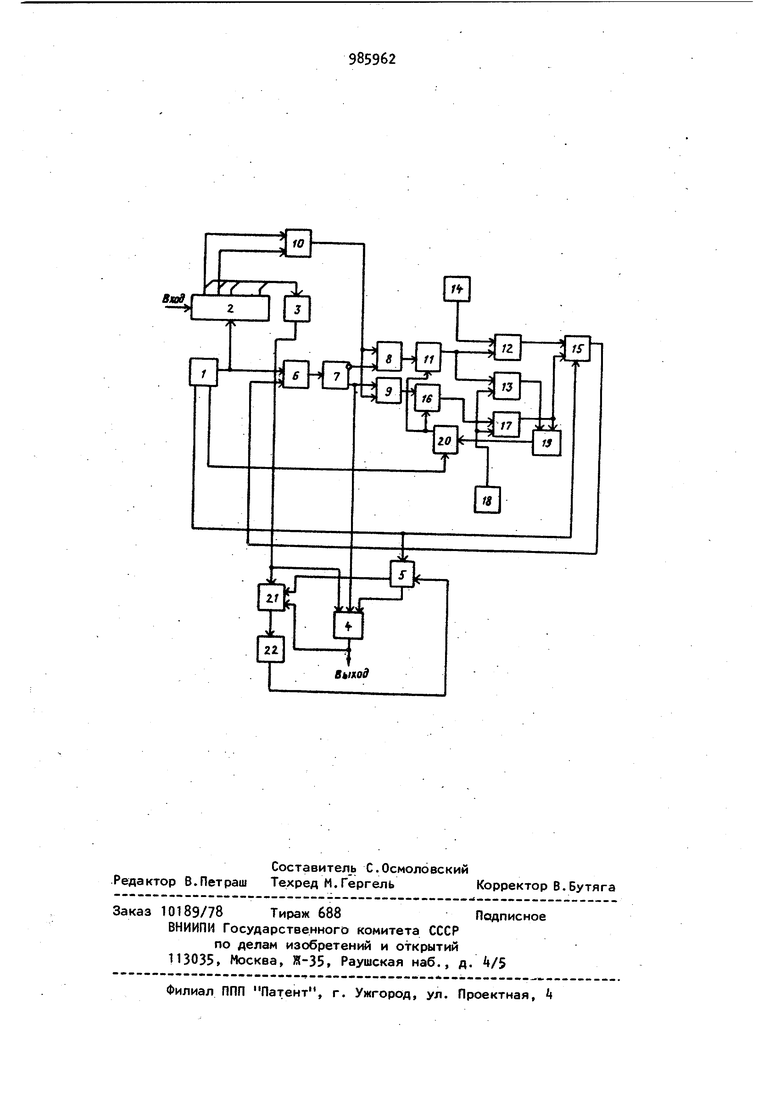

Для достижения поставленной цели в устройство цикловой синхронизации , содержащее последовательно соединенные генератор тактовых импульсов, распределитель, первый элемент И, интегратор и пороговый элемент,выход которого подключен к второму входу распределителя, сдвиговый регистр, выходы которого соединены с входами дешифратора и элемента равнозначности, а также первый блок сравнения, первый накопитель и второй элемент И, введены датчики верхнего и нижнего порога, два блока ,5 сравнения второй накопитель, три вентиля ИЛИ и триггер, при этом второй выход генератора тактовых импульсов подключён к входу сдвигового регистра и через первый элемент ИЛИ к счетному входу триггера, выходы которого подключены к первым входам первого и второго вентилей, к вторым входам которых подключен выход элемента равнозначности, а выходы указаиных вентилей подключены к входам соответствующих накопителей, выход первого накопителя подключен к первым входам первого и второго блоков сравнения, выход датчика нижнего порога подключен к второму входу первого блока сравнения, выход кото.рого через второй элемент И соединен с вторым входом первого элемента ИЛИ, выход датчика верхнего порога подключен к вторым входам второго и третьего блоков сравнения, к первому входу последнего подключен выход второго накопителя,выход третьего блока сравнения подключен к второму входу второго элемента И и к первому входу второго элемента ИЛИ, к второму входу кото: рого подключен выход второго блока сравнения, а выход второго элемента ИЛИ через третий вентиль, к второму |входу которого подключен третий выход генератора тактовых импульсов, подключены к вторым входам первого и второго накопителей, причем первый эход второго вентиля объединен с вто рым входом первого элемента И, к третьему входу которого подключен р.ыход дешифратора, подключенный к второму входу интегратора, третий вход которого соединен с вторым выходом распределителя, первый вход которого объединен с третьим входом второго элемента И, На чертеже представлена структурная схема устройства. Устройство цикловой синхронизации содержит генератор 1 тактовых импуль сов, сдвиговый фегистр 2, дешифратор 3, первый элемент И 4, распределитель 5, первый элемент ИЛИ 6, три гер 7, первый и второй вентили 8 и 9, элемент 10 равнозначности, первый накопитель 11, первый и второй блоки 12 и 13 сравнения, датчик k нижнего порога, второй элемент И 15, второй накопитель 16, третий блок 17 сравне ния,датчик 18 верхнего порога, второ элемент ИЛИ 19. третий вентиль 20, интегратор 21, пороговый элемент 22 Устройств.о работает следующим об разом. Синхропоследовательность двоичны символов О и 1.), закодированная за щитным кодом (символ О закодирован двумя элементами О 1 , а 1 Ю и искаженная помехами при передаче сигналов по каналу связи, накаплива ется в сдвиговом регистре 2, содержимое которого сдвигается в каждом такте под воздействием тактовых импульсов генератора 1 с одновременной записью в первый разряд очередного элемента кода. Сигналы с выхода всех разрядов сдвигового регистра 2 поступают на дешифратор 3, на выходе которого . формируется единичный логический сигнал в случае точного или приблизительного совпадения кода, накопленного в сдвиговом регистре 2 с защитным кодом синхропоследовательности. Одновременно сигналы с выходов первых двух разрядов сдвигового регистра 2 поступают на элемент 10 равнозначности, на выходе которого формируется единичный сигнал в случае равенства двух элементов защитного кода, поступивших на вход устройства последними. При поступлении на вход целого числа символов основного кода, соответствующего целому числу подциклов и четвертому числу элементов защитного кода, на выходе элемента 10.равнозначности формируется, как правило, нулевой сигнал, соотвэтствуодий неискаженным элементом одного последнего подцикла |ОЦ или , и только при искажении помехой одного из элементов защитного кода, что соответствует стиранию символа основного.кода OOj или|11 , на выходе элемента .10 равнозначности формируется единичный сигнал. Тактовые импульсы со второго выхода генератора 1 поступают также через первый элемент ИЛИ 6 на счетный вход триггера 7 При этом если эти такты соответствуют истинной фазе подцикла, т.е. моментам, когда ррошло целое число подциклов и в.сдвиговом регистре 2 записано целое число символов основного кода, то второй вентиль 9, открываемый в указанных тактах, пропускает сравнительно мало единичных сигналов от элемента 10 равнозначности на второй накопитель 16. А первый вентиль 8, открываемый сигналом с инверсного выхода триггера 7 пропускает сравнительно много единичных импульсов с элемента 10 равнозначности на первый накопитель 11. : В результате содержимое. первого накопителя 11 растет быстрее содержимого второго накопителя 16 и раньше достигает верхнего порога,-поступающего с датчика 18 на блоки 13 и 17 5 сравнения. При этом на входе второго блока 13 сравнения формируется единичный сигнал,который проходит через второй элемент ИЛИ 19 на третий вентиль 20 и совпадает с импульсом третьего выхода генератора 1 тактовы импульсов, который задержан относительно импульса первого выхода генератора 1 тактовых импульсов на время меньшее периода тактовых импульсов. В результате на выходе третьего вентиля 20 формируется сигнал, обнуляющий первый и второй накопители 11 и 16, после чего работа накопителей начи нается сначала изложенным выше способо Сигнал первого накопителя 11 поступает также на первый блок 12 сравнения, на выходе которого формируется единичный сигнал в случае, когда поступающий сигнал меньше нижнего порога; поступающего от датчика И нижнего порога. При высоком уровне помех, когда большое число символов основного кода оказывается стертым и содержимое второго накопи теля 16 растет достаточно быстро, она может достичь верхнего порога раньше, чем в первом накопителе 11. 1Если к этому моменту времени саде мое первого накопителя 11 все же превысило нижний порог, то е иничиый сигнал формируется на выходе третьего блока 17 сравнения и через второ элемент ИЛИ 19 и третий вентиль 20 обнуляет первый и второй накопители 11 и 16, после чего накопление начинается сначала. Если же содержимое второго накопителя 1& достигло верхнего порога, а содержимое первого накопителя 11 растет так медленно, что еще не до-. стигло нижнего порога, что наиболее вероятно при сбое подцикловой синхро низации, когда целому числу подциклов соответствует нулевой сигнал на прямом выходе тригпера 7, то единичные сигналы формируются сразу на двух первом и третьем блоках 12 и 17 сравнения. При этом на выходе второго элемента И 15 формируется импульс, совпадающий по времени с импульсом первого выхода генератора 1 тактовых импульсов, который занимает промежуточное положение между I импульсами первого и третьего выходов. Импульс с выхода второго элемента И 15 проходит через первый элемент ИЛИ 6 и поступает на вход триггера 7, изменяя его состояние 62 противоположное, вследствие чего на корректируется фаза подцикла и устраняется сбой подцикловой синхронизации, Вместе с тем сигнал с третьего блока 17 сравнения через элемент ИЛИ 19 и третий вентиль 20 обнуляет первый и второй накопители 11 и 16, после чего их работа начинается сначала. Сигнал о наличии синхронизма на выходе первого элемента И k, который является выходом устройства, формируется только при условии расхождения распределителя 5 (импульсов в состоянии истинной фазы, наличия сигнала совпадения на выходе дешифратора 3 и нахождения триггера 7 в состоянии истинной фазы подцикловой синхронизации. Одновременно сигнал с выхода первого элемента И k обнуляет интегратор 21. При отсутствии синхронизма в ячейках интегратора 21, количество которых равно числу состояний распределителя 5 (импульсов), накапливается сигнал дешифратора 3, соответствующий различным состояниям распределителя 5 ( импульсов). В случае, если в одной из ячеек интегратора 21 содержимое превысит заданный порог, то на выходе порогового элемента 22 формируется сигнал, устанавливащий распределитель 5 {импульсов в состояние истинной фазы. Устройство цикловой синхронизации обеспечивает повышение помехоустойчивости при кодировании синхропоследовательности защитнь 1 кодой и высоком уровне помех, так как при высоком уровне помех для поддержания устойчивого синхронизма дешифратор 3 настраивается на приблизительное совпадение с синхропоследовательностью, а такое приблизительное совпадение может возникнуть в нежелательные моменты времени при сдвиге кода синхропоследовательности на дробное число подциклов, при большом количестве стираний символов синхропоследовательности, в результате чего возникает возможность поддержания состояния /южного синхронизма,кото- . рую устраняет использование третьего входа у первого элемента И 4 и под- ключение к нему сигнала подцикловой синхронизации от триггера 7. Формула изобретения Устройство цикловой синхронизации, одержащее последовательно соединен9ные генератор тактовых импульсов, распределитель, первый элемент И, интрегратор и пороговый элемент, выход которого подключен к второму входу распределителя, сдвиговый регистр, выходЪ которого соединены с входами дешифратора и элемента равнознамности, а также пер.вый блок сравнения, первый на1 опитель и второй элемент И, о тличающееся тем, что, с целью повышения помехоустойчивости, в него введены датчики верхнего и нижнего порога, два блока сравнения, второй накопитель, три вентиля, два элемента ИЛИ и триггер, при этом вто рой выход генератора тактовых импуль сов подключенК входу сдвигового регистра и через первый элемент ИЛИ к счетному входу триггера, выходы которого подключены к первым входам первого и второго вентилей, к вторым входам которых подключен выход элемента равнозначности, а выходы указанных вентилей подключены к входам соответствующих накопителей, выход первого накопителя подключен к первым входам первого и второго блоков сравнения, выход датчика нижнего порога подключен к второму входу первого блока сравнения, выход которого через второй элемент И соеди28нен с вторым входом первого элемента ИЛИ, выход датчика верхнего порога подключён к вторым входам второго итретьего блоков сравнения, к перво У входу последнего подключен выход второго накопителя, выход третьего блока сравнения подключен к второму входу второго элемента И и к первому входу второго элемента ИЛИ, к второму входу которого подключен выход второго блока сравнения, а выход второго элемента ИЛИ через третий вентиль, к второму входу которого подключен третий выход генератора тактовых импульсов, подключен к вторым входам первого и второго накопителей, причем первый вход второго вентиля объединен с вторым входом первого элемента И, к третьему входу которого подключен выход дешифратора, подключенный к второму Тходу интеграто|5а, третий вход которого соединен с вторым выходом распределителя,, первый вход которого объединен с третьим входом второго элемента И, Источники информации, принятые во.внимание при экспертизе 1, Авторское свидетельство СССР , кл. Н 0 L 7/08, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| Устройство для выделения маркера кадровой синхронизации | 1989 |

|

SU1663775A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для формирования циклического синхроимпульса | 1989 |

|

SU1725404A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

Авторы

Даты

1982-12-30—Публикация

1981-06-23—Подача