1

Устройство цикловой синхронизации от.носится к радиотехнике и может использоваться в системах передачи информационных сигналов.

Известно устройство цикловой синхронизашш, содержащее дешифратор, на который подан синхросигнал и счетчик, связанный через ключ с генератором такто - вых импульсов и подключенный к входу распределителя, фазовые выходы которого подключены к соответствующим накопителям, а выходы последних - к решающему блоку, управляющему ключом и порогом накопителей. В данном устройстве синхро- j сигнал расшифровывается в дешифраторе . и открывает ключ, через который тактовые импульсы проходят на счетчик, а с него - на распределитель импульсов. При этом со второго выхода деши4 атора им- 20 пульсы поступают на входы всех накопителей, с фазами которых они совпадают. При достижении содержимым одного из накопителей заданного порога, его фаза

принимается решающим блоком за истинную. А состояние других накопителей говорит о состоянии канала, в зависимости от которого решающий блок изменяет пороги накопителей; что позволяет повысить достоверность фазы цикловой сишьронизашш Cl.

Недостатком известного устройства является невысокая вероятность удержагния синхронизма в условиях интенсивных псыех, обусловленная одинаковыми условиями работы всех накопителей независ1 МО от положения фазы цикловой синхро низашш.

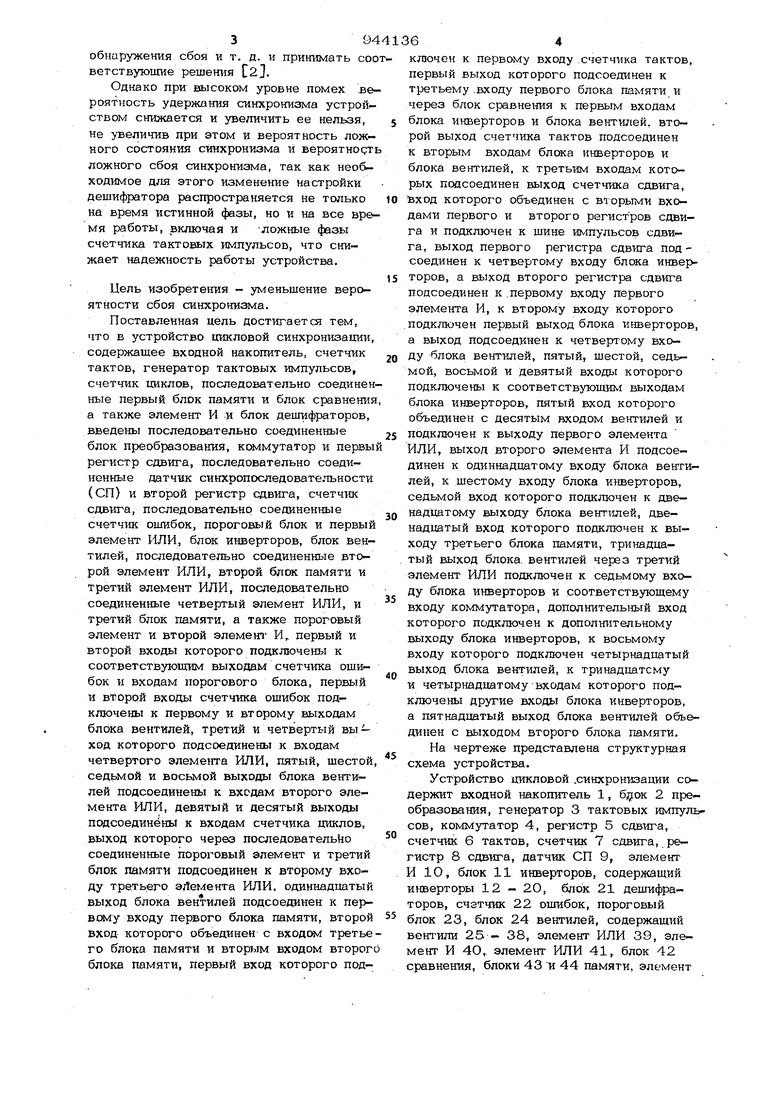

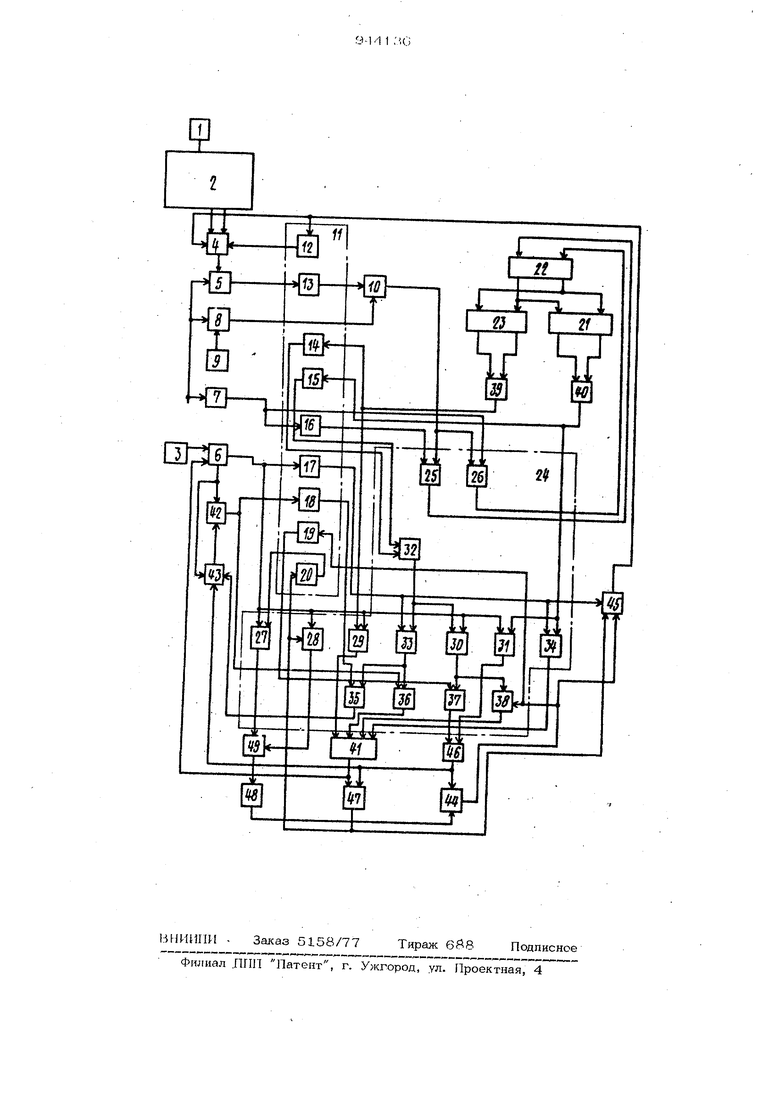

Известно устройство шпсповой синхронизации, содержащее входной накопитель, счетчик тактов, генератор тактовых импульсов, счетчик циклов, тгоследовательно соединенные первый блок памяти и блок сравнения, а также элемент И и блок деши4 трров. Данное устройство может распознавать состояние наличия синхронизма, сбоя синхронизма, ложного об}шружения сбоя и т, д. и принимать соо ветствующие решения C2j. Однако при высоком уровне помех вероятность удержа тта синхронизма устройством снижается и увеличить ее нельзя, не -величив при этом и вероятность ложного состояния синхронизма и вероятност ложного сбоя синхронизма, так как необходимое для этого изменение настройки дешифратора распространяется не только на время истинной фазы, но и на все время работы, включая и ложные фазы счетчика тактовых импульсов, что снижает надежность работы устройства. Цель изобретения - уменьшение вероятности сбоя синхронизма. Поставленная цель достигается тем, что в устройство цикловой синхронизации, содержащее входной накопитель, счетчик тактов, генератор тактовых импульсов, счетчик циклов, последовательно соединен ные первый блок памяти и блок сравнения а также элемент И и блок дешифраторов, введены последовательно соединенные блок преобразования, ксммутатор и первы регистр сдвига, последовательно соединенные датчик синхропоследовательности (СП) и второй регистр сдвига, счетчик сдвига, последовательно соединенные счетчик ошибок, пороговый блок и первый элемент ИЛИ, блок инверторов, блок вентилей, последовательно соединенные второй элемент ИЛИ, второй блок памяти и третий элемент ИЛИ, последовательно соединенные четвертый элемент ИЛИ, и третий блок памяти, а также пороговый элемент и второй элемент И„ первый и второй входы которого подключены к соответствующим выходам счетчика ошибок и входам порогового блока, первый и второй входы счетчика ошибок подключены к первому и второму выходам блока вентилей, третий и четвертый вы ход которого подсоединены к входам четвертого элемента ИЛИ, пятый, шестой седьмой и восьмой выходы блока вентилей подсоединены к входам второго элемента ИЛИ, девятый и десятый выходы подсоединены к входам счетчика циклов, выход которого через последовательно соединенные пороговый элемент и третий блок памяти подсоединен к второму входу третьего элемента ИЛИ, одиннадцатый выход блока вентилей подсоединен к первсяму входу первого блока памяти, второй вход которого объединен с входом третье го блока памяти и вторым входом второг блока памяти, первый вход которого подключен к первому входу счетчика тактов, первый выход которого подсоединен к третьему .входу первого блока памяти и через блок сравнения к первым входам блока инверторов и блока вентилей, второй выход счетчика тактов подсоединен к вторым входам блока инверторов и блока вентилей, к третьим входам которых подсоединен выход счетчика сдвига. Вход которого объединен с вторыми входами первого и второго регистров сдвига и подключен к шине импульсов сдвига, выход первого регистра сдвига подсоединен к четвертому входу блока инверторов, а выход второго регистра сдвига подсоединен к.первому входу первого элемента И, к второму входу которого подк7почен первый выход блока Т1нверторов, а выход подсоединен к четверт-ому входу блока вентилей, пятый, шестой, седьмой, восьмой и девятый входы которого подключены к соответствующим выходам блока инверторов, пятый вход которого объединен с десятым входом вентилей и подключен к выходу первого элемента ИЛИ, выход второго элемента И подсоединен к одиннадцатому входу блока вентилей, к шестому входу блока инверторов, седьмой вход которого подключен к двенадцатому выходу блока вентютей, двенадцатый вход которого подключен к выходу третьего блока памяти, тринадцатый выход блока, вентилей через третий элемент ИЛИ подключен к седьмому входу блока инверторов и соответствующему входу коммутатора, дополнительный вход которого подключен к дополнительному выходу блока инверторов, к восьмому входу которого подключен четырнадцатый выход блока вентилей, к тринадцатому и четырнадцатому-входам которого подключены другие входы блока инверторов, а пятнадцатый выход блока вентилей объединен с выходом второго блока памяти, На чертеже представлена структурная схема устройства. Устройство цикловой .синхронизации содержит входной накопитель 1, 2 преобразования, генератор 3 тактовых импульсов, коммутатор 4, регистр 5 сдвига, счетчик 6 тактов, счетчик 7 сдвига, регистр 8 сдвига, датчик СП 9, элемент И 10, блок 11 инверторов, содержащий инверторы 12 - 20, блок 21 дешифраторов, счэтчик 22 ошибок, пороговый блок 23, блок 24 вентилей, содержащий вентили 25 - 38, элемент ИЛИ 39, элемент И 40, элемент ИЛИ 41, блок 42 сравнения, блоки 43 и 44 памяти, элемент 594 ИЛИ 45, элемент ИЛИ 46, блок 47 памя ти, пороговый элемент 48 и счетчмк 49 1ГИКЛОВ. Устройство цикловой синхронизашга работает следу1ощ 1М образом. Принимаемый сигнал синхропоследовательности накапливается во входном накопителе 1 по одному разряду в каждом такте. Синхропоследовательность представляет собой Vi - разрядный двоичный код (основной), каждый разряд которого О или 1 закодирован двумя разрядами защитного кода, соответственно О или Ю. Во входном накопителе 1-содержится 2-VI принятых последними разрядов защитного кода. Вследствие воздей ствия помех в канале связи часть разрядов оказывается искаженной, при этом элемент основного кода вместо вида 10 или О1 имеет вид ОО или 11, что называется стиранием элемента основного кода. Из входного накопителя 1 сигнал поступает в блок 2. В блоке 2 преобразования все стирания преобразуются к виду ОО и к виду 11. В каждом такте коммутатор 4 пропускает сигнал блока 2 при нулевом сигнале на выходе элемента ИЛИ 45, что возникает в такте, соответствующем фазе цикловой синхронизации, когда на выходе счетчика 6 тактов формируется единичный цикловый сигнал, при условии, что в предыдущем цикле не было сбоя и блок памя ти 47 находится в нулевом состоянии, и не включен режим жесткой синхронизашга (блок 44 памяти находится в нулевом состоянии). Во всех остальных случаях через коммутатор 4 проходит нулевой сигнал блока 2. Сигналы блока 2 после коммутатора 4 поступают в регистр сдви га 5. Одновременно в регистр сдвига 8 записьтается сигнал СП от датчика СП 9 Далее на управляющие входы регистров сдвига 5 и 8 и счетный вход счетчика 7 сдвигов поступает 2 -vi .импульсов сдвига. При этом Б случае , если в разряде эталонной СП стоит единица, а в соответствующем разряде принятого сигнала ноль, то на выходе элемента И 10 формть руется сигнал ошибок, который через вентиль 25 проходит в счетчик ошибок 22 н на нулевых позициях СП при нулевом зна чении младщего разряда счетчика 7, а при единичном значении младшего разряда счетчика 7 - проходит через вентиль 26 в счетчик ошибок 22 на единичных позициях СП. Таким образом, после прохождения 2-И импульсов сдвига в счет- 66 чике 22 накаштивается число ошибок при нулевых и единичных позициях СП соответственно. Далее сигналы со счетчика 22 поступают на пороговый блок 23 и блок 21 дешифраторов, в результате чего на выходе элемента И 4О формируется единичный С11гнал при полном отсутствии ошибок, а на выходе элемента ИЛИ 39 формируется единичный сигнал в случае, еоmi число ошибок в счетчике 22 превышает заданный порог. Счетчик тактов 6 имеет коэффициент пересчета, равный числу тактов в цикле, и при счете импульсов генератора 3 один раз за цикл вырабатывает единичный цикловый сигнал, соответствующий истинной фазе цикловой синхронизации, который в течение соответствующего такта открывает вентили 27 - 31. При этом, в случае полного отсутствия ошибок, единичный сигнал с элемента И 4О про.ходит через вентиль 31, элемент ИЛИ 46 I и устанавливает или подтверждает нуле вое состояние блоков 43 и 44 памяти и блока 47 памяти, выходной сигнал которого проходит через инвертор 2О, вентиль 27 и устанавливает в нулевое состояние счетчик 49 циклов со сбоем синхронизации. То же самое происходит в случае, если на выходе элемента И 40 - нулевой сигнал, и на выходе элемента ИЛИ 39 сфорктрован нулевой сигнал, свидетельствующий о малом количестве ошибок, который через инвертор 14, вентили 32, 30 и вентильь 34, открытый при килевом состоянии блока 44 памяти, проходит на второй вход элемента ИЛИ 46. Этим подтверждается наличие синхронизЛии. Если же в этом такте на выходе элемента ИЛИ 39 формируется единичный сигнал, что свидетельствует о превыщетга допустимого количества ошибок, то этот сигнал проходит через вентиль 29, элемент ИЛИ 41 и устанавливает блок 47 памяти в еди{шчное состояние и, воздействуя на установочный вход счетчика 6 тактов подтверждает его установку в состояние, соответствующее истинной фазе синхронизации. Сигнал сбоя с выхода блока 47 памяти поступает на вентиль 28, через который шпсловый сигнал проходит на счетчик 49 циклов со сбоем синхронизации. Одновременно сигнал сбоя поступает с блока 47 памяти ш элемент ИЛИ 45 и далее на первый вход коммутатора 4, в результате чего в следующем цикле в регистр 5 сдвига проходит сигнал с блока 2 преобрааоваПИЯ, что приводит к выявлению большего количества ошибок. Следует отметить, что если блок 47 памяти находится длительное время в состоянии сбоя (единичном состоянии), то каждый цикловый импульс проходит со счетчика 6 тактов через вентиль 28 на счетчик 49 циклов. При достижении в счетчике 49 циклов заданного порога на выходе порогового элемента 48 формируется сигнал, который устанавпивает блок 44 памяти в единичное состояние. При этом независимо от номера такта на выходе элемента ИЛИ 45 присутствуе единичный стагнал и через коммутатор 4 проходит сигнал от блока 2 преобразования, что приводит к выявлению большего количества ошибок, и, кроме того, сброс блока 47 памяти, свидетельствующий о восстановлении синхронизации, может про изойти только при безошибочном совпадении принимаемой СП с эталонной СП, ког да в такт соотвегствукицем истинной фазе цикловой синхронизашш, на выходе элемента И 4О фор«гаруется единичный сигнал, проходящий через вентиль 31 и элемент ИЛИ 46 на блсж 47 памяти. Сигнал с выхода вентиля 32, свидетельст вующий о небольшом количестве ошибок, не проходит через закрытый вентиль 34 на нулевой вход блока 47 памяти, а проходит в такте, соответствующем истинной фазе синхронизации, через открытый вентиль 38, элемент ИЛИ 41 и подтверж дает состояние сбоя в блсже 47 памяти. В случае, еащ устройство фиксирует совпадение принятой СП и эталонной СП в такте, номер которого не соответствует истинной синхронизации, в открытом состоянии Находятся вентили 33 и 34, Поэтому, если количество ошибок равно нулю, то e шничный сигнал с выхода элемента И 4О проходит.через вентиль 34. элемент ИЛИ 41, устанавливает блок 47 памяти в единичное состояние и, воздействуя на установочный вход, устанавливает счетчик 6 тактов в состояние, соответсгвуюшее истинной фазе цикловой синхронизации, т, е. корректирует фазу синхронизации. Если же произошло совпадение С7Г с небольшим допустимым количеством ошибок, то единичный сигнал с выхода вентиля 32 проходит через вентиль 33 на входы вентилей 35 и 36, которые управляются выходным сигналом блока 42 сравнения, В исходном состоя1 НИИ на выходе блока 42 сравнения сформирован нулевой сигнал,который через инвертор 18 открывает вентиль 35 и сигнал с выхода вентшш 35 поступает на вход записи блока 43 памяти. При этом номер такта, в котором произошло совпадение С с небольшим количеством ошибок с информационного выхода счетчика тактов 6 записывается в блок 43 памяти. Сигнал о записанном номере во всех последующих тактах поступает с блока 43 памяти на блок 42 сравнения, на другой вход которого поступает сигнал о номере со счетчика тактов 6. Если в дальнейшем совпадение С/ с небольшим допустимым количеством ошибок произойдет в та,кте, номер которого совпадает с номером, записанным в блоке 43 памяти, то вследствие наличия в этом такте единичного сигнала на выходе блока 42 сравнения сигнал с вентиля 33 проходит через открытый вентиль 36, элемент ИЛИ 41 и устанавливает блок 47 памяти в единичное состояние и счетчик тактов 6 в состояние истинной фазы цикловой синхронизации, т. е. про исходит корректировка фазы цикла. Следует отметить, что блок 43 памяти хранит записанный номер такта только до момента возникновения первого сигнала, подтверждающего наличие синхронизма, так как в этом, случае сигнал с выхода элемента ИЛИ 46 сбрасывает блок 43 памяти в исходное состояние. Эффективность предлагаемого устройства особенно высока в условиях воздействия интенсивных помех и при резком изменении состояния канала связи. Формула изобретения Устройство цикловой синхронизации, содержащее входной накопитель, счетчик тактов, генератор тактовых импульсов, счетчик циклов, последовательно соединенные первый блок памяти и блок сравнения, а также элемент И и блок дешифраторов, отличающееся тем, что, с целью уменьшения вероятности сбоя синхронизма, введены последовательно соединенные блок преобразования, коммутатор и первый регистр сдвига, последовательно соединенные датчик синхропоследовательности (СП) и второй регистр сдвига, счетчик сдвига, последовательно соединенные счетчик ошибок, пороговый блок и первый элемент ИЛИ, блок инверторов, блок вентилей, последовательно соединенные второй элемент ИЛИ, второй блок памяти и третий элемент ИЛИ, последовательно соединенные четвертый элемент ИЛИ и третий блок памяти, а также по- роговый элемент и второй элемент И, первый и второй входы которого подключень . к соответствующим выходам счетчика ошн- j бок и входам порогового блока, первый к второй входы счетчика ошибок подключены к первому и второму выходам блока вентилей, третий и четвертый ёыход которого подсоединены к входам четвертого эле- Ю мента ИЛИ, пятый, шестой, седьмой и восьмой выходы блока вентилей подсоединены к входам второго элемента ИЛИ, девятый и десятый выходы подсоединены к входам счетчика шжлов, выход которого 15 через последовательно соединенные пороговый элемент и третий блок памяти подсоединен к второму входу третьего элемента ИЛИ, одиннадцатый выход блока вентилей подсоединен к первому входу первого блс 20 ка памяти, второй вход которого объединен с входом третьего блока памяти и вторым входом второго блока памяти, первый вход которого подключен к перва-.му входу счетчика тактов, первый выход 25 которого подсоединен к третьему входу первого блока памяти и через 6jjoK сравнения к первым входам блока инверторов и блока вентилей, второй выход счетчика тактов подсоединен к вторым входам бло-зо ка инверторов и блока вентилей, к третьим входам которых подсоединен выход счетчика сдвига, вход которого объединен с вторыми входами первого и второго регистров сдвига и подключен к ши- .j не импульсов сдвига, выход первого регистра сдвига подсоединен к четвертому

входу блока инверторов, а выход второго регистра сдвига подсоединен к первому входу первого элемента И, к второму входу которого подключен первый выход блока инверторов, а выход подсоединен к четвертому входу блока вентилей, пятый шестой, седьмой, восьмой и девятый входы которого подключены к соответствующим выходам блока инверторо }, пятый вход которого объединен с десятым входом блока вентилей и подключен к выходу первого элемента ИЛИ, выход второго элемента И подсоединен к одиннадцатому входу блока вентилей и шестому входу блока инверторов, седьмой вход которого подключен к двенадцатому выходу блока вентилей, двенадцатый вход которого подключен к выходу третьего блока памяти, тринадцатый выход блока вентилей через третий элемент ИЛИ подключен к седьмому входу блока инверторов и соответствуюшему входу коммутатора, дополнительный вход которого подключен к дополнительному выходу блока инверторов, к восьмому входу которого подключен четырнадцатый выход блока вентилей, к тринадцатому и четырнадцатому входам которого подключены другие входы блока инверторов, а пятнадцатый выход блока вентилей объединен с Еыходс второго блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 684757, кл. Н О4 L 7/О8, 1077.

2.Авторское свидетельство СССР № 64167О, кл. Н 04Ь 7/О8, 1077 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU985962A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство синхронизации по циклам | 1980 |

|

SU944135A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

Авторы

Даты

1982-07-15—Публикация

1980-12-29—Подача