(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной техниками может быть использовано в пультах управления телевизионных систем.,

Известно устройство памяти, содержащее ячейки памяти и блок-сброса til.

Недостатками этого устройства . являются неудовлетворительная надежность, обусловленная его инерционностыр и сло {ностью конструкции из-за большого количества элементов и связей между ними.

Наиболее близким по технической сущности к изобретению является запоминающее устройство, содержащее ячейки пaмяtи и .блок сброса.

Каждая ячейка памяти содержит коммутирующий и переключающий транзисторы и нагрузочные резисторы, а блок сброса - два транзистора с нагрузочными резисторами t2.

Недостатком этого устройства (является сложность конструкции.

Цель изобретения - упрощение конструкции запоминаняцего устройства.

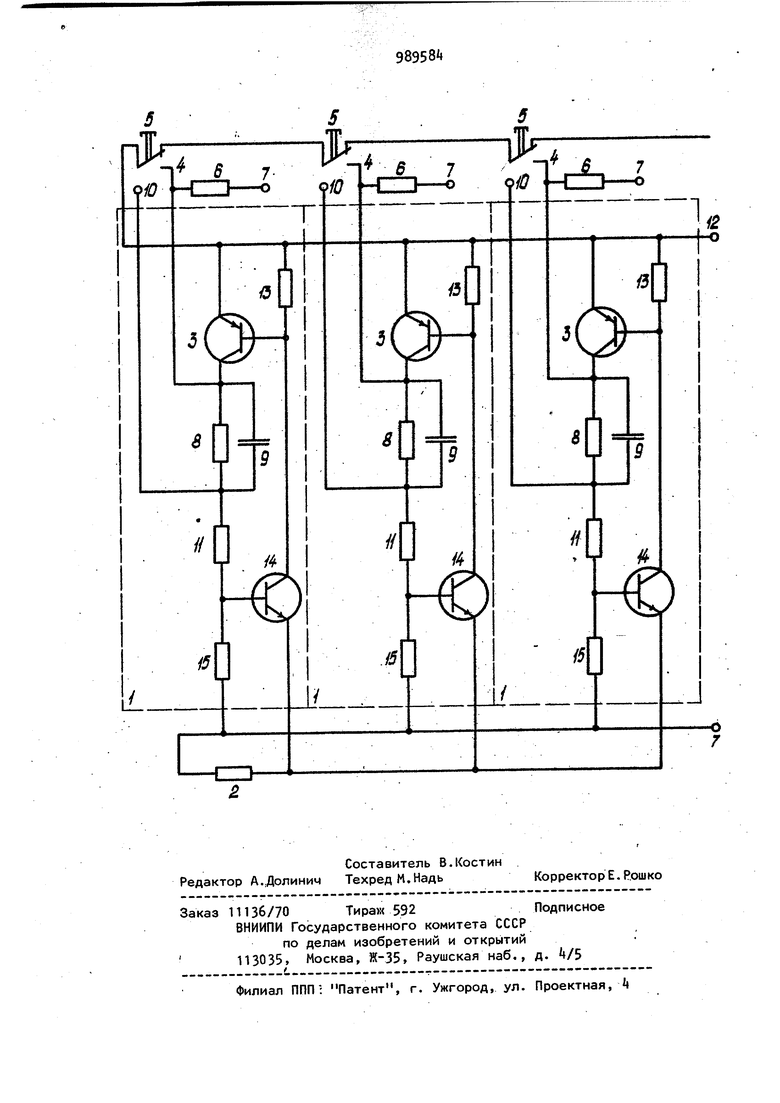

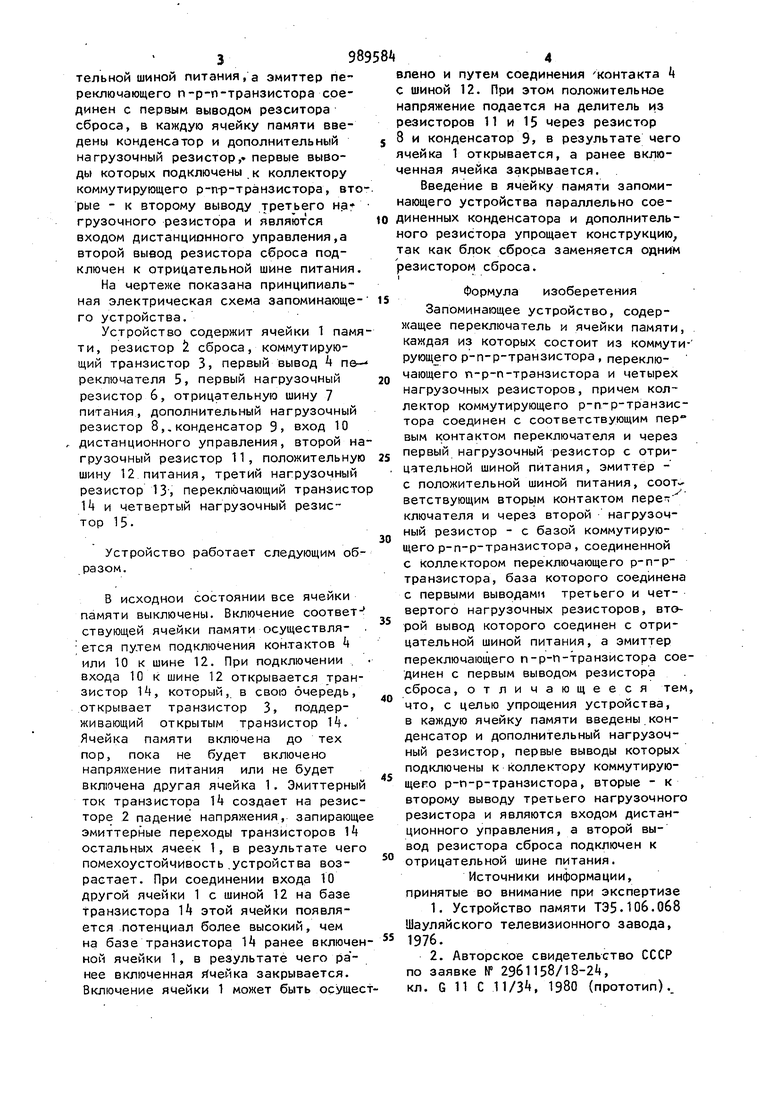

Поставленная цель достигается тем/ что в запоминающем.устройстве, содер- жащем переключатель и ячейки памяти, каждая из которых состоит из коммути рующего p-ft-p-транзистора, переключающего п-р-п-транзистора и четырех нагрузочных резисторов, причем кол: Лектор коммутирующего р-п-р-транзисtoтора сое;динен с соответствующим первым .контактом переключателя и через первый нагрузочный резистор с отрицательной, шиной питаний, эмиттер с положительнс 1 шиной питания, соот15ветствующим вторым контактом nepeKiwчателя и через второй нагрузочный резистор с базой коммутирующего р-п-р-транзистора,соединенной с колго лектором переключающего р-п-р-транзистора, база которого соединена с первыми выводами третьего и четвертого нагрузочных резисторов, второй вывод которого соединен с отрицательной шиной питания, а эмиттер пе реключающего п-р-п-транзистора соединен с первым выводом резситора сброса, в каждую ячейку памяти введены конденсатор и дополнительный нагрузочный резистор, первые выводы которых подключены к коллектору коммутирующего р-п-р-транзистора, вто рые - к второму выводу третьего нэг грузочного резистора и являются входом дистанционного управления,а второй вывод резистора сброса подключен к отрицательной шине питания. На чертеже показана принципиальная электрическая схема запоминающего устройства. Устройство содержит ячейки 1 памя ти, резистор сброса, коммутирующий транзистор 3, первый вывод 4 пв- реключателя 5, первый нагрузочный резистор 6, отрицательную шину 7 питания, дополнительный нагрузочный резистор 8,,конденсатор 9, вход 10 дистанционного управления, второй на грузочный резистор 11, положительную шину 12 питания, третий нагрузочный резистор 13, переключающий транзисто 1 и четвертый нагрузочный резис тор 15. Устройство работает следующим об разом. В исходной состоянии все ячейки памяти выключены. Включение соответ ствующей ячейки памяти осуществля; ется путем подключения контактов t или 10 к шине 12, При подключении . входа 10 к шине 12 открывается транзистор 1, который, в свою очередь, открывает транзистор 3, поддерживающий открытым транзистор И, Ячейка памяти включена до тех пор, пока не будет включено напряжение питания или не будет включена другая ячейка 1, Эмиттерный ток транзистора 14 создает на резисторе 2 падение напряжения, запирающе эмиттерные переходы транзисторов It остальных ячеек 1, в результате чего помехоустойчивость.устройства возрастает. При соединении входа 10 другой ячейки 1 с шиной 12 на базе Транзистора Н этой ячейки появляется потенциал более высокий, чем на базе транзистора 1А ранее включен ной ячейки 1, в результате чего ранее включенная Ячейка закрывается, Включение ячейки 1 может быть ocVtuec лено и путем соединения контакта 4 шиной 12, При этом положительное апряжение подается на делитель из езисторов 11 и 15 через резистор и конденсатор 3, в результате чего чейка 1 открывается, а ранее вклюенная ячейка закрывается. Введение в ячейку памяти запомиающего устройства параллельно соеиненных конденсатора и дополнителього резистора упрощает конструкцию, ак как блок сброса заменяется одним езистором сброса. Формула изоберетения Запоминающее устройство, содержащее переключатель и ячейки памяти, каждая из которых состоит из коммутирующего р-п-р-транзистора , переключающего п-р-п-транзистора и четырех нагрузочных резисторов, причем коллектор коммутирующего р-п-р-транзистора соединен с соответствующим пер вым контактом переключателя и через первый нагрузочный резистор с отрицательной шиной питания, эмиттер с положительной шиной питания, соот ветствующим вторым контактом переключателя и через второй нагрузочный резистор - с базой коммутирующего р-п-р-транзистора, соединенной с коллектором переключающего р-п-ртранзистора, база которого соединена с первыми выводами третьего и четвертого нагрузочных резисторов, второй вывод которого соединен с отрицательной шиной питания, а эмиттер переключающего п-р-п-транзистора соединен с первым выводом резистора сброса, отличающееся тем, что, с целью упрощения устройства, в каждую ячейку памяти введены конденсатор и дополнительный нагрузочный резистор, первые выводы которых подключены к коллектору коммутирующего р-п-р-транзистора, вторые - к второму выводу третьего нагрузочного резистора и являются входом дистанционного управления, а второй вывод резистора сброса подключен к отрицательной шине питания. Источники информации, принятые во внимание при экспертизе 1,Устройство памяти ТЭ5.106,068 Шауляйского телевизионного завода, 1976, 2,Авторское свидетельство СССР по заявке № 2961158/13-2 +, кл. СП С 11/3, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU942149A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ СИГНАЛИЗАЦИИ | 2005 |

|

RU2297672C1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1741167A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Коммутирующее устройство | 1985 |

|

SU1252834A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Коммутирующее устройство | 1982 |

|

SU1027821A1 |

| Коммутирующее устройство | 1983 |

|

SU1173546A1 |

Авторы

Даты

1983-01-15—Публикация

1981-06-02—Подача