нерсь: соответственно с первыми выводами второгр. и третьвхо источн.иков Ш91223 тока, вторые выводы источников тока под1слючены к второй шине питак ая.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Усилитель считывания | 1983 |

|

SU1104581A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

УСИЛИТЕЛЬ ЗАПИСИ И СЧИТЫБАШ-1Я ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ, содержащий группы управляющих п-р-п-траизисторов, эмиттеры которых являются разрядными входами усилителя, усилительные п-р-п-транзисторы с первого по четвертый, ограничивающие п-р-птранзисторы, нагрузочные резисторы и первый источник тока, причем коллекторы управляющих транзисторов первой группы, базы первого и третьего усилительных транзисторов и первый вывод первого нагрузочного резистора объединены и являются первым выходом усилителя, коллекторы управляющих транзисторов второй группы, базы второго и четвертого усилительных транзисторов и первый вывод второго нагрузочного резистора объединены и являются вторым выходом усилителя, вторые выводы нагру- зочных резисторов и ко.гшекторы усилительных транзисторов соединены с первой шиной питания, базы управляющих транзисторов первой и второй групп подключены соответственно к эмиттеру первого и эмиттеру в торого ограничивающих транзисторов, коллекторы которых соединены с первой шиной питания, базы первого и второго ограничивающих транзисторов являются соответственно первым и вторым управляющими входами усилителя, о т л и ч а ю Ц, и и с я тем, что, с целью повышения его быстродействия, в него введены переключающие п-р-птранзисторы с первого по шестой,смещающие диоды, третий и четвертый нагрузочные резисторы, первые выводы которых соединены соответственно с эмиттерами первого и четвертого и второго и третьего усилительных транзисторов , причем вторые выводы третьего и четвертого нагрузочных резисторов подключены соответственно к коллекторам первого и третьего пе реключающих транзисторов и базам управляющих транзисторов первой груп(Л пы и к коллекторам второго и четвертого переключающих транзисторов и бас зам управляющих транзисторов второй группы, базы третьего и четвертого переключающих транзисторов соединены соответственно с катодом первого и с катодом второго смещающих диодов, CD аноды которых подключены соответственно к эмиттеру пятого и к эмиттеру tc шестого переключающих транзисторов, к базы которых соединены соответственно с базой второго и базой первого огсо раничивающего транзисторов, коллекторы пятого и шестого переключающих транзисторов подключены к первой шине питания, базы -первого и второго переключающих транзисторов объединены и являются входом опорного напряжения усилителя, эмиттеры переключающих транзисторов с первого по четвертый соединены с первым выводом первого источника тока, катоды первого и второго смещающих диодов соеди

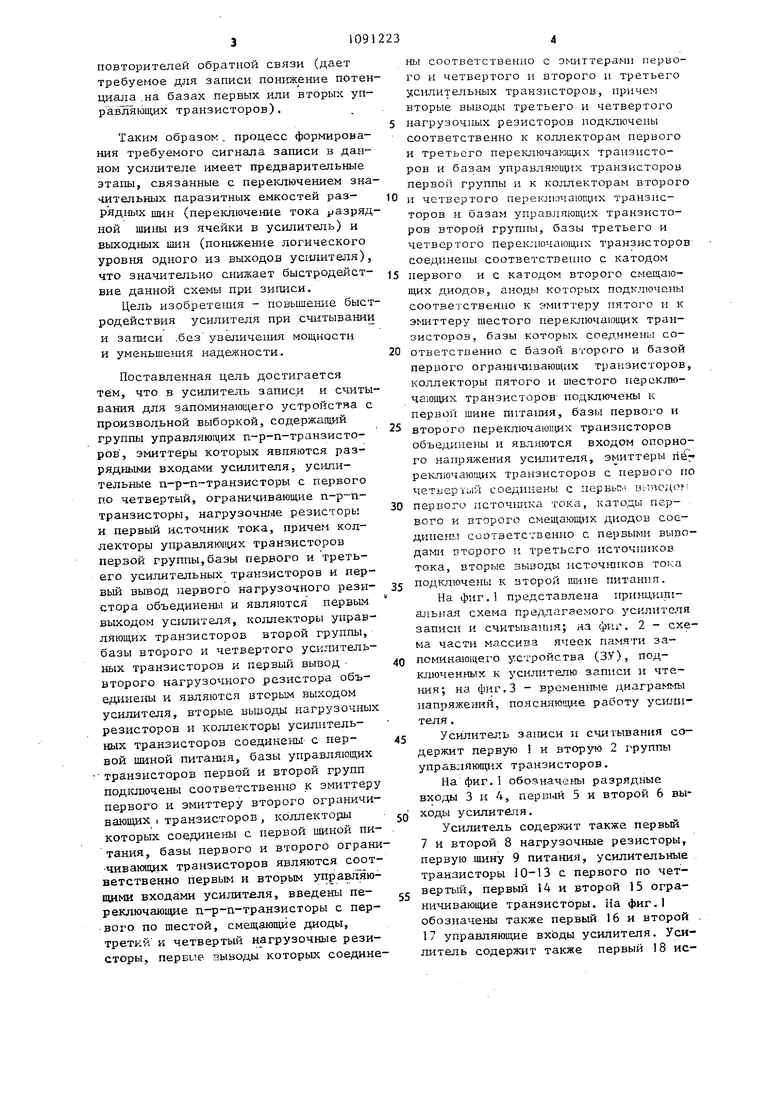

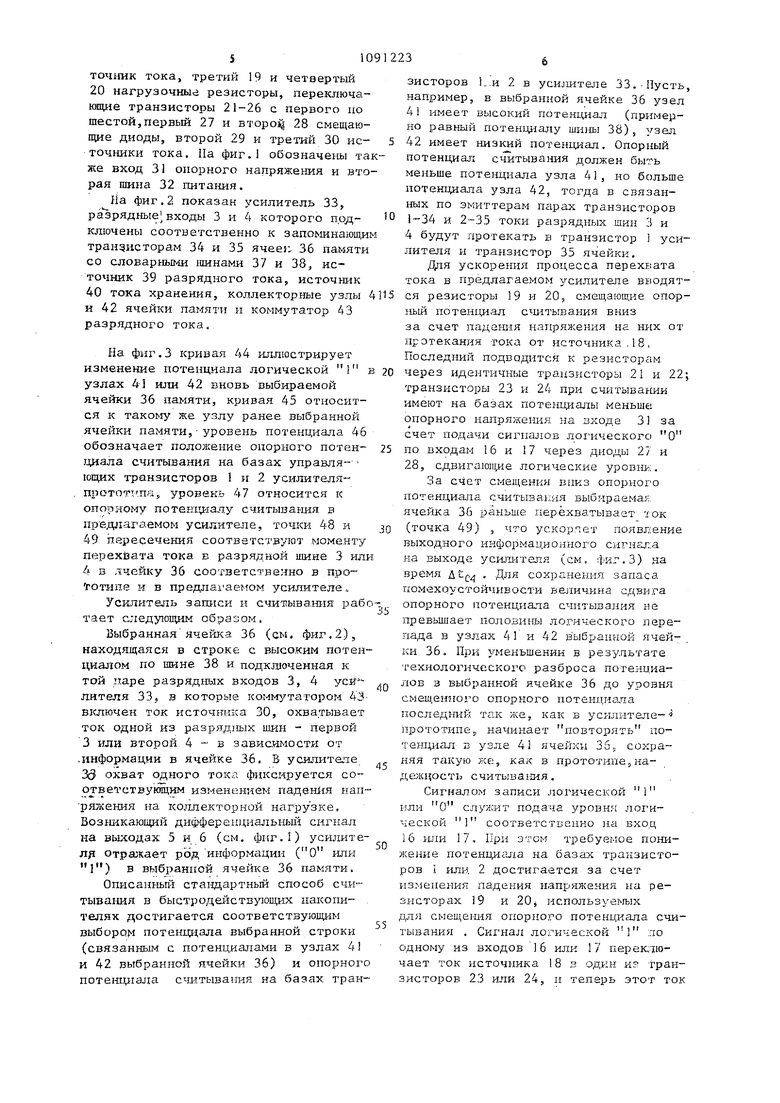

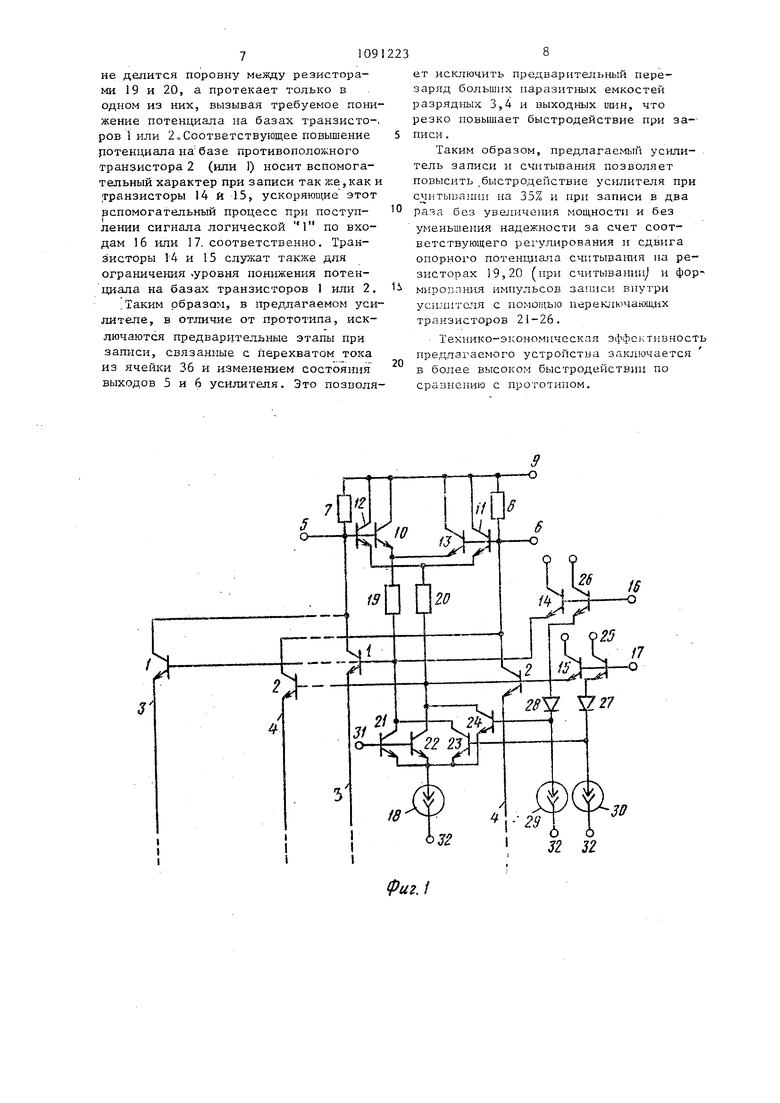

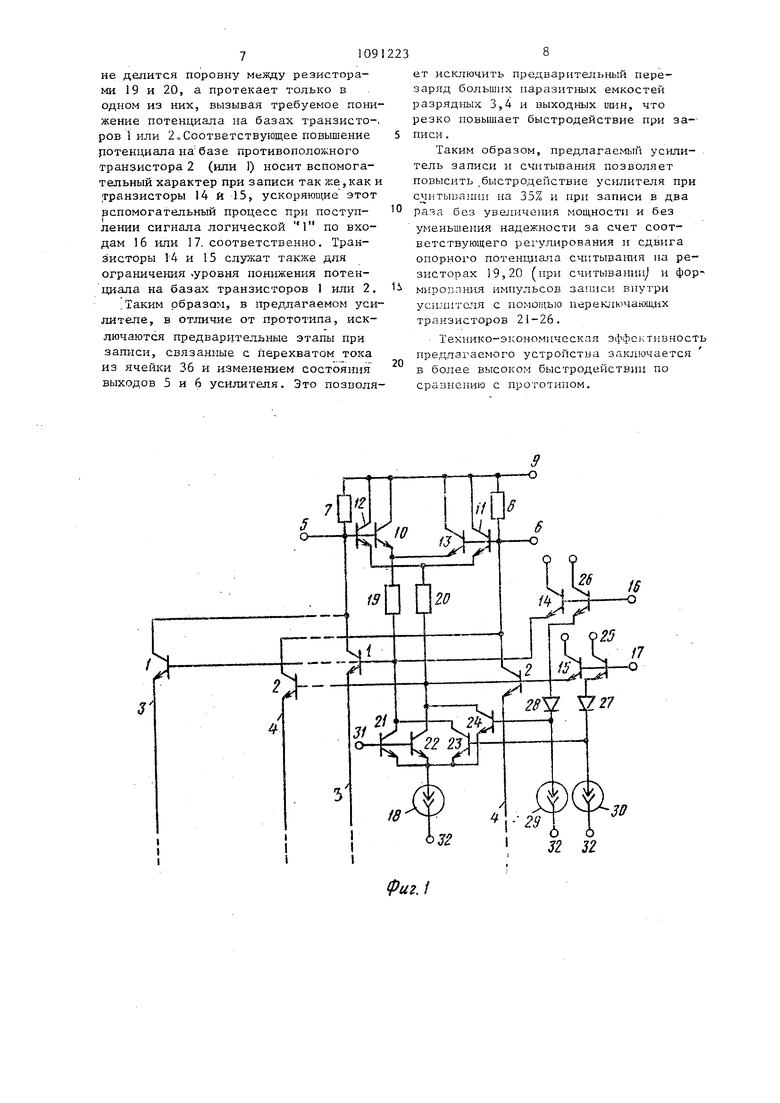

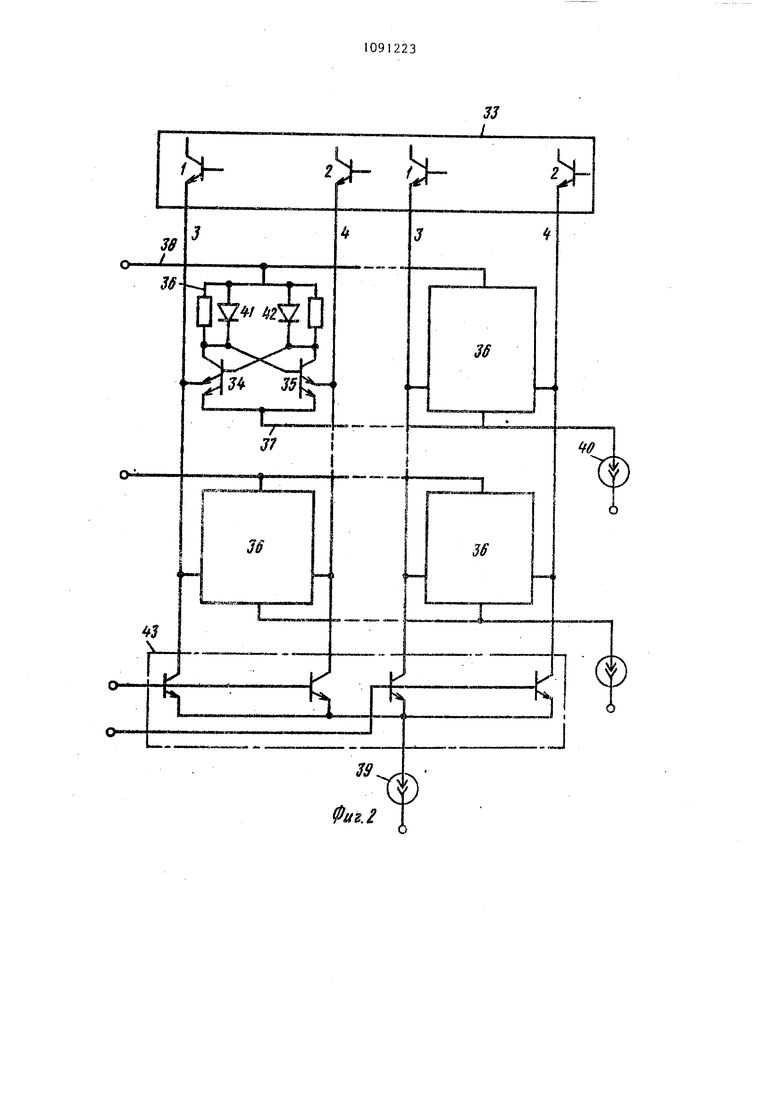

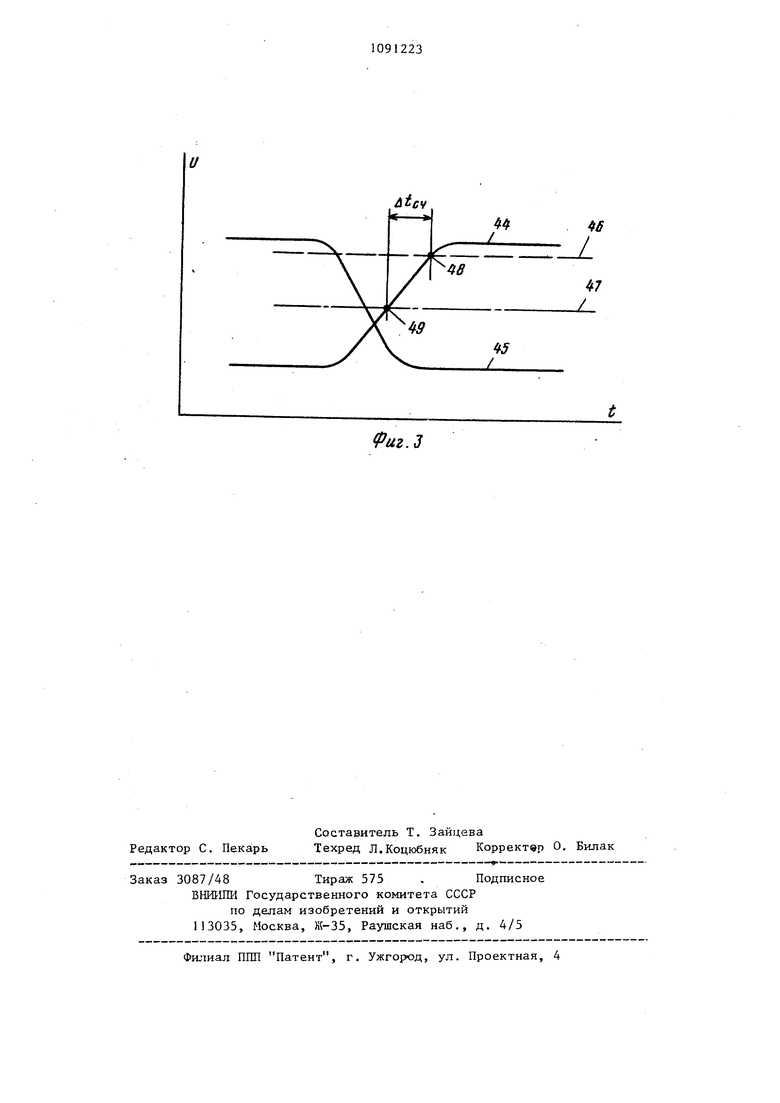

Изобретение относится к вычислительной технике и предназначено для использования в цифровых полупроводниковых схемах памяти с произвольной выборкой, в частности в интегральных схемах оперативной памяти на биполяр ных транзисторах. Известен усилитель записи и считывания для запоминаюищх устройств с произвольной выборкой, содержап ий пары первых и вторых управляющих тра зисторов, подключенных эмиттерами к парам соответственно первых и вторых разрядных шин,, причем коллекторы все первых и всех вторых транзисторов подключены соответственно к первой и второй выходным шинам и через соот ветственно nepBbui и второй резисторы - к шине питания, третий и четвертый транзисторы, .-;П;0дключен11ые кол лекторами к ййнй питания, базами соотвеп ственно к первой и второй выходным 1аИнам, эмиттерами к источнику тока и обьединенным базам всех и первых и вторых..управляющих транзисторо пары пяти и шестых управляющих транзисторов, подключенных эмиттерами соответственно к парам первых и вторь раэряддагх шин, коллекторами к шине питания, базами соответственно к первой и второй управляющим шинам, - управляемый источник тока, подключенньш через соответственно первьй и второй элементы развязки к первой и второй выходным шинам, вход управля емого источника тока подключен к дополнительной уп равляюш,ей тине ГО. Недостатками данного усилителя являются большое тшсло дополнительных управляющих транзисторов и низкое быстродействие, Наиболее близким техническим решением к изобретению является усилитель записи и считыватшя для запоминающего устройства с произвольной выбор кой, с одержащий пары первых и вторых транзисторов, подключенных эмиттерам соответственно к парам первых и вто рых разрядных шин, причем коллекторы всех первых и всех вторых транзисторов подключены соответственно к первой и. второй выходным шинам и через соответственно первый и второй резистор - к шине питания, третий и . четвертый транзисторы, подключенные базами соответственно к первой и второй выходным шинам, коллекторами к шине литания, эмиттерами к базам соответственно первых и вторых транзисторов и соответственно к первому и второму источгшкам тока, пятый и шестой транзисторы, подключенные коллекторами к шине питания, базами соответственно к первой н второй выходным шинам , эмиттерами соответственно к эмиттерам четвертого и третьего транзисторов, седьмой и восьмой транзисторы,, подключенные базами соответственно к первой и второй управляющим шинам, коллекторами к шине питания, эмиттерами соответственно к базам первых и вторых транзи сторов Г2.1. Недостатком прототипа является низкое быстродействие при считывании н записи информации, так как при считьшании, быстродействие огра-шчено высоким положением опорного потенциала считывания (в схемах данного типа последний .повторяет высокий уровень логической единицы выбргнндй ячейки памяти), а опорргогй потен1;;иал считывания за,цает порог пераключения тока разрядных 1иин 3 выбираемую ячейку и при высоком положении ..этого порога он достигается ячейкой позднее, только в конце переходного процесса смешз адреса строк. При записи 13 данной схеме ввиду невозмож юсти )Непосредственно понизить потенциал относительно опорного на базах первых или вторых управляющих транзисторов из-за эми1терных повторителей обратной связи (транзисторы с трет.ьего по шестой) применяется предварительное переюдачение тока одной из разрядных шин в усилитепь. При этом соответственно пони хается потенци повторителей обратной связи (дает требуемое для записи понижение поте циала .на базах первых или вторых уп ра впяющих транзисторов). Таким образом, процесс формирования требуемого сигнала записи в данном усилителе имеет предварительные этапы, связанные с переключением зна чительных паразитных емкостей разрядных шин (переключение тока разряд ной шины из ячейки в усилитель) и выходных miiH (поьшжение логического уровня одного из выходов усшштеля), что значительно снижает быстродействие данной схемы при зиписи. Цель изобретения - повьше1-п1е быст родействия усилителя при считывании и записи .без увеличения мощности и уменьшегшя надежности. Поставленная цель достигается те;м, что в усилитель записи и считы вания для запоминающего устройства с произвольной выборкой, содержащий группы управляющих п-р-п-транзисторов, эмиттеры которых являются разрядными входами усилителя, усилительные п-р-п-транзисторы с первого по четвертый, ограничивающие п-р-птранзисторы, нагрузочшле резисторы и первый источник тока, причем коллекторы упр.авляюпдях транзисторов первой группы,базы первого и третьего усилительных транзисторов и первый вывод первого нагрузочного резистора объединены и являются первым выходом усилителя, коллекторы управляющих транзисторов второй группы, базы второго и четвертого усилительных транзисторов и первый вывод второго нагрузочного резистора объединены и являются вторым выходом усилителя, вторые выводы нагрузочных резисторов и коллекторы усилительных транзисторов соединены с первой шиной питания, базы управляющих транзисторов первой и второй групп под1слючены соответственнр к эмиттеру первого и эмиттеру второго ограничивающих 1 транзисторов , коллекторы которых соединены с первой шиной питания, базы первого и второго ограни чивакящх транзисторов являются со ответственно первым и вторым управляющими входами усилителя, введены переключающие п-р-п-транзисторы с первого по шестой, смещающие диоды, третий и четвертый нагрузочные резисторы, nepBLe выводы которых соедине нь соответственно с эмиттерами первого и четвертого и второго и третьего усилительных транзисторов, причем вторые выводы третьего и четвертого нагрузоч1шх резисторов подключень соответственно к коллекторам первого и третьего переключаюцщх транзисторов и базам управляюиц1х транзисторов первой группы и к коллекторам второго и четвертого переклгачаюпщх транзисторов и базам управляющих транзисторов второй группы, базы третьего и четвертого переключающих транзисторов соединены соответственно с катодом первого и с катодом второго смещающих диодов., аноды которых подключены соответственно к эмиттеру пятого и к 3NmTTepy шестого переключающих транзисторов, базы которых соединены соответственно с базой второго и базой первого ограничивающих транзисторов, коллекторы пятого и шестого переключающих транзисторов подключены к первой шине питания, базы первого и второго переключающих транзисторов объединены и являются входом опорного напряжения усилителя, эмиттеры реключающих транзисторов с первого по четьертый соединены с иервы 1 ш-г.юдсГ первого псточ1П1ка тока, катоды первого и второго смещающих диодов соединегш соответственно с первыми выводами: второго II третьего источников тока, вторые выводы источников тока подключены к второй пипе питания. На фиг.1 представлена иринциш альная схема предлагаемого усилителя записи и считывания; на фяг. 2 - схема части массива ячеек памяти запоминающего устройства (ЗУ), подключенных к усилителю записи и чтения; на фиг.З - временпь1е диаграммы напряжений, поясняющее работу усшштеля . Усилитель записи и считывания содержит первую I и вторую 2 группы управляющих транзисторов. На фиг.1 обозначены разрядные входы 3 и 4, первый 5 и второй 6 выходы усилителя. Усилитель содержит также первый 7 и второй 8 нагрузочные резисторы, первую щину 9 питания, усилительные транзисторы 10-13 с первого по четвертый, первый 14 и второй 15 ограничивающие транзисторы. На фиг.1 обоз}1ачены также первый 16 и второй 17 управляющие входы усилителя. Усилитель содержит также первый 18 источник тока, третий 19 и четвертый 20 нагрузочные резисторы, переключающие транзисторы 21-26 с первого по шестой,первый 27 и второ 28 смещающие диоды, второй 29 и третий 30 источники тока. Па фиг. обозначены та же вход 31 опорного напряжеьшя и вто рая шина 32 питания. lia фиг.2 показан усилитель 33, разрядные входы 3 и 4 которого подключены соответственно к зaпo шнaющи транзисторам 34 и 35 ячеек, 36 памяти со словарными шинами 37 и 38, источник 39 разрядного тока, источник 40 тока хранения, коллекторные узлы и 42 ячейки памяти и коммутатор 43 разрядного тока. На фиг.З кривая 44 иллюстрирует изменение потенциала логической узлах 41 или 42 вновь выбираемой ячейки 36 памяти, кривая 45 относится к такому же узлу ранее выбранной ячейки памяти, уровень потенциала 46 обозначает пололгение опорного потенгдаала считывания на базах управля-- ющих транзисторов 1 и 2 усилителяпрототипа, уровень 47 относится к опорному потеыгдаалу считывания в предлагаемом усилителе, точки 48 и 49 пересечения соответствуют моменту перех зата тока в разрядной шине 3 ил 4 в ячейку 36 соответственно в прототипе и в предла1аемом усилителе. Усилитель записи и считгывашш раб тает следующим образом. Выбраннаяячейка 36 (см. фиг.2), находящаяся в строке с высоким потен циалом по шине 38 и подключенная к той паре разрядных входов 3, 4 усй лителя 33, в которые коммутатором 43 взшючен ток источника 30, охватывает ток одной из разрядных шин - первой 3 или второй 4 - в зависимости от .информации в ячейке 36. В усилителе охват одного тока фиксируется соответствующим изменением паден11я нап ряжения на. коллекторной нагрузке, Бозршкаюцщй дифференциальньш сигнал на выходах 5 и б (см. фиг.1) усилите лр отразкает род информации (О или I) в выбранной ячейке 36 памяти. Описанный стандартньй способ считыва1шя в быстр од ействуюцдах накопителях достигается соответствующим выбором потенциала выбранной строки (связанным с потенциалами в узлах 41 и 42 выбранной ячейки 36) и опорног потенциала считывания на базах тран зисторов 1..И 2 в усшштеле 33.-Пусть, например, в выбранной ячейке 36 узел 41 имеет высокий потенциал (примерно равный потенциалу шины 38), узел 42 имеет низкий потенциал. Опорный потенциал считывания должен быть меньше потенциала узла 4, но больше потенциала узла 42, тогда в связанных по эмиттерам парах транзисторов 1-34 и 2-35 токи разрядных шин 3 и 4 будут протекать в транзистор усилителя и транзистор 35 ячейки. Для ускорения процесса перехвата тока в предлагаемом усилителе вводятся резисторы 19 и 20, смещающие опорзйый потенциал сгштьшания вниз за счет падания напряжения на них от протекания тока от источника , 18. Последний подводится к резисторам через идентичные транзисторы 21 и 22; транзисторы 23 и 24 при считывавши имеют на базах потенциалы меньше опорного напряжения на входе 31 за счет подачи сигпалов логического О по входам 16 и 17 через диоды 27 и 28, сдвигаюпще логические уровни:. За счет смещении вакз опорного потенциала считывания выбираемая; ячейка 36 т аньше перехватывает ток (точка 49) 3 что ускоряет появление выходного информационного сигнал:а на выходе усилителя (см. фиг.З) на время At(, . Для сохраненыя запаса помехоустойчивости величина сдвига опорного потенциала считывания не превьицает половины логического перепада в узлах 41 и 42 выбрапной ячей-, кк 36, При уменьшении в результате техиологического разброса потени.иалов в выбранной ячейке 36 до уровня смеш,енггого опорного потенциала послед -шй так же, как в усилителепрототипе,, начинает повторять потенцигш в узле 41 ячейки 36. сохраняя такую же, как в прототипе,наде;кцость считывания. Сигнал.ом записи логической I О служит подача уровн.ч логической соответс- лг,г,т,. вход 16 1-ши 17. При этом требуемое понижение потенциала на базах транзисторов i или. 2 достигается за счет изменения падения напряжения на резисторах 19 и 20, используеьшх для смещегшя опорного потенциала считывания . Сигнал логичес.кой 1 :гю одному из входов 16 или 17 переключает ток источника 18 в один из транзисторов 23 или 24, н теперь этот ток

не делится поровну между резисторами 19 и 20, а протекает только в одном из них, вызывая требуемое понижение потенциала на базах транзисторов 1 или 2 о Соответствующее повьшение потенциала набазе противоположного транзистора 2 (или ) носит вспомогательный характер при записи так же,как и транзисторы 14 и 15, ускоряющие этот эспомогательный процесс при поступлении сигнала логической 1 по входам 16 или 17. соответственно. Транзисторы 14 и 15 служат также для ограничения .уровня понижения потенциала на базах транзисторов 1 или 2.

.Таким образом, в предлагаемом усилителе, в отличие от прототипа, исключаются предварительные этапы при записи, связашше с перехватом тока из ячейки 36 и изменением состояния выходов 5 и 6 усилителя. Это позволяет исктпочить предварительный перезаряд больших паразитных емкостей разрядных 3,4 и выходных ишн, что резко повышает быстродействие при записи .

Таким образом, предлагаемый усилитель записи и считывания позволяет повысить .быстродействие усилителя при считывании на 35% и при записи в два раза без увеличения мощности и без уменьшения надежности за счет соответствующего регулирования и сдвига опорного потенциала С411тыва1шя на резисторах 19,20 (при считывании/ и формировашш импульсов записи внутри усилителя с помощью переключающих транзисторов 21-26.

Технико-экономическая эффективность предлагаемого устройства заключается в более высоком быстродействии по сравнению с прототипом.

3

(.i у Ьг1

&ic4

иг,3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4078216, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборное колесо | 1921 |

|

SU370A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-11—Подача