(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU989584A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ СИГНАЛИЗАЦИИ | 2005 |

|

RU2297672C1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Коммутатор | 1982 |

|

SU1045385A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1741167A1 |

Изобретение относится к вычислитель ной технике и может быть использовано для запоминания информаяии в телевизионных системах. Известно запоминающее устройство, содержащее тиристор, коммутирующиетранзисторы и резисторы . Недостатком известного устройства является неудовлетворительное быстродействие из-за ограниченной скорости включения и выключения тиристоров, большое количество элементов в ячейке памяти. Цель изобретения - повьпиение быстродействия устройства. Поставленная цель достигается тем, что в запоминающем устройстве, содержащем ячейку памяти, состоящую из коммутирующего р и -р-транзистора, база которого через нагрузочный резист соединена с эмиттером и щиной питания блок сброса, кнопочный переключатель, первый вьгоод которого соединен с шино питания, и общую шину, в ячейку памяти введень переключающий и - р - И транзистор и два дополнительных нагрузочных резистора, первый вывод первого из которых подключен к коллектору коммутирующего р - VI - р -1ранзистора, второй - к базе переключающего и - р И -транзистора и первому выводу второго допогаттельного нагрузочного реаистора, второй вьшод которого подключен к общей щине, а коллектор переключающего м - р - V -транзистора подключен к базе коммутирующего р - VI - р транзистора, блок сброса вьтолнен из двух переключающих транзисторов одинакового типа проводимости и четьфех нагрузочных и одного суммирующего резисторов, причем база первого переключающего транзистора подключена к коллектору второго переключающего транзистора и через первый нагрузочный резистор к щине питания, эмиттеры переключающих транзисторов и первый вьтод суммирующегч) резистора подключены к общей шине, коллектор первого перекгаочающего транзистора подйлючен через второй нагрузочный резистор к эмиттеру перекгаочающего транзистора ячейки памяти, база вторюго переключаю щего транаистора подключена к второму выводу суммирующего резистора и через третий нагрузочный резистор к коллектору коммутирующего транзистора ячейки памяти, второму вьшоду кнопочного переключателя и первому выводу четвертого нагрузочного резистора, второй вывод которого ПОДКЛЮЧИ к общей щине.

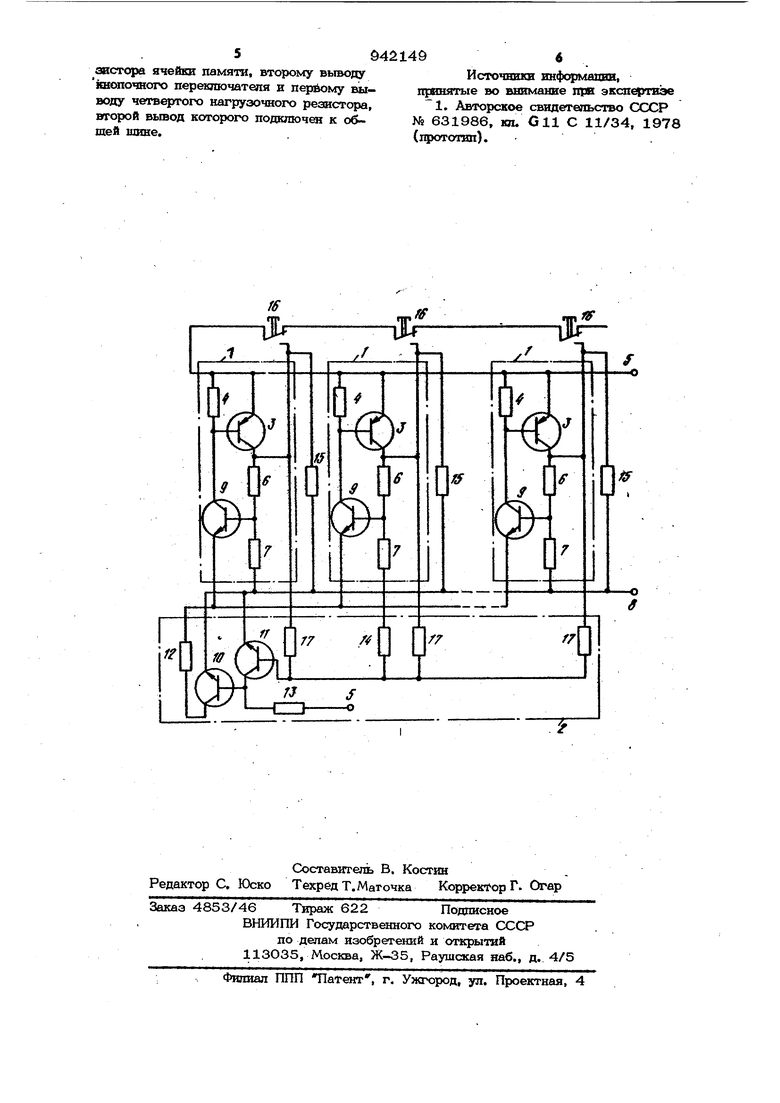

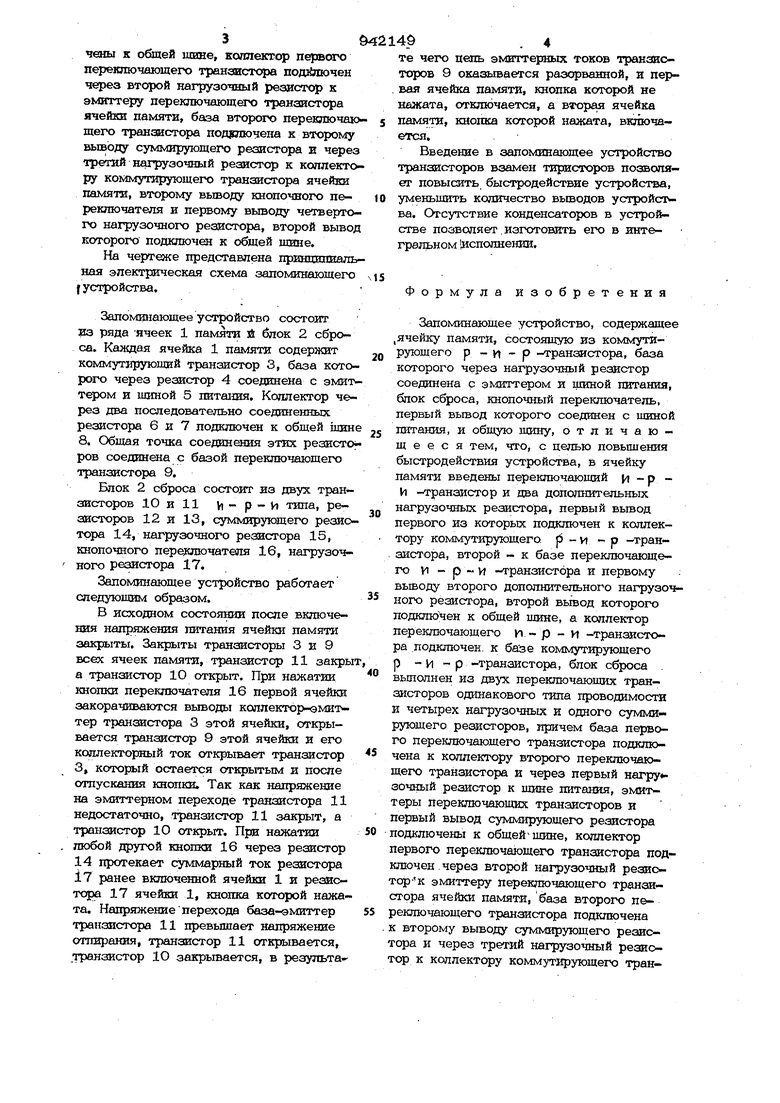

На чертеже представлена принципиальная электрическая схема запоминающего (устройства.

Запоминающее устройство состоит из ряда -ячеек 1 памята и блсж 2 сброса. Каждая ячейка 1 памяти содержит коммутирующий транзистор 3, база которого через резистор 4 соединена с эмиттером я шиной 5 питания. Коллектор через два последовательно соединенных резистора 6 и 7 подключен к общей шин 8. Общая точка соединения этих резисторов соединена с базой переключающего транзистора 9.

Блок 2 сброса состоит из двух транзисторов 1Ои11 Vi-p-И типа, резисторов 12 и 13, суммирующего резистора 14, нагрузочного резистора 15, кнопочного переключателя 16, нагрузочного резистора 17.

Запоминающее устройство работает следующим образом.

В исходном состоянии после включения напряжения питания ячейки памятей закрыты. Закрыты транзисторы 3 и 9 всех ячеек памяти, транзистор 11 закры а транзистор 10 открыт. При нажатии кнопки переключателя 16 первой ячейки закорачиваются выводы коллектор-эмиттер транаистора 3 этой ячейки, открывается транзистор 9 этой ячейки и его коллекторный ток открьтает транзистор 3, который остается открытым и после отпускания кнопки. Так как напряжение на эмиттерном переходе транзистора 11 недостаточно, транзистор 11 закрыт, а транзистор 10 открыт. При нажатии

любой другой кнопки 16 через резистор 14 протекает суммарный ток резистора 17 ранее включенной ячейки 1 и резистора 17 ячейки 1, кнопка которой нажата. Напряжение перехода база-эмиттер транзистора 11 превьшает напряжение отпирания, транзистор 11 открывается, транзистор 1О закрьгаается, в резутгьтате чего дезпь эмиттерных токов транзисторов 9 оказывается разорванной, и первая ячейка памяти, кнопка которой не нажата, отключается, а вторая ячейка памяти, кнопка которой нажата, включается.

Введение в запоминающее устройство транзисторов взамен тиристоров позволяет повысить быстродействие устройства, уменьшить количество вьгоодов устройства. Отсутствие конденсаторов в устройстве позволяет.изготовить его в интегральном | 1сполнении.

Формула изобретения

Запоминающее устройство, содержаще .ячейку памяти, состоящую из коммутирующего р - и р -транзистора, база которого через нагрузочный резистор соединена с эмиттером и щиной питания, блок сброса, кнопочный переключатель, первый вьгоод которого соединен с шиной питания, и общую шину, отличающееся тем, что, с целью повьшхения быстродействия устройства, в ячейку памяти введены переключающий ц - р И -транзистор и два дополнительных нагрузочных резистора, первый вьгаод первого из которых подключен к коллектору коммутирующего. 5 - vt - р -тран. зистора, второй - к базе переключающего и - р и -транзистора и первому выводу второго дополнительного нагрузоного резистора, второй вьгаод которого подклк)чен к общей щине, а коллектор переключающего у - р - и -транзистора подключен, к базе коммутирующего р -И - р -транаистора, блок сброса . вьшопнен из двух переключающих транзисторов одинакового типа проводимости И четырех нагрузочных и одного суммирующего резисторов, причем база первого переключающего транзистора подключена к коллектору второго переключающего транзистора и через первый нагру зочный резистор к щине питания, эмиттеры переключающих транзисторов и первый вывод суммирующего резистора подключены к общей щине, коллектор первого переключающего транзистора подключен, через второй нагрузочный резистор-к эмиттеру переключающего транзистора ячейки памяти, база второго переключающего транзистора подключена к второму выводу суммирующего резистора и через третий нагрузочный резистор к коллектору коммутирующего тран sacTopa ячейки памяти, второму вьгаоду кнопочного перекшочатепя и пербому выводу четвертого нагрузочного резистора, второй вьгаод которого подключен к обшей шине. 9 49 ИсточнЕкв информапвв, пршштые во внимание при экспертЕэе 1. Авторское свидетельство СССР № 631986, юь Он С 11/34, 1978 (прототип).

Авторы

Даты

1982-07-07—Публикация

1980-07-16—Подача