о

4 О

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1986 |

|

SU1361630A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1573472A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

Изобретение относится к электронике и вычислительной технике и может быть использовано в запоминающих устройствах (ЗУ) на биполярных транзисторах. Целью изобретения является повышение надежности работы запоминающего устройства за счет более полной компенсации влияния изменения температуры и величины напряжения питания. Устройство содержит источник 1 тока, нагрузочный транзистор 2, первый 3 и второй 4 резисторы смещения, элемент шунтирования в виде диода 5, первый согласующий транзистор 6, третий резистор 7 смещения, второй согласующий транзистор 8, компенсирующий резистор 9, вход 10 подключения нулевого потенциала источника 10

питания, переключающий транзистор 11, третий 12 и четвертый 13 согласующие транзисторы, токозадающий резистор 14, вход 15 подключения напряжения источника питания, выход 16 устройства, стабилизирующий элемент в виде конденсатора 17. Введение в параметрический источник четвертого согласующего транзистора и со Изобретение относится к электронике и вычислительной технике и может быть использовано в запоминающих устройствах на биполярных транзисторах.

Целью изобретения является повыше- ние надежности работы запоминающего устройства за счет более полной компенсации влияния изменения температуры и величины напряжения питания.

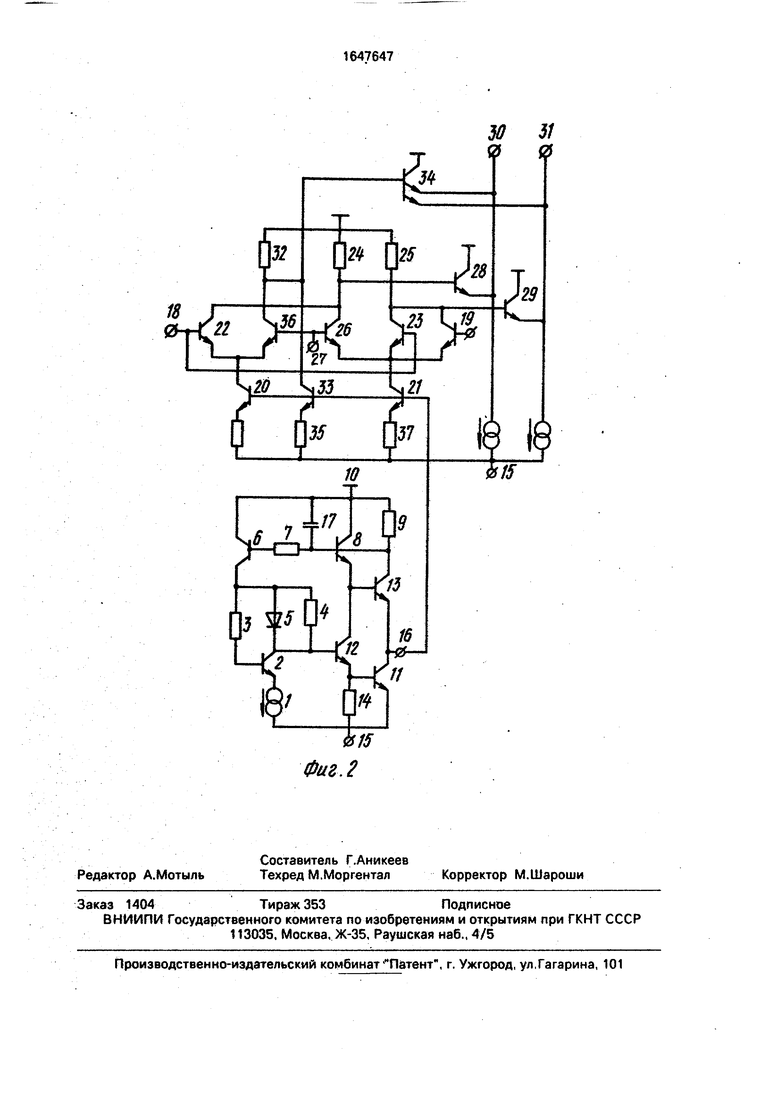

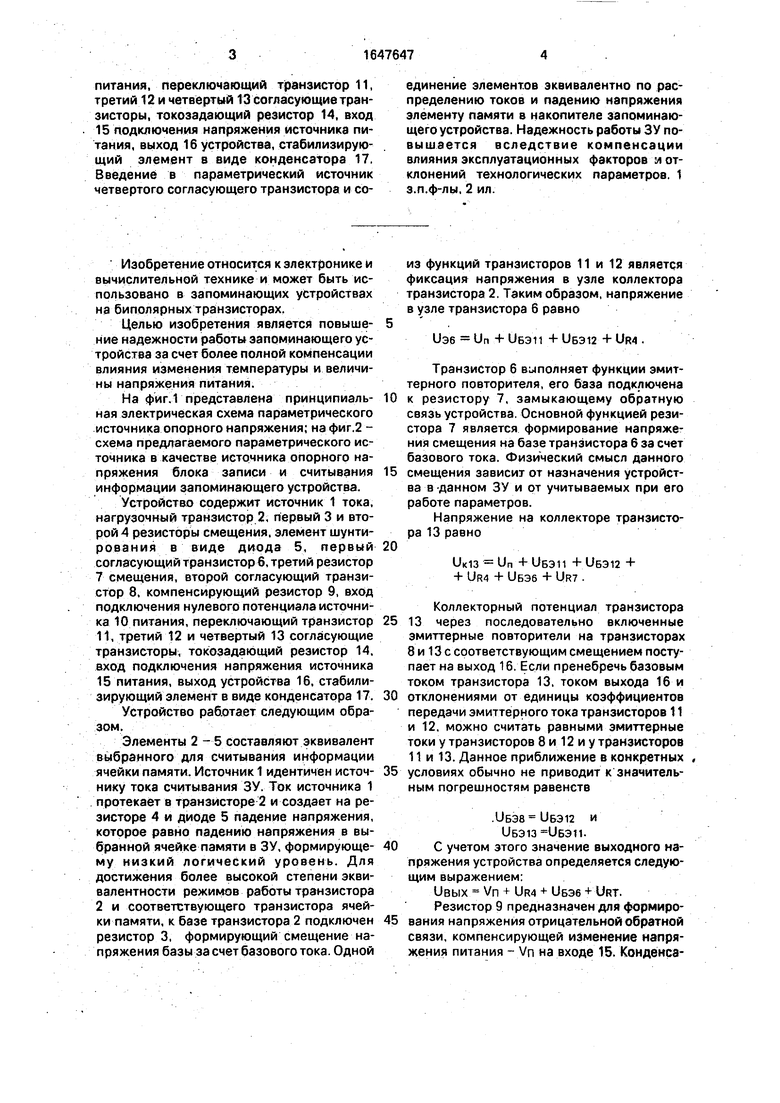

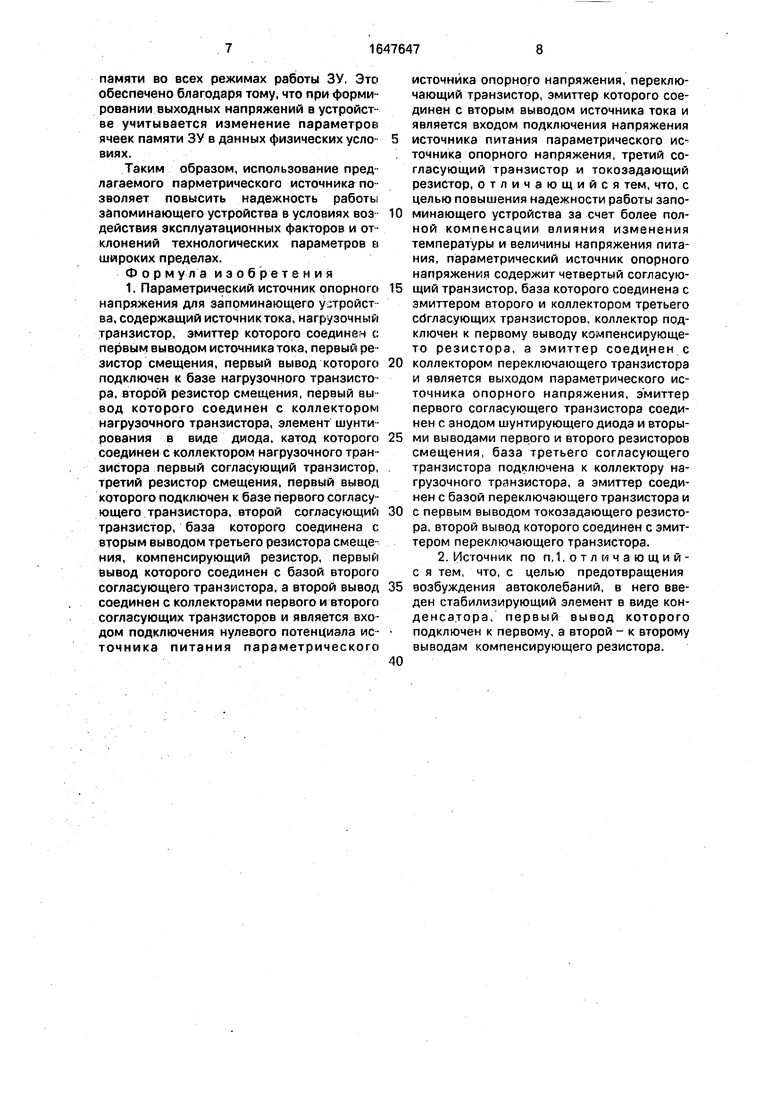

На фиг.1 представлена принципиаль- ная электрическая схема параметрического источника опорного напряжения; на фиг.2 - схема предлагаемого параметрического источника в качестве источника опорного напряжения блока записи и считывания информации запоминающего устройства.

Устройство содержит источник 1 тока, нагрузочный транзистор 2, первый 3 и второй 4 резисторы смещения, элемент шунтирования в виде диода 5, первый согласующий транзистор 6, третий резистор 7 смещения, второй согласующий транзистор 8, компенсирующий резистор 9, вход подключения нулевого потенциала источника 10 питания, переключающий транзистор 11, третий 12 и четвертый 13 согласующие транзисторы, токозадающий резистор 14, вход подключения напряжения источника 15 питания, выход устройства 16, стабилизирующий элемент в виде конденсатора 17.

Устройство работает следующим образом.

Элементы 2-5 составляют эквивалент выбранного для считывания информации ячейки памяти. Источник 1 идентичен источнику тока считывания ЗУ. Ток источника 1 протекает в транзисторе 2 и создает на резисторе 4 и диоде 5 падение напряжения, которое равно падению напряжения в выбранной ячейке памяти в ЗУ, формирующе- му низкий логический уровень. Для достижения более высокой степени эквивалентности режимов работы транзистора 2 и соответствующего транзистора ячейки памяти, к базе транзистора 2 подключен резистор 3, формирующий смещение напряжения базы за счет базового тока. Одной

единение элементов эквивалентно по распределению токов и падению напряжения элементу памяти в накопителе запоминающего устройства. Надежность работы ЗУ по- вышается вследствие компенсации влияния эксплуатационных факторов и отклонений технологических параметров. 1 з.п.ф-лы, 2 ил.

из функций транзисторов 11 и 12 является фиксация напряжения в узле коллектора транзистора 2, Таким образом, напряжение в узле транзистора 6 равно

U36 Un + UB311 + UB312 + UR4 .

Транзистор 6 выполняет функции эмит- терного повторителя, его база подключена к резистору 7, замыкающему обратную связь устройства. Основной функцией резистора 7 является формирование напряжения смещения на базе транзистора 6 за счет базового тока. Физический смысл данного смещения зависит от назначения устройства в -данном ЗУ и от учитываемых при его работе параметров.

Напряжение на коллекторе транзистора 13 равно

UK13 Un + UB311 + UB312 + + UR4 + UB36 + UR7 .

Коллекторный потенциал транзистора 13 через последовательно включенные эмиттерные повторители на транзисторах 8 и 13 с соответствующим смещением поступает на выход 16. Если пренебречь базовым током транзистора 13. током выхода 16 и отклонениями от единицы коэффициентов передачи эмиттерного тока транзисторов 11 и 12, можно считать равными эмиттерные токи у транзисторов 8 и 12 и у транзисторов 11 и 13. Данное приближение в конкретных условиях обычно не приводит к значительным погрешностям равенств

.иБЭ8 и&Э12 И UB313 UB311.

С учетом этого значение выходного напряжения устройства определяется следующим выражением:

Увых Vn UR4 + U536 + URT.

Резистор 9 предназначен для формирования напряжения отрицательной обратной связи, компенсирующей изменение напряжения питания - Vn на входе 15. Конденсатор 17, шунтирующий резистор 8, ослабляет коэффициент усиления обратных связей на высоких частотах, что необходимо для предотвращения возникновения автоколебаний. В устройстве присутствуют две цепи отрицательной обратной связи: между коллектором и базой транзистора 13 через транзистор 8 и между коллектором транзистора 13 и базой транзистора 11 через цепь из элементов 7, 6, 4, 5 и 12.

Для иллюстрации проявления положительного эффекта рассмотрим использование предлагаемого параметрического источника, как источника опорного напряжения блока записи и считывания информации запоминающего устройства (фиг.2).

Блок записи и считывания работает следующим образом.

В режиме считывания информации на входе 18 установлено напряжение высокого логического уровня, при этом независимо от уровня напряжения на входе 19 коллекторные токи транзисторов 20 и 21 протекают через транзисторы 22 и 23 в резисторы 24 и 25, создают на них падения напряжений. Для обеспечения такого режима работы устройства и возможности переключения транзисторов 22,26 при изменении уровней напряжений на входах 18 и 19 напряжение на шине 27 должно соответствовать среднему от высокого и низкого логических уровней напряжений на входах 18 и 19. Падение напряжений на резисторах 24 и 25 приводит к формированию низких логических уровней на базах транзисторов 28 и 29, в результате чего эти транзисторы оказываются запертыми и не влияют на уровни напряжений на выходах 30, 31. Падение напряжения на резисторе 32 создается колекторным током транзистора 33, это напряжение значительно меньше, чем на резисторах 24 и 25, поэтому базовый потенциал транзистора 34 выше чем у транзисторов 28, 29, транзистор 34 формирует уровни напряжений на выходах 30 и 31 в соответствии со следующим выражением:

R32

R35

Raz (Б 34;

(Ui6 - Up - УБЭЗЗ ) где Vie /вых для параметрического источника опорного напряжения.

В данном выражении сумма в скобках соответствует напряжению на резисторе 35. Если обеспечить равенство напряжений Vea у транзисторов 6 и 33, напряжение на резисторе 35 будет соответствовать сумме напряжений на резисторах 4 и 7, которые эквивалентны смещениям высокого и низ:

кого уровней напряжений в выбранной ячейке памяти матрицы ЗУ. Таким образом, в режиме считывания информации на выходе блока записи и считывания будет

формироваться уровень считывания, соответствующий полусумме высокого и низкого уровней в выбранной ячейке памяти, если соотношение номинальных сопротивлений R32/R35 установлено равным 1/2. Если при

этом падение напряжения на резисторе 32 не соответствует аналогичному напряжению в дешифраторе ЗУ. оно может быть сбалансировано изменением напряжения UR за счет определенного расчетами увеличения или уменьшения величины сопротивления резистора 7.

В режиме записи информации на входе

18устанавливается напряжение низкого логического уровня, а напряжение на входе 19

соответствует записываемым данным. Ток коллектора транзистора 20 переключается в транзистор 36 и совместно с коллекторным током транзистора 33 создает на резисторе 32 большое падение напряжения, запирающее транзистор 34. Ток коллектора транзистора 23 в соответствии с уровнем на входе

19протекает либо в резисторе 24, либо в резисторе 25. Напряжения на выходах 30 и 31 в данном режиме определяются транзисторами 28. 29. Высокий выходной уровень определяется выражением

/

ивых зап - - R 24 Б 28 - УБЭ 28 .

Данный уровень в наилучшем случае должен лежать выше высокого уровня в выбранной ячейке памяти. В рассматриваемом устройстве это может быть достигнуто, если падение напряжений на резисторах 24

и 25 за счет базовых токов транзисторов 28 и 29 удается сделать меньше чем смещение высокого уровня в выбранной ячейке памяти. Низкий уровень напряжений на выходах 30 и 31 соответствует выражению

и°ых.зап. - (L)R7 + UR4) - - R 24 IB 28 UB3 28

Для обеспечения записи информации в выбранную ячейку памяти уровень низкого напряжения записи должен лежать ниже низкого уровня в ячейке памяти. Из данного выражения видно, что данное требование

легко выполнить, если установить отношение R24/R37 большим или равным единице. Выражения для выходного напряжения блока записи и считывания демонстрируют согласованность выходных уровней блока записи и считывания с уровнями элемента

памяти во всех режимах работы ЗУ. Это обеспечено благодаря тому, что при формировании выходных напряжений в устройстве учитывается изменение параметров ячеек памяти ЗУ в данных физических условиях.

Таким образом, использование предлагаемого парметрического источника позволяет повысить надежность работы запоминающего устройства в условиях воздействия эксплуатационных факторов и отклонений технологических параметров в широких пределах.

Формула изобретения 1. Параметрический источник опорного напряжения для запоминающего устройства, содержащий источник тока, нагрузочный транзистор, эмиттер которого соединен с: первым выводом источника тока, первый резистор смещения, первый вывод которого подключен к базе нагрузочного транзистора, второй резистор смещения, первый вывод которого соединен с коллектором нагрузочного транзистора, элемент шунтирования в виде диода, катод которого соединен с коллектором нагрузочного транзистора первый согласующий транзистор, третий резистор смещения, первый вывод которого подключен к базе первого согласующего транзистора, второй согласующий транзистор, база которого соединена с вторым выводом третьего резистора смещения, компенсирующий резистор, первый вывод которого соединен с базой второго согласующего транзистора, а второй вывод соединен с коллекторами первого и второго согласующих транзисторов и является входом подключения нулевого потенциала источника питания параметрического

источника опорного напряжения, переключающий транзистор, эмиттер которого соединен с вторым выводом источника тока и является входом подключения напряжения

источника питания параметрического ис- точника опорного напряжения, третий согласующий транзистор и токозадающий резистор, отличающийся тем, что, с целью повышения надежности работы запоминающего устройства за счет более полной компенсации влияния изменения температуры и величины напряжения питания, параметрический источник опорного напряжения содержит четвертый согласующий транзистор, база которого соединена с эмиттером второго и коллектором третьего сбгласующих транзисторов, коллектор подключен к первому выводу компенсирующе- то резистора, а эмиттер соединен с

коллектором переключающего транзистора и является выходом параметрического источника опорного напряжения, эмиттер первого согласующего транзистора соединен с анодом шунтирующего диода и вторыми выводами первого и второго резисторов смещения, база третьего согласующего транзистора подключена к коллектору нагрузочного транзистора, а эмиттер соединен с базой переключающего транзистора и

с первым выводом токозадающего резистора, второй вывод которого соединен с эмиттером переключающего транзистора.

возбуждения автоколебаний, в него введен стабилизирующий элемент в виде конденсатора, первый вывод которого подключен к первому, а второй - к второму выводам компенсирующего резистора.

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Патент США N; 4099070, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-10—Подача