(54) ОДНОРОДНАЯ СТРУКТУРА ДЛЯ «ФУНКЦИЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Тестопригодное логическое устройство | 1986 |

|

SU1451695A1 |

| СПОСОБ ТЕСТОПРИГОДНОСТИ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2011 |

|

RU2497182C2 |

| Программируемое логическое устройство | 1987 |

|

SU1444892A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1474671A1 |

| Устройство для обучения | 1987 |

|

SU1543438A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

| Однородная структура для реализации логических функций | 1974 |

|

SU498618A1 |

| Устройство для ввода в ЭВМ дискретных сигналов | 1990 |

|

SU1786481A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

Изо югение относится к вычислигепь)к ной технике и авгомагнке.

Известна однородная логическая структура для реализации логических фунюшй, содержащая магриду элементов, каждый из которых выполнен на последовательно соединенных полевых транзисторах, элементы неравнозначности и резисторы 1 .

Недостатками устройства являются низкое быстродействие и сложность.щ

Наиболее близкой по технической сущности к предлагаемой является однородная структура для реализации логических функций, содержащая триггер, матри- ., цу элементов неравнозначности, нвходы которых соединень с вертикальными и диагональными щинами, а выходы с элементами И, на входы которых подаются управляющие сигналы Г2 .20

Недостатками известного устройства являюихзя низкое быстродействие и использование брльщого числа элементов неравнозначности.

2

Целью изЬфетения является упрощение и повышенке быстродействия.

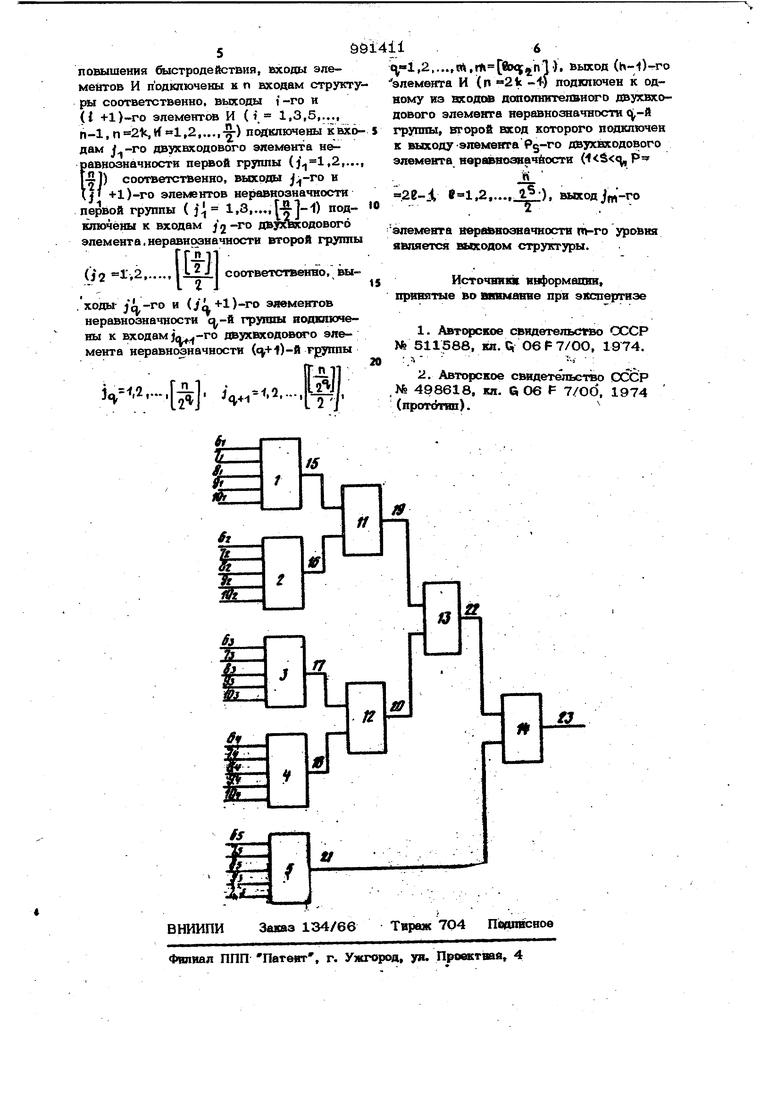

Поставленная цель достигается тем, что в однородной-структуре для реализации логических функций, содержащей элементы И в неравнозначности, входы . элементов И подключены к п входам структуры соответственно, вьрсоды i -го к ( i + 4)-РО элементов И ( i 1,3,5,..., n-lfH 2,1, Х 1,2,....,-) подключены к входам |л-го двухвходового элемента неравнозначности первой группы (j 1,2,..., Г- 1) с оответственно, выходы jj| -го и (I Jj+1)-го элементов неравнозначности первой группы (ji- 1,3,..., 5 подключены к входам двухвходового элемента неравнозначности

(Ш|)

второй группы ( J2 1

соI 2 J

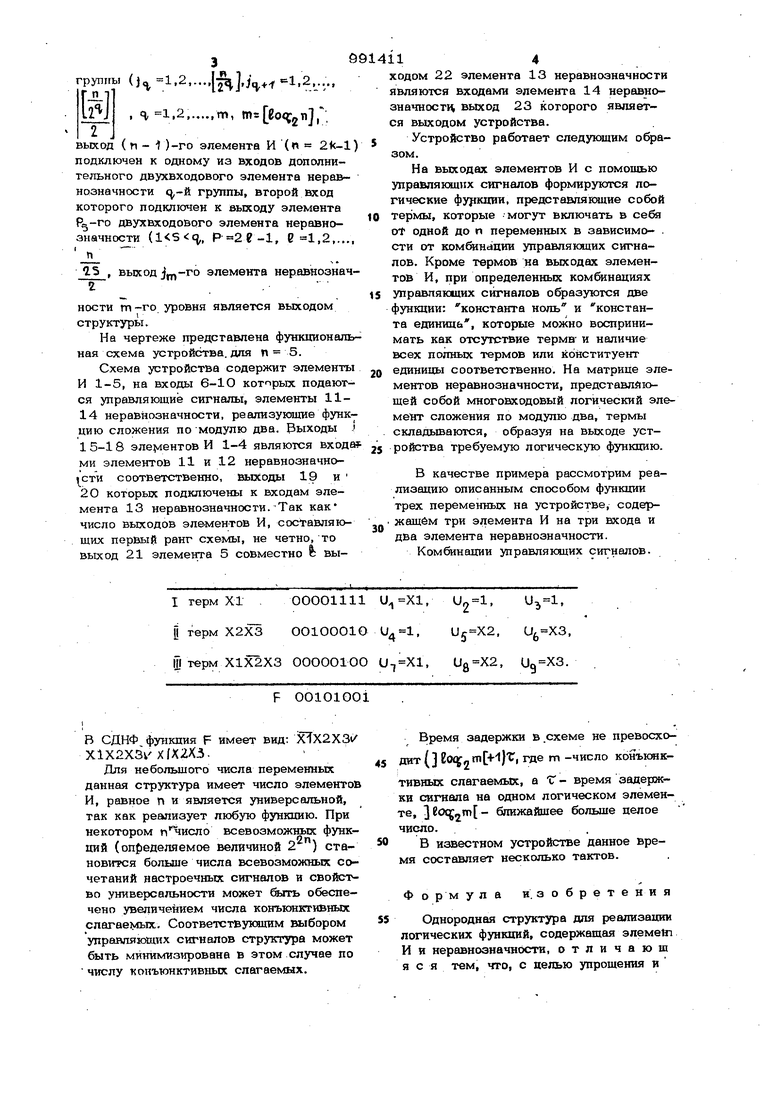

ответственно, выходы Оа 1)-го элементов неравнозначности -и группы подключены к входам двухвходового элемента нерав.нрзначности ()-й 3 группы (,2,...,,,2,..,, % 1.2,.,..,m, ,, выход (м - ) )-го элемента И (п 2 подключен к одному из входов дополнительного двухвходового элемента неравнозначности (,-й группы, второй вход которого подключен к выходу элемента двухвходового элемента неравнозначности , , ,2,.. 15 , выxoдj -гo элемента неравнозна 2, ности m -го уровня является выходом структуры. На чертеже представлена функционал ная схема устройства, для п 5. Схема устройства содержит элемент И 1-5, на входы 6-1О которых подают ся управляющие сигналы, элементы 1114 неравнозначности, реализующие функ цию сложения по модулю два. Рыходы 1 5-18 эле 1ентов И 1-4 являются вход ми элементов 11 и 12 неравнозначно{сти соответственно, выходы 19 и 2О которых подключены к входам элемента 13 неравнозначности.Так как число выходов элементов И, составляющих первый ранг схемы, не четно, то выход 21 элемента 5 совместно I: выI герм XIОООО1И1 ,,,1,

I терм X2X3 ОО1ОО01О ,,,

Ш терм Xl5C2X3 ООООО1ОО ,,.

F OOlOlOOi

В СДНФ функция F имеет вид: X7X2X3v X1X2X3VXfX2X3.

Для неболылого числа переменных данная структура имеет число элементов И, равное п и является универсальной, так как реализует любую функ1шю. При некотором всевозможных функций (оп{)еделяемое величиной 2 ) становится больше числа всевозможных сочетаний настроечных сигналов и свойство универсальности может быть обеспечено увеличением числа конъюнктивных слагаемых. Соответствующим выбором управляющих сигналов структура может быть минимизирована в этом .случае по числу конъюнктивных слагаемых.

Время задержки в .схеме не превосходит ( В Х{:„т -И)С, где m -число конъюнктивных слагаемьгх, а Т- время задержки сигнала на одном логическом элементе, 3eoqj, ближайшее больше целое число.

В и естном устройстве данное время составляет несколько тактов.

Формула и. зобретения

Однородная структура для реализации логических функций, содержащая элемеш И и неравнозначности, отличают я с я тем, что, с целью упрощения и l4 2 элемента 13 неравнозначности являются входами элемента 14 неравнозначности вькод 23 которого является выходом устройства. Устройство работает следующим образом. На выходах элементов И с помощью управляющих сигналов формируются логические фуркдии, представляющие собой термы, которые могут включать в себя от одной до п переменных в зависимо- . сти от комбинации управляющих сигналов. Кроме термов на выходах элементов И, при определенных комбинациях управляющих сигналов образуются две функции: константа ноль и константа единица, которые можно воспринимать как отсутствие терма- и наличие всех полных термов или конституэнт единицы соответственно. На матрице элементов неравнозначности, представляющей собой многоЁкодовый логический элемент сложения по модулю два, термы складьтаются, образуя на выходе устройства требуемую логическую функцию, В качестве примера рассмотрим реализацию описанным способом функции трех переменных на устройстве, содержащем три элемента И на три входа и два элемента неравнозначности. Комбинации управлякщих сигналов.

Авторы

Даты

1983-01-23—Публикация

1981-07-27—Подача