(21)4252426/24-24

(22)29.05.87

(46) 15.12.88. Бюл, № 46

(71)Харьковский авиационный.- инсти- тут им., Н.Е.Жуковского

(72)В.ПоУлитенко, В.Я.Жихарев, Г.Н.Тимонькин, В.С.Харчёнко, С.Н.Тка- ченк о и С.Ф.Тюрин

(53) 681.327.66 (088.8) (56) Баранов С.И., Баркалов А.А. Применение программируемых логических матриц в цифровой технике. - За- рубежная радиоэлектроника, 1982, № 6, с. 67-68.

Авторское свидетельство СССР № 1267964, кл. G 11 С 17/00, iG 06 F 7/00, 1983.

(54) ПРОГРАММИРУЕМОЕ ЛОШМЕСКОЕ УСТРОЙСТВО

(57) Изобретение относится к вычислительной технике и может быть использовано для вычисления систем

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

(Л

булевых функций. Целью изобретения является повышение быстродействия устройства в режиме записи. Для достижения этой цели в устройство, содержащее элементы И 1, элементы ИЛИ 5, три группы 2,3,4 D-триг- геров и две группы элементов 6,7 с Тремя состояниями выходов, введена

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем булевых функций.

Целью изобретения является повышение быстродействия устройства в резш- ме записи за счет того, что программирование элементов И и ИЛИ устройст ва производится одновременно, .

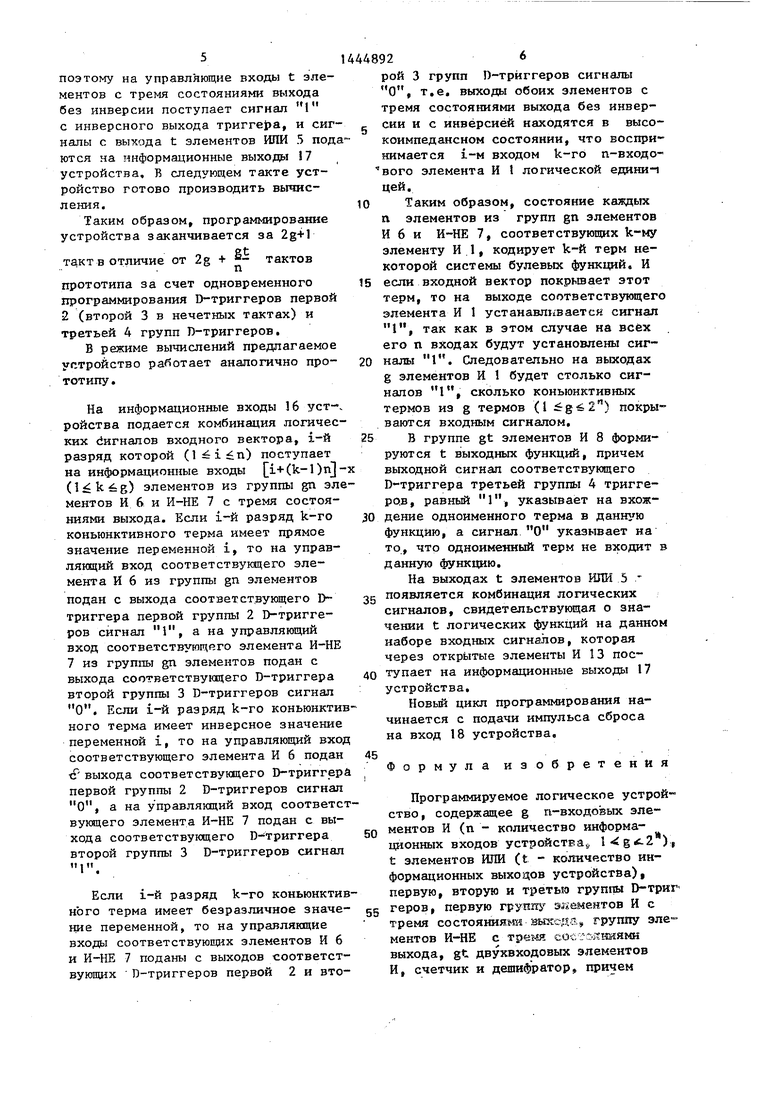

Функциональная схема устройства приведена на чертеже.

Символы п, g и t используются для обозначения соответственно количества входов, термов и выходов уст- ройства.

Программируемое логическое устройство содержит g п-входовых элементов И 1, первую 2, вторую 3 и третью 4 группы В-триггеров, t элементов ИЛИ 5, пер- вую группу из gn элементов И 6 с тремя состояниями выхода, группу gn элементов И-НЕ 7 с тремя состояниями выхода, gt двухвходовых элементов И 8, счетчик 9 с коэффициентом пе- ресчета 2g+l, дешифратор 10, первый 11 и второй 12 RS-триггеры, вторую группу из t элементов И 13 с тремя состояниями выхода, третий RS-триггер 14, дополнительный эле- мент ИЛИ 15, информационные входы 16 разрядностью п, информационные выходы 17 разрядностью t, вход 18 сброса, тактовьй вход 19, выход 20 индикации программирования элементов ИЛИ, выход 21 индикации программирования элементов И.

Первая группа 2 D-триггеров предназначена для приема и хранения информационных сигналов программирова- ния и подачи их на входы управления вторые, входы соответствующих элементов И с тремя состояниями вытретья группа элементов 13 с тремя состояниями выходов. Это позволило использовать для программирования не только информационные входы, но , и информационные выходы, и програм- мировать элементы И и ИЛИ одновременно. 1 ил.

хода. Вторая группа 3 D-триггеров предназначена для приема и хранения информационных сигналов программирования и подачи их на входы управления соответствуняцих элементов И-НЕ с тремя состояниями выхода. Третья группа 4 D-триггеров предназначена дпя приема с информационных выходов устройства и храиения информационных сигналов программирования и подачи их на входы управления элементов И 8 второй группы. I

При отсутствии разрешающего сигнала на управляющем (втором) входе выходы соответствующего элемента с тремя состояниями выхода находятся с высокоимпедансном состоянии.

Счетчик 9 с коэффициентом пересчета 2g+l предназначен для формирования по счетным сигналам, поступающим с тактового входа 19 устройства, сигналов для управления дешифратором 10 и подачи импульса со своего выхода переполнения на вход установки второго триггера 12.

Дешифратор 10 имеет 2g+t выход (с нулевого по 2g-й) и предназначен для формирования сигналов синхронизации для первой, второй и третьей групп 2-4 D-триггеров (выходы с первого по 2§-й), а нулевой выход предназначен для установки третьего триггера 14,

Первый RS-триггер 11 предназначен для формирования и подачи на вход 20 устройства сигнала по окончании программирования D-тркггеров третьей группы 4 по (g+l)-My импульсу счетчика 9. При этом установка триггера 1I происзфдит при изменении состояния g-го выхода дегаифратора с О

И

на 1

Второй RS-триггер 12 предназначен для формирования и подачи на выход 21 устройства сигнала по окон- чсанш; нрсграмг-мрования D-триггеров первой и второй групп 2 и 3 по (2g4-l)-My счетному импульсу счетчика 9. При этом установка триггера происходит по сигналу переполнения счетчика 9 с коэффициентом пересчет 2g-H.

Вторая группа элементов И 13 с тремя состояниями выхода предназна- передачи на информационные вьгходы устройства выходных сигналов с элементов ИЛИ 5 по разрешанлцему сигналу на их входах управления и для перевода своих выходов и высоко- импедансное состояние при снятии с их управляющих (вторых) входов разрешающего сигнала, причем разреша гаций сигнал поступает с инверсного выхода третьего триггера 14, I

Вход 18 устройства предназначен

для приема сигнала сброса D-тригге- ров первой 2, второй 3| третьей 4 групп, первого 11, второго 12 и третьего 14 RS-триггербв и счетчика 9. Вход 19 устройства предназначен для приема тактовых сигналов программирования. Выход 20 устройства

, является вторым выходом управления, свидетельствующим о том, что программирование элементов ИЛИ закончено, &1ХОД 21 устройства является первым выходом управления, свидетельствующим о том, что программирование элементов И и, следовательно, устройства в целом закончено.

Программируемое логическое устройство может работать в двух режимах: программирования и вычислений,

В режиме программирования (или записи) устройство работает следующи образом,

В исходном состоянии D-триггеры первой - третьей групп 2-4, ElS-триг- геры 1,2 514 и счетчик 9 обнулены по входу 18 устройства. На входы управления групп элементов И 6,7 с тремя состояниями выхода поданы сигналы О, и их выходы находятся в вы сокоимпедансном состоянии,

По nepEOi.y импульсу, поступающему на вход 19 устройства, счетчик 9 с коэффициентом пересчета 2g-f-l переходит в первое состояние и на нулевом выходе дешифратора 10 появляется сигнал 1, Третий RS-триггер 14 устанавливается в состояние 1, а на его инверсном выходе устанавливается сигнал О, Поэтому на управляющих . входах t элементов И 1 3 с тремя состояниями выхода устанавливаются также 0 уровни О, и их выходы переводятся в высокоимпедансное состояние. По второму тактовому импульсу на информационные входы 16 устройства подается комбинация логических сигна- 5 лов программирования первых п D-триггеров из первой группы 2 D-триггеров, а на информационные выходы 17 устройства подается комбинация логических сигналов программирования 0 первых t D-триггеров из третьей группы 4 D-триггеров, которые заносятся в соответствующие D-триггеры по переднему фронту сигнала на первом выходе дешифратора 10, По третьему 5 тактовому импульсу на информационные входы 16 устройства подается комбинация логических сигналов программирования первых п D-триггеров из второй группы 3 D-триггерОБ, а на 0 информационные выходы 17 устройства подается комбинация логических сигналов программирования вторых t D-триггеров из третьей группы 4 D-триггеров, которая заносится в 2 .соответствующие D-триггеры по.(переднему фронту сигнала на втором выходе; дешифратора 10, Далее процесс прог- , раммирования продолжается аналогично. По ( )-му импульсу на тактовом 0 входе 19 первый триггер 11 устанавливается в состояние 1 по входу установки, на который подается сигнал 1 с (g-t-l)-ro выхода дешифратора 10, На выходе 20 устройства уста- 5 навливается сигнал 1, что свидетельствует об окончании программирования элементов ИЛИ,

По (2g+l)-My импульсу на входе 19 второй триггер 12 устанавливает- g ся в состояние 1 по входу установки, на который подается сигнал 1 с выхода переполнения счетчика 9, Поэтому на выходе 21 устройства

55

устанавливается сигнал 1 , что свидетельствует об окончании программирования элементов И и выходных сигналов. Сигнал 1 с выхода триггера 12 по первому входу элемента ИЛИ 15 обнуляет третий триггер 14,

такт в отличие от 2g +

тактов

поэтому на управляющие входы t элементов с тремя состояниями выхода без инверсии поступает сигнал 1 с инверсного выхода триггера, и сигналы с выхода t элементов Ш1И 5 подаются на информационные выходы 17 устройства, В следующем такте устройство готово производить вычисления.

Таким образом, программирование устройства заканчивается за 2g+l

gt n

прототипа за счет одновременного программирования D-триггеров первой 2 (второй 3 в нечетных тактах) и третьей 4 групп П-триггеров,

В режиме вычислений предпагаемое устройство работает аналогично прототипу .

На информационные входы 16 уст-. ройства подается комбинация логических Сигналов входного вектора, i-й разряд которой () поступает на информационные входы i+(k-l)n|() элементов из группы gn элементов И 6 и И-НЕ 7 с тремя состояниями выхода. Если i-й разряд k-ro конъюнктивного терма имеет прямое значение переменной i, то на управ- лянщий вход соответствугадего элемента И 6 из группы gn элементов подан с выхода соответствующего триггера первой группы 2 D-триггеров сигнал 1, а на управляющий вход соответствующего элемента И-НЕ 7 из группы gn элементов подан с выхода соответствующего D-триггера второй группы 3 D-триггеров сигнал О. Если 1-й разряд k-ro конъюнктивного терма имеет инверсное значение переменной i, то на управляющий вход соответствующего элемента И 6 подан t выхода соответствующего D-триггера первой группы 2 D-триггеров сигнал О, а на управляющий вход соответствующего элемента И-НЕ 7 подан с выхода соответствующего D-триггера

второй группы 3 D-триггеров сигнал

n I ti I

Если i-й разряд k-ro конъюнктивного терма имеет безразличное значение переменной, то на управляющие входы соответствующих элементов И 6 и И-НЕ 7 поданы с выходов соответствующих D-триггеров первой 2 и вто

444892 рой О

10

ts

20

25

3 групп П-трйггеров сигналы

, т.е. выходы обоих элементов с тремя состояниями выхода без инверсии и с инверсией находятся в высо- коимпедансном состоянии, что воспринимается i-M входом k-rb п-входо- вого элемента И 1 логической едини-i цей.

Таким образом, состояние каладых n элементов из групп gn элементов И 6 и И-НЕ 7, соответствующих k-му элементу И 1, кодирует k-й терм некоторой системы булевых функций. И если входной вектор покрьшает этот терм, то на выходе соответствукяцего элемента И 1 устанавливается сигнал 1, так как в этом случае на всех его n входах будут установлены сигналы 1. Следовательно на выходах g элементов И 1 будет столъко сигналов I, сколъко конъюнктивных термов из g термов (1 5g62) покрываются входным сигналом.

В группе gt элементов И 8 формируются t выходных функций, причем выходной сигнал соответствующего D-триггера третьей группы 4 триггеров, равный 1, указывает на вхождение одноименного терма в даннз ю функцию, а сигнал О указывает на то, что одноименный терм не входит в данную функцию.

На выходах t элементов ИЛИ 5 появляется комбинация логических сигналов, свидетелъствующая о значении t логических функций на данном наборе входных сигналов, которая через открытые элементы И I3 пос- 40 тупает на информационные выходы 17 устройства.

Новый цикл программирования начинается с подачи импульса сброса на вход 18 устройства.

Формула изобретения

Программируемое логическое устройство, содержащее g п-входовых элементов И (п - количество информационных входов устройства, l-igtf-Z ), t элементов ИЛИ (t количество информационных выходов устройства)I первую, вторую и третью грушты 0 триГ 55 геров, первую элементов И с тремя состояниями выхскй группу эле ментов И-НЕ с тремя сосг - йкиямк выхода, gt двухвходовых элементов И, счетчик н дешифратор, причем

30

35

50

D-входы i+(k-l ) П-триггеров первой и второй групп, первые входы соответствукщих элементов И с тремя состояниями выхйда первой группы и первые входы элементов И-НЕ с тремя состояниями выхода (1 1бп} 1 ) являются i-M информационным входом устройства, выходы П-триггеров первой группы соединены с вторы- ьш входами соответствующих элементов И с тремя состояниями выхода первой группы, а выходы D-триггеров второй группы - с вторыми входами соответствующих элементов И-НЕ с тре мя состояниями выхода, выходы которых соединезлл с выходами соответствующих элементов И с тремя состояниями выхода первой группы, С-входы (k-On+ij-x D-триггеров первой груп пы соединены с k-м нечетным выходом дешифратора, а С-входы одноименных D-триггеров второй группы с k-м четным выходом дешифратора, выходы C(k-l ) п+ -X элементов И с тремя состояниями выхода первой группы соединены с входами k-ro п-вх6дового элемен- та И, выход которого соединен с первыми входами k-f(j-l)g3-x двухвхо- довых элементов И (), вторые входы которых соединены с выходами соответствующих D-триггеров третьей группы, а выходы - с k-м входом j-x элементов ИЛИ, информационные выходы счетчика соединены с входами дешифратора, а счетный вход счетчика являет- ся тактовым входом устройства, от:

личающееся тем, что, с целью повьппения быстродействия устройства в режиме записи, в него вве- g дены первый, второй и третий RS-триг- геры, дополнительный элемент ИЛИ и вторая группа элементов И с тремя состояниями выхода, первые входы которых соединены с выходами соотбет10 ствукщих элементов ИЛИ, а вторые входы - с инверсным выходом третьего RS-триггера, S-вход которого соеди-. нен с нулевым выходом дешифратора а R-вход - с выходом дополнительного

15 элемента ИЛИ, выход j-ro элемента И с тремя состояниями выхода второй группы соединен с D- вxoдaми fk+Cj- l)gj-x D-триггеров третьей группы и является соответствующим информаци- 20 онным выходом устройства, р-й выход дешифратора () соединен с С-входами (p-l)t+j1-x D-триггеров третьей группы S-входы первого и второго RS-триггёров соединены соот25 ветственно с g-м выводом дешифратора и с выходом переполнения счетчика, выход первого RS-триггера является выходом индикации программирования элементов ИЛИ устройства, вы30 ход второго RS-триггера соединен с первым входом дополнительного элемента ИЛИ и является выходом индикации программирования элементов И устройства, R-входы D и RS-триггеров

35 и второй вход дополнительного элемента ИЛИ являются входом сброса устройства.

Авторы

Даты

1988-12-15—Публикация

1987-05-29—Подача