Тма. 1

SM

ментов И (ГПЭИ) 16.1-16.В, злемент сложения по модулю 2 (ЭМСМ2) 17, вход расширения (ВДР) 18, входы-выходы данных ВДВД 19, входы управления (ВДУ) 20 и 21, информационный вход (ИРВ) 22, входы расширения (ВДР) 23 и 24, входы (ВД) 25 и 26, выход расширения (ВДР) 27. ИСХ ЭМИ (3) ЭМИ (2) ШНФ(1) ЭМИЛИ (10) ВДУ (20). ИСХ ЭМИЛИ (10) ЭМИ (2). ИСХ ВДУ (21) ЭМИЛИ (21) ЭМИ (3) РСТ(8). ИСХ ШНФ (1) ВДВД (19). ИСХ PC

(8) ШНФ (1). ИСХ PC (8) ГПЭИ (14.1, ) ЭМИ (4) ГПЭИ-НЕ (15.1, 15.В) PC (8). ИСХ ЭМСМ2 (17) ЭМИ (6) ЭМИЛИ (12) ШНф (1) ВДР (27). ИСХ ВДР (23) ЭМИЛИ (11) эМи

(4) ЭМИ (5) ЭМИЛИ (12). ИСХ PC (9) PCi (8) PC (9) ПГЭИ (16.1,16.В) ЭМИ (4). ИСХГПЭИ (16.1, 16.В) ЭМСМ2 (17) ЭМИ (7) PC (9) ЭМИЛИ (11). ИСХ PC (9) ЭМИЛИ (13) ЭМИ

(5). ИСХ PC (9) ЭМИ (6) ВД (26). ИСХ ЭМИ- . ЛИ (13) ВД (25). 4 ил.;.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

Использование: программно-аппаратное вычисление булевых функций. Цель: расширение функциональных возможностей за счёт выполнения операций конъюнкции и сложения по модулю 2 входных данных при их введений в ЭВМ, Сущность изобретения: устройство содержит: шинный формирователь(ШНФ) 1, элементы И (ЭМИ) 2-7, регистры (PC) 8 и 9, элементы ИЛИ (ЭМИЛИ) 10-13, группу элементов И стремя состояниями на выходе (ГПЭИ) 14.1-14.В, где В - разрядность входного сигнала, группу элементов И-НЕ с тремя состояниями на выходе (ГПЭИ-НЕ) 15.1-15,В, группу элеI- 9

Изобретение относится к вычислительной технике и может быть использовано для программно-аппаратного вычисления булевых функций.

Известно устройство двунаправленного ввода-вывода информации, состоящее из дешифратора адреса, шинного формирователя и схем И.

Недостатком такого устройства являются низкие быстродействие и функциональные возможности.

Известно также устройство, состоящее из дешифратора адреса, шинного формирователя, регистра, программируемой логической матрицы, элементов И и ИЛИ.

Недостатком такого устройства являются низкие быстродействие и функциональные возможности.

Наиболее близким по технической сущности является устройство для ввода в мик- роЭВМ дискретных сигналов, содержащее дешифратор адреса, три элемента И, элемент ИЛИ, шинный формирователь, ре;- гистр, группу элементов И, группу элементов И-НЕ.

Недостатком такого устройства являются низкие быстродействие и функциональные возможности.

Целью изобретения является расширение функциональных возможностей за счет выполнения операций конъюнкции и сложения по модулю 2 входных данных при их введении в ЭВМ.

Поставленная цель достигается тем, что в известное устройство для ввода в ЭВМ дискретных сигналов, содержащее шинный формирователь, с первого по третий элементы И, первый регистр, первый элемент ИЛИ, группу элементов И с тремя состояниями на выходе и группу элементов И-НЕ с тремя состояниями на выходе, первый вход второго элемента И соединен с первым входом первого элемента И, выход которого соединен со входом выборки шинного формирователя, выход задания направления

передачи которого соединен с первым входом первого элемента ИЛИ и является йхо- дом команды ввода устройства, первого элемента ИЛИ соединен со вторым

входом первого элемента И, вход команды ввода данных в ЭВМ устройства соедийен со вторыми входами первого элемента ИЛИ и второго элемента И, выход которого cjoe- динен со входом синхронизации перйого

регистра, вход-выход шинного формирфва- теля является информационным входом-выходом устройства, группа информационйых входом первого регистра соединена сфот- ветственно с группой выходов шинн ого

формирователя, выход нечетных разрядов первого регистра соединены со входами отключения соответствующих элементов И с тремя состояниями на выходе группы, выход каждого из которых соединен с соотфетствующим входом третьего элемента И и выходом соответствующего элемента И-МЕ с тремя состояниями на выходе группы, вход отключения которого соединен с выходом соответствующего нечетного разряда

первого регистра, согласно изобретению введены четвертый и пятый элементы И, со второго по четвертый элементы ИЛИ, группа элементов И и элемент сложения по модулю 2, выход которого соединен с первым

входом пятого элемента И, выход которого соединен с первым входом третьего элейен- та ИЛИ, выход которого соединен с информационным входом шинного формирователя и является выходом расширения устройс|ва,

первый вход задания режима устройства соединен с первым входом второго элемента ИЛИ, выход которого соединен с (2К+|)-м входом третьего элемента И, где К - разрядность входного сигнала, выход которогр;соединен с первым входом четвертого элемента И, выход которого соединен со вторым входом третьего элемента и|ш, вход синхронизации второго регистра cjoe- динен со входом синхронизации первого

регистра, выходы которого соединены с соответствующими информационными входами второго регистра, с первого по К-й выходы которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены соответственно с первого по К-й входами третьего элемента И, выходы элементов И группы соединены с соответствующими входами элемента сложения .по модулю 2, (К+1)-й вход которого соединен с (К+1)-й разряд выхода которого соединен со вторым входом второго элемента ИЛИ, (К+2)-ой разряд выхода второго регистра соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, (К+3)-й разряд выхода второго регистра соединен со вторым входом пятого элемента И, второй вход которого является входом наращивания разрядности устройства, при вычислении суммы по модулю 2, вторые входы четвертого элемента ИЛИ и пятого элемента И являются соответственно входом наращивания разрядности устройства при вычислении конъюнкции и вторым входом задания режима устройства.

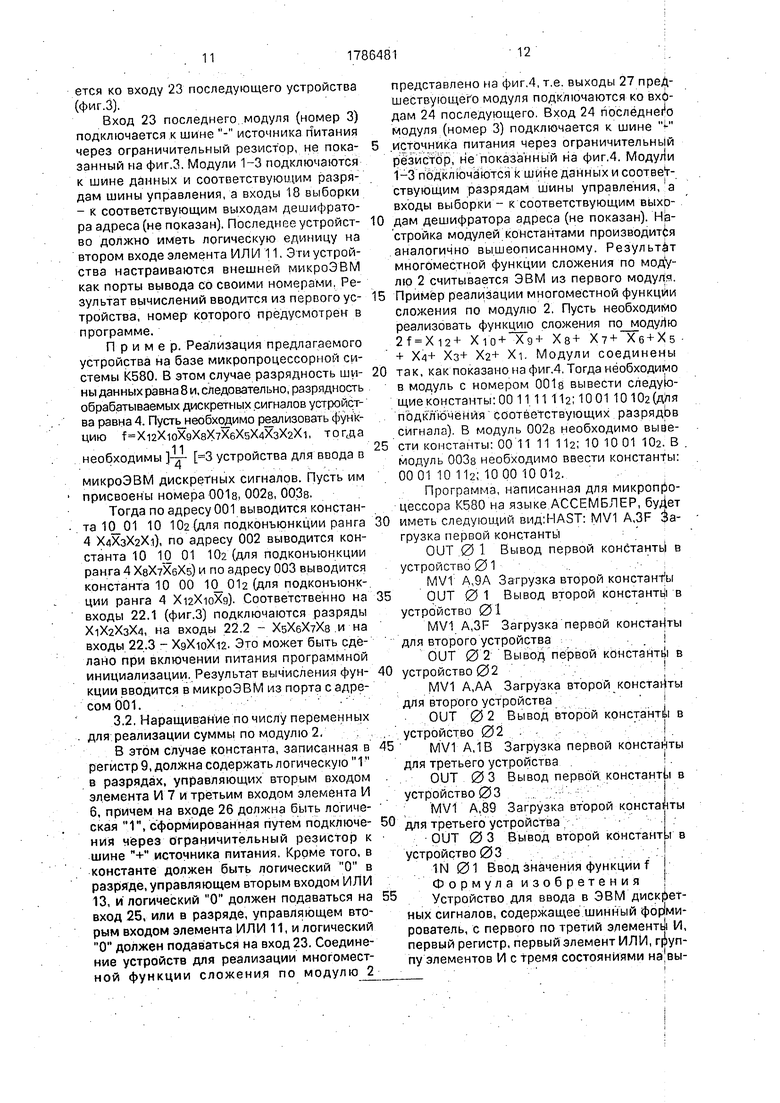

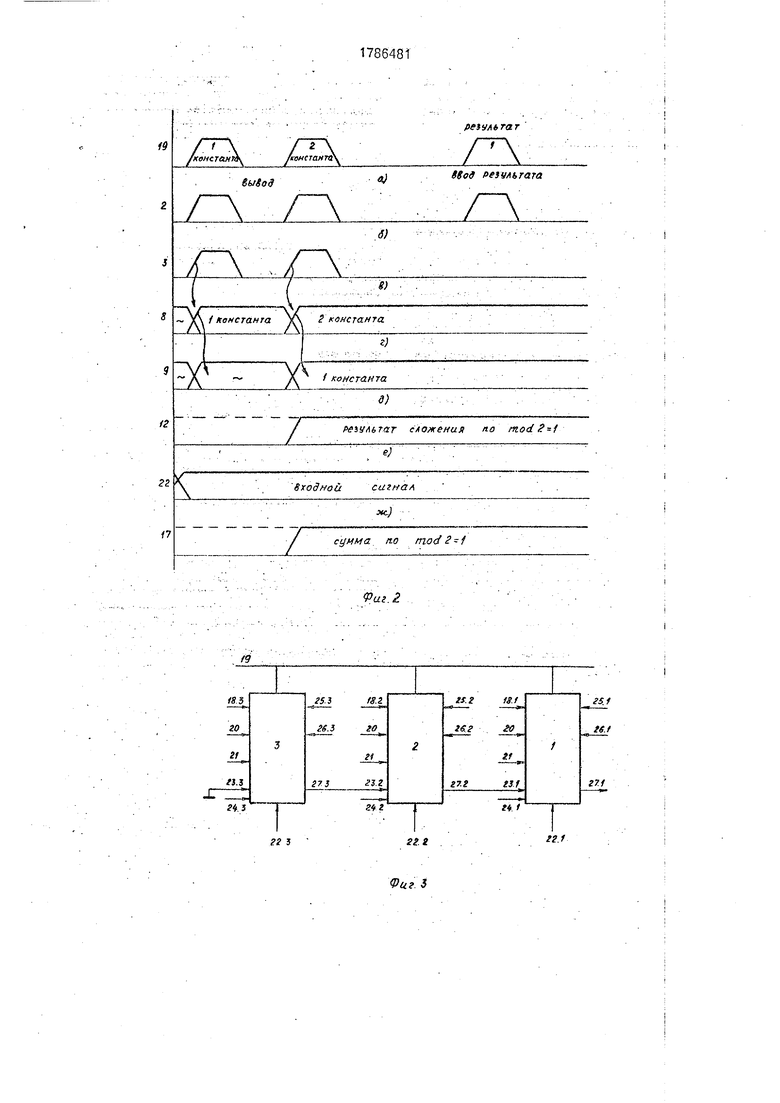

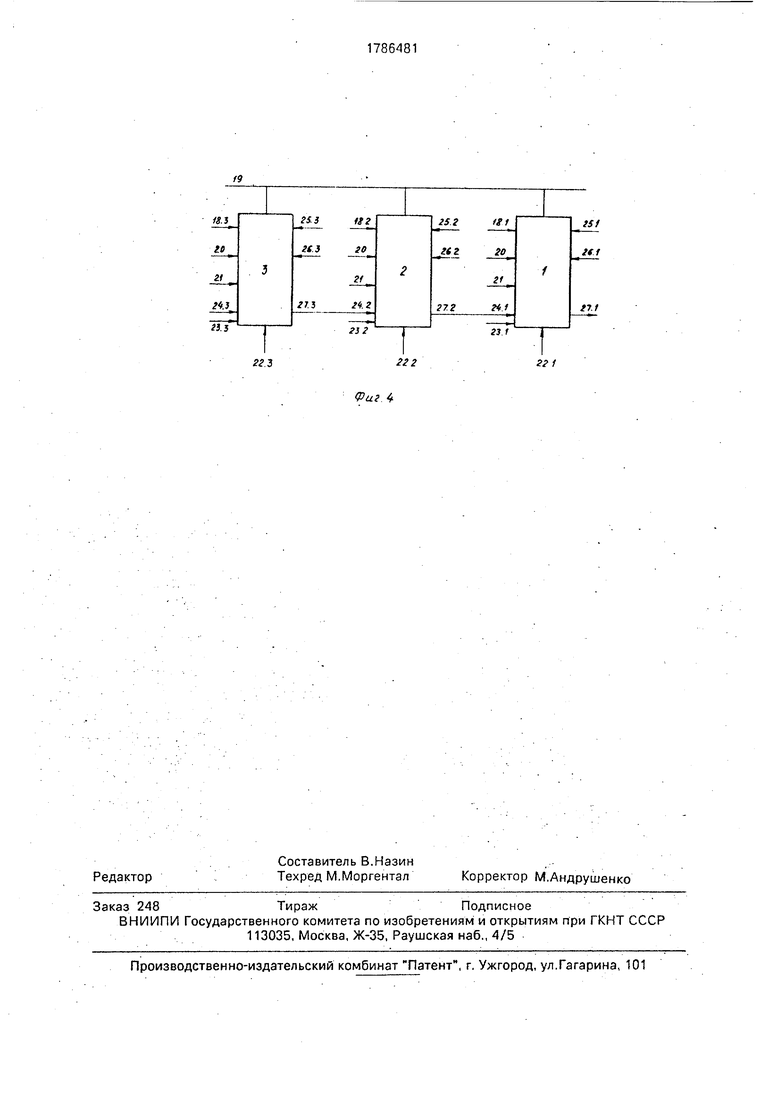

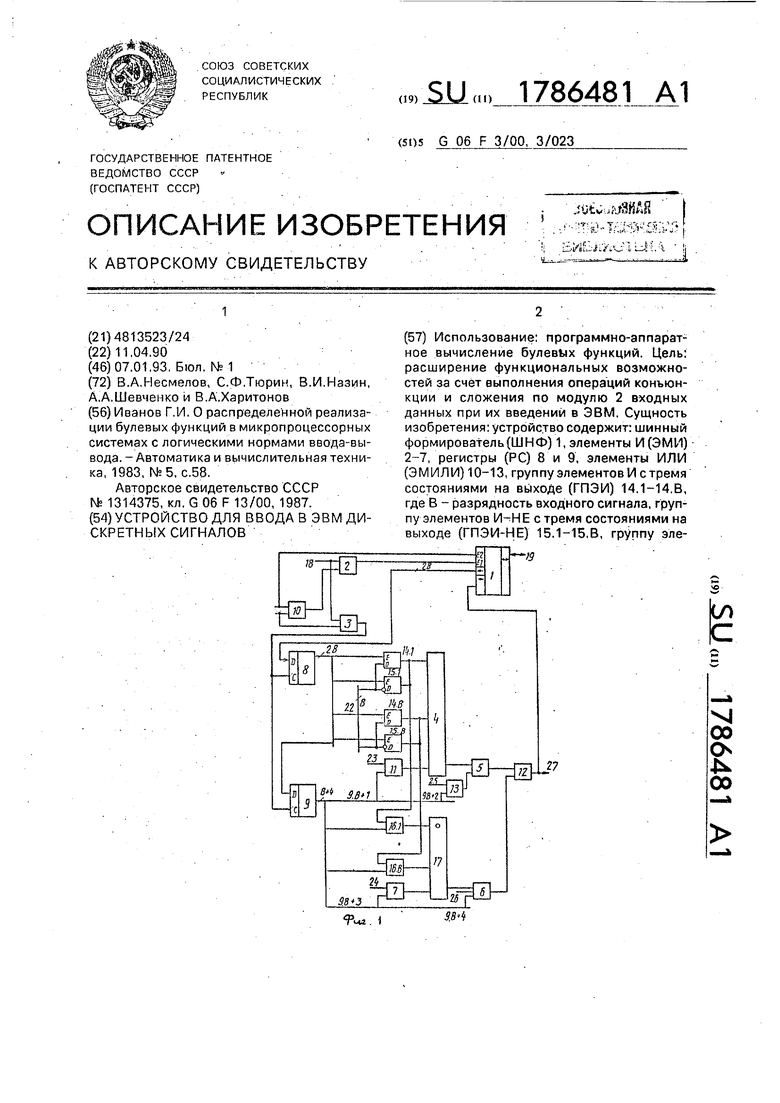

На фиг.1 изображена функциональная схема предлагаемого устройства: на фиг.2 - временные диаграммы работы устройства при реализации режима сложения по модулю 2; на фиг.З - примеры структурной схемы секционного объединения трех устройств для ввода в ЭВМ дискретных сигналов для вычисления многоразрядных конъюнкций; на фиг.4 - пример структурной схемы секционного объединения трех устройств для ввода в ЭВМ дискретных с-игналов для реализации суммы по модулю 2.

Устройство для ввода в ЭВМ дискретных сигналов содержит шинный формирователь 1, элементы И 2-7, регистры 8 и 9, элементы ИЛИ 10-13, группу элементов И ,.14.1-14.В с тремя состояниями на выходе, где В - разрядность входного сигнала, группу элементов И-НЕ 15.1-15.В стремя состояниями на выходе, группу элементов И 16.1-16.В, элемент 17 сложения по модулю 2, вход 18 разрешения, входы-выходы 19, данных, входы 20 и 21 управления, информационные входы 22, входы 23 и 24 расширения, входы 25 и 26, выход 27 расширения.

Шинный формирователь 1 предназначен для усиления по мощности сигналов на входах-выходах 19 устройства при активизации входа выборки, а также для перевода своего входа-выхода в состояние высокого импеданса при неактивизации этого входа для отключения информационных входов- выходов 19 устройстве и может быть реализован, например, на микросхеме 589АП16.

0

5

0

5

0

5

0

5

0

5

Режим работы шинного формирователя 1 определяется уровнем сигнала на входе на- правления передачи.

Элемент И 2 предназначен для управления входом выборки шинного формирователя 1. Выход элемента И 2 возбуждается, если активированы вход 18 разрешения и выход элемента ИЛИ 10.

Элемент И 3 предназначен для управления синхровходами регистров 8 и 9.

Элемент И 4 предназначен для формирования значения конъюнктивного терма по значению выходов каждой пары элементов 14-15. Причем, когда выходы обеих элементов в паре находятся в высокоимпедансном состоянии, это воспринимается входом элемента И 4 как логическая 1.

Элемент И 5 предназначен для управления первым входом элемента ИЛИ 12 при учете результата локальных вычислений подконъюнкций.

Элемент И 6 предназначен для управления вторым входом элемента ИЛИ 12 при учете результата локальных вычислений суммы по модулю 2.

Элемент И 7 предназначен для управления (В+1)-м входом элемента 17 сложения по модулю 2 при учете результата вычислений суммы по модулю 2 в предшествующих секциях.

Регистр 8 предназначен для записи и временного хранения констант по синхроимпульсу, поступающему с выхода элемента И 3 и может быть реализован, например, на микросхемах 155ИР13, 589ИР12.

Регистр 9 предназначен для записи и временного хранения констант по синхроимпульсу, поступающему с выхода элемента И 3 и может быть реализован, например, аналогично регистру 8.

Элемент ИЛИ 10 предназначен для управления элементом И 2 в том случае, если активированы входы 20 или 21 устройства.

Элемент ИЛИ 11 предназначен для управления (В+1)-м входом элемента И 4 при учете результатов вычисления подконъюнкций в предыдущих секциях.

Элемент ИЛИ 12 предназначен для реализации логического сложения результатов вычисления конъюнкций и сложения по модулю 2 и управления входа шинного формирователя 1.

Элемент ИЛИ 13 предназначен для управления вторым входом элемента И 5 с целью реализации заданных режимов рабо- ты устройства при учете подконъюнкций.

Элементы И 14 с тремя состояниями на выходе без инверсии предназначены для идентификации прямого значения соответствующей переменной в конъюнктивном

терме. При этом активирован вход управления одного из элементов И 14. В противном случае выход элемента находится в высоко- имледансном состоянии и не влияет на работу элементов И 15.

Элементы И-НЕ 15 стремя состояниями на выходе предназначены для идентификации инверсного значения соответствующей переменной в конъюнктивном терме. При этом активирован вход.управления одного из элементов И-НЕ 15. В противном случае, выход элемента находится в высокоимпе- дансном состоянии и не влияет на работу элементов И 14.

Элементы И 16 предназначены для управления элементом 17 сложения по модулю 2.

Элемент 17 сложения по модулю 2 предназначен для получения суммы переменных по модулю 2 и может быть реализован, например, на микросхемах 561ЛП2, 564ЛП2 и др.

Вход 18 разрешения предназначен для активизации работы устройства.

Входы-выходы 19 предназначены для подключения шины данных внешней ЭВМ.

Вход 20 управления Чтение предназ- начен для подключения команды ввода внешней ЭВМ..

Вход 21 управления Запись предназначен для подключения команды вывода внешней ЭВМ..

Информационные входы 22 предназначены для подключ ения кома нды вывода внешней ЭВМ.. .

Вход 23 расширения предназначен для подключения выхода 27 предыдущего устройства с целью увеличения разрядности обрабатйваемШ дйскГр етных сигналов для наращивания по числу переменных конъюнкций.

Вход 24 расширения предназначен для подключения выхода 27 предыдущего устройства с целью увеличения разрядности обрабатываемых дискретных сигналов для наращивания по числу переменных при реализации суммы по модулю 2,

Вход 25 предназначен для управления элементом И 5 дли реализации заданных режимов работы устройства.

Вход 26 предназначен для управления элементов И 6 для реализации заданных режимов работы устройства.

Вход 27 расширения предназначен для реализации работы устройства в режиме разряда наращиваемой структуры.

17 Работа в вычисления конъюнкции..

Устройство работает следующим образом.

5

0

Вначале производится настройка или инициализация. При этом ЭВМ обращается к нему, как к порту вывода с фиксированнь м адресом. Активизируется вход 21 Запис

и вход 18 разрешения (фиг.1), активизируя выходы элемента ИЛИ 10, элементов И 2,3. Элемент И 2 подключает шинный формирователь 1 в режиме ввода с входов-выходбв 19 н.а входы данных регистра 8. Синхрон 0 зирующий импульс с выхода элемента И; 3 записывает код настройки, поступающий с шины данных ЭВМ через шинный формир о- ватель 1 в 2 В-разрядный регистр 8 (фиг.2,в), сигналы с выходов которого настраивают

5 элементы И и ИЛИ-НЕ 14.1-14.В, 15.1-15:6 так, что каждый разряд входного слова на входах 22 через каждую пару этих элементов может либо передаваться без инверсии (высОкоимпедансное состояние элементов

0 И 14), либо с инверсией (высокоимпедансное состояние элементов И-НЕ 15), либо г е- редачи не будет - безразличное состояние разряда входного сигнала (высокоимледа н- сное состояние обоих магистральных э/Je- ментов И 14 и 15). На выхода всех пар элементов ИЛИ-НЕ 14 и 15 устанавливаются активные уровни сигналов, если входной сигнал покрывается конъюнктивным т4р- мом, вычисляемым микропроцессорной системой, i

На входы 23 и 25 подаются сигналы логической 1, а на вход 26 - логического О, при этом активизируются выходы элементов ИЛИ 11 и 13 и запирается выход элемен5 та И 6. Это может быть произведено путем предварительного подключения входов 23, 25 к шине + источника питания через ограничительный резистор, а входа 26 - к ши|не - через ограничительный резистор в трм.

0 случае, если нет необходимости использования функции сложения по модулю 2 (тогда устройство работает аналогично прототи- . пу). Активный уровень сигнала с выхода . мента И 4 через элементы 5 и 12 ввОдитс)я в

5 ЭВМ по сигналу Чтение, который настраивает шинный формирователь 1 на ввод информации. Затем из ЭВМ выводится ||од настройки для .вычисления следующего

конъюнктивного терма, и процесс повто

эя- ется. ,,.-; -,-,-,.: ; ---.;--..-. . .

Если вычисленный терм 1, т.е. ЭВМ получает от устройства активный , то вычисленная функция 1 и ЭВМ выполняет соответствующие действия. . . L При изменении логических функций йе- няются коды настройки, которые записаны вмассиведанных(ОЗУилиПЗУ),ЭВМ, вычисляет новую систему логических функций. Пример. Вычислить логическую функцию

v d

.Коды настроек, которые выносятся в массив данных, будут иметь следующий вид:

10 10 10 002 Mi;00 00 00 Oh Mi; 00 01 00 002 Мз. Программа,.написанная для микропроцессора К580, на языке АССЕМБЛЕР будет иметь следующий вид:

РРА: LX1 Н, L TABL Инициализация памяти....

CLC: MOV A, M Взять маску К

OUT PORT 1 Программировать устройство маской К

1N PORT 1 Ввести значение терма

ORA А Установить флаги

INZ ZCLL Закончить вычисления, если терм 0

1NX Н, L Модифицировать память

SUB А Обнуление А

ADD M Проверка окончания данных

INZ CLC Вычислить очередной терм

ZCL1:MV1 С, 00 Вычисленный терм 0

IMP МО Переход на метку функция 0

ZCL2: MV1 С, 01 Вычисленная функция 1,

IMP M1 Переход на метку функция 1

TABL: DB А8,40,00 .

END

Здесь в исходных данных 00 - маркер .окончания таблицы данных.

. Таким образом, устройство работает аналогично работе прототипа.

В этом режиме на вход 25 подается сиг- нал логического нуля, а на вход 26 - логической единицы аналдгично вышеописанному (фиг.1). ЭВМ, обращаясь к устройству как к порту вывода, производит двукратную выдачу констант по адресу, активизирующему вход 18. При этом вначале константа записывается в регистр 8 (фиг.2, г) по заднему фронту синхроимпульса на выходе элементе 3 И (фиг.2, в), затем при выдаче второй константы первая переписывается в ре- гистр 9 (фиг.2,д), а вторая записывается в регистр 8 (фиг.2, г), т.к. входы синхрониза- дии регистров объединены. В первой константе используется В+4 разряда, где В - разрядность входа 22. Во второй константе используются 2 В разрядов, так как было описано выше. Вторая константа с выхода регистра 9 управляет группой элементов И 16, элементами ИЛИ 11 и 13, элементами И 6 и 7. Если нет необходимое™ расширения разрядности обрабатываемых дискретных сигналов, то на. второй вход элемента И 7 с выхода регистра 9 должен поступать логический нуль, а на второй вход элемента ИЛИ 11 - логическая 1.

На третий вход элемента И 6 для производства вычислений.толь ко по модулю 2 подается сигнал логической 1, а на второй вход элемента ИЛИ 13 -- сигнал логического О. На входы элементов И 16 группы подаются нули в том случае, если соответствующий разряд входного сигнала не участвует в образовании суммы по модулю 2. С целью вычисления суммы по модулю 2 от- инверсии входных сигналов должны быть с помощью константы в регистре 8 подключены соответствующие элементы И-НЕ 15 с тремя состояниями на выходе. При вычислении суммы по модулю 2 от инверсируемых значений входных разрядов должен быть подключен соответствующий элемент И 14 группы с тремя состояниями на выходе. Если разряд входного сигнала 22 не участвует в образовании суммы по модулю 2, то состояние соответствующих элементов И 14, И- НЕ 15 может быть произвольно (естественно, кроме запрещенного, когда одновременно подключены оба элемента). Тогда элемент 17 сложения по модулю 2 формирует сумму по модулю 2 (фиг.2,з) от заданных разрядов входного сигнала 22 (включая и заданные инверсии)(фиг.2,ж) и передает вычисленные значения через элемент 6 И и элемент 12 ИЛИ на вход 27 (фиг.2, е) и вход шинного формирователя 1 и по шине данных 19 (фиг.2, а)- во внешний микропроцессор.

В этом случае константа, выведенная в регистр 9, должна подавать логический О на второй вход элемента ИЛИ 11 (фиг.1). Кроме того, на третий вход элемента И 6 подается логический О для подключения формирования суммы по модулю 2, на второй вход элемента ИЛИ 13 подается логическая 1 для подключения элемента И 5. В этом случае настройка группы элементов И 14 и И-НЕ 15 аналогична режиму 1. Однако элемент И 4 формирует логическую только в том случае, если на вход 23 поступит логическая 1 с выхода 27 аналогичного устройства для ввода дискретных сигналов, настроенного на вычисление второй под- конъюнкции в том случае, если разрядности одного устройства не достаточно (естественно, подконъюнкция, вычисляемая первым устройством, также должна покрывать свою долю разрядов входных сигналов). Для вычисления многоразрядных конъюнкций устройства для ввода дискретных сигналов подключаются последовательно, т.е. выход 27 предшествующего устройства подключается ко входу 23 последующего устройства (фиг.З).

Вход 23 последнего, модуля (номер 3) подключается к шине - источника питания через ограничительный резистор, не показанный на фиг.З. Модули 1-3 подключаются к шине данных и соответствующим разрядам шины управления, а входы 18 выборки - к соответствующим выходам дешифратора адреса (не показан). Последнее устройство должно иметь логическую единицу на втором входе элемента ИЛИ 11, Эти устройства настраиваются внешней микроЭВМ как порты вывода со своими номерами. Результат вычислений вводится из первого устройства, номер которого предусмотрен в программе.

Пример. Реализация предлагаемого устройства на базе микропроцессорной системы К580. В этом случае разрядность шины данных равна 8 и, следовательно, разрядность обрабатываемых дискретных сигналов устройства равна 4. Пусть необходимо реализовать функцию 1 Х12ХюХ9Х8Х7ХбХ5Х4ХзХ2Х1, тогда

11 необходимы W- 3 устройства для ввода в

микроЭВМ дискретных сигналов. Пусть им присвоены номера Q01a, 002s, ООЗв.

Тогда по адресу 001 выводится константа 10 102(для подконъюнкции ранга 4 Х4ХзХ2Х1), по адресу 002 выводится константа 10 01 102 (для подконъюнкции ранга 4 XeXyXeXg) и по адресу 003 выводится константа 10 00 10 012 (для подкокыонк-. ции ранга 4 X12X10X9). Соответственно на входы 22.1 (фиг.З) подключаются разряды XiX2XaX4, на входы 22.2 - ХзХеХуХв .и на входы 22.3 - XgXioXia. Это может быть сделано при включении питания программной инициализации. Результат вычисления функции вводится в микроЭВМ из порта с адресом 001.

В этом случае константа, записанная в регистр 9, должна содержать логическую 1 в разрядах, управляющих вторым входом элемента И 7 и третьим входом элемента И 6, причем на входе 26 должна быть логическая 1, сформированная путем подключения через ограничительный резистор к шине + источника питания, Кроме того, в константе должен быть логический О в разряде, управляющем вторым входом ИЛИ 13, и логический О должен подаваться на вход 25, или в разряде, управляющем вторым входом элемента ИЛИ 11, и логический О должен подаваться на вход 23. Соединение устройств для реализации многоместной функции сложения по модулю 2

представлено на фиг.4, т.е. выходы 27 предшествующего модуля подключаются ко вхй- дам 24 последующего. Вход 24 последнего модуля (номер 3) подключается к шине .источника питания через ограничительный резистор, не показанный на фиг.4. Модули 1-3 подключаются k шине данных и соответствующим разрядам шины управления, а входы выборки - к соответствующим выхо- дам дешифратора адреса (не показан). Н|э- стройка модулей константами производится аналогично вышеописанному. Результат многоместной функции сложения по модУ- лю 2 считывается ЭВМ из первого модуля. Пример реализации многоместной функции сложения по модулю 2. Пусть необходимо реализовать функцию сложения по модулю 2f Xi2+ Хю+ Хд + Хв+ Х7 + + Х5 + Х4+ Хз+ Х2+ XL Модули соединены так, как показано на фиг.4, Тогда необходимо в модуль с номером 001s вывести следующие константы: 00 11.11 112; 1001 10102 (для подключения соответствующих разрядов сигнала). В модуль 002в необходимо выае- сти константы: 00 11 11 112; 10 1001 102. В модуль ООЗв необходимо ввести константны: 0001 10 1l2i.10.QO 10012.;

Программа, написанная для микропроцессора К580 на языке АССЕМБЛЕР, буДет иметь следующий вид:НАЗТ: MV1 A,3F ja- грузка первой константы:

OUT 0 1 Вывод первой константь) в устройство 01-.. -...-. ;

MV1 А,9А Загрузка второй константны OUT 0 1 Вывод второй константй в устройство 01

MV1 A,3F Загрузка первой константы для второго устройстваI

OUT 02 Вывод первой константф в устройство 02|

MV1 АДА Загрузка второй констайты для второго устройства i

OUT 02 Вывод второй KOHCTaHTili в устройство 02 . : . MV1 А.1В Загрузка первой константы для третьего устройства . .

OUT 0 3 Вывод первой констант в устройство 03 ;..;. ;;;/: :; .

MV1 А,89 Загрузка второй константы для третьего устройства I .

OUT 0 3 Вывод второй констант| г в устройство 03..,.. . .: 1.N 01 Ввод значения функции f I Формула изобретения | Устройство для ввода в ЭВМ дискретных сигналов, содержащее шинный формирователь, с первого по третий элементы И, первый регистр, первый элемент ИЛИ, группу элементов И с тремя состояниями на|выходе и группу элементов И-НЕ с тремя состояниями на выходе, первый вход второго элемента И соединен с первым входом первого элемента И, выход которого соединен с входом выборки шинного формирователя, выход задания направления передачи которого соединен с первым входом первого элемента ИЛИ и является входом команды ввода устройства, выход первого элемента ИЛИ соединен с вторым входом первого элемента И, вход команды ввода данных в ЭВМ устройства соединен с вторыми входами первого элемента ИЛИ и второго элемента И, выход которого соединен с входом синхронизации первого регистра,1 вход-вы- ход шинного формирователя является информационным входом-выходом устройства, группа информационных входов первого регистра соединена соответственно с группой выходов шинного формирователя, выходы нечетных разрядов первого регистра соединены с входами отключения соответствующих элементов И с тремя состояниями на выходе группы, выход каждого из которых соединен с соответствующим входом треть- его элемента И и выходом соответствующего элемента И-НЕ с тремя состояниями на выходе группы, вход отключения которого соединен с выходом соответствующего нечетного разряда первого регистра, отл и ч а- ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операций конъюнкции и сложение по модулю два входных данных при их введении в ЭВМ в него введены четвертый и пятый элементы И, с второго по четвертый элементы ИЛИ, группа элементов И и элемент сложения по модулю два, выход которого соединен с первым входом пятого элемента И, выход которого соединен с пер- вым входом третьего элемента ИЛИ, выход

которого соединен с информационным входом шинного формирователя и является вы- ходом расширения устройства, первый вход задания режима устройства соединен с первым входом второго элемента ИЛИ, выход, которого соединен с (2К+1)-м входом третьего элемента И (где К - разрядность входного сигнала), выход которого соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, вход синхронизации второго регистра соединен с входом синхронизации первого регистра, выходы которого соединены с соответствующими информационными входами второго регистра, с первого по К-й выходы которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены соответственно с первого по К-й входами третьего элемента И, выходы элементов И группы соединены с соответствующими входами элемента сложения по модулю два, (К+1)-й.вход которого соединен с выходом шестого элемента И, второй вход которого соединен с (К+4)-м разрядом выхода второго регистра, (К+1)-й разряд выхода которого соединен с вторым входом второго элемента ИЛИ, (К+2)-й разряд выхода второго регистра соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, (К+4)-й разряд выхода второго регистра соединен с вторым входом пятого элемента И, второй вход которого является входом наращивания разрядности устройства при вычислении суммы по модулю два, вторые входы четвертого элемента ИЛИ и пятого элемента И являются соответственно входом наращивания разрядности устройства при вычислении конъюнкции и вторым входом задания режима устройства.

гг.з

ггг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| О распределенной реализации булевых функций в микропроцессорных системах с логическими нормами ввода-вывода | |||

| - Автоматика и вычислительная техника, 1983, №5, с.58 | |||

| Устройство для записи-воспроизведения в видеомагнитофоне | 1986 |

|

SU1314375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-07—Публикация

1990-04-11—Подача