1

Изобретение относится к автоматике и вычислительной технике, в частности к автоматической обработке хроматографической информации.

Изв1естен интегратор, содержащий аналого-цифровой преобразователь, блок вычитания, цифровую следящую систему, блок управления, сравнивающий сигна11 с пороговым значением и исчисляющий первые разности 13 .Ю

Известен также интегратор для хроматографического анализа, содержащий блок .детектирования пиков, блок коррекции базовой линии, преобразователь напряжение-частота, вентиль, счетчик-накопи- is тель.2 .

Однако известные устройства имеют низкую точность интегрирования хромее тографических пикОв при наличии на20

входе преобразователя помехи известной функциональной зависимости от времени с медленно, монотонно или скачкообразно изменяющейся производной. Подобной помехой в хроматографии может служить как пик растворителя, на заднем склоне которого появляются анализируемые пики, сдвиг нулевой линии, смещение нулевой линии иэ-за традиет ного элюирования или неизотермнческого процесса хроматографического разделеняя, переключения чувствительности входного усилителя.

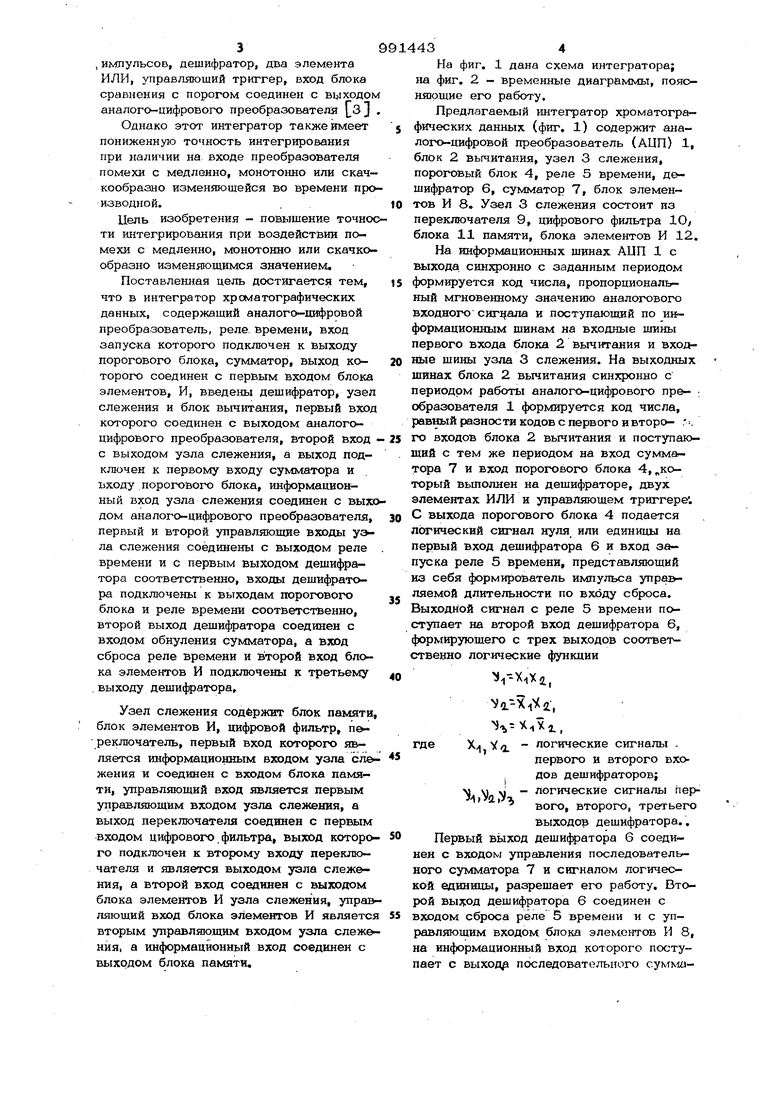

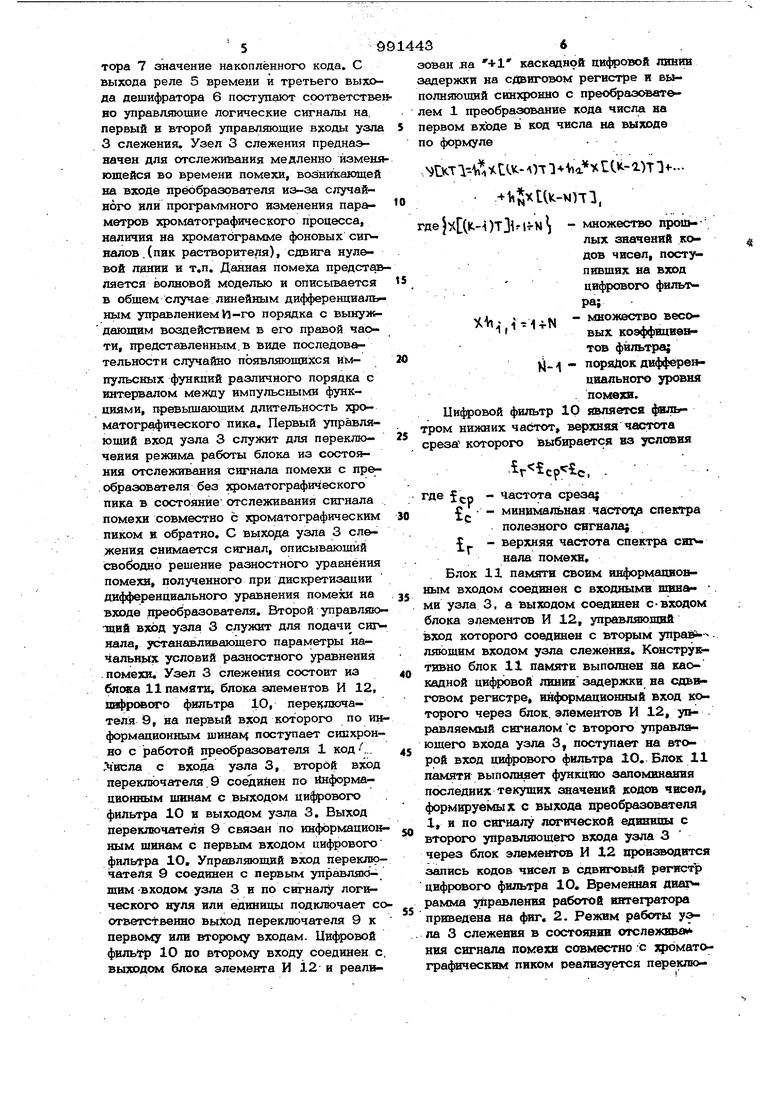

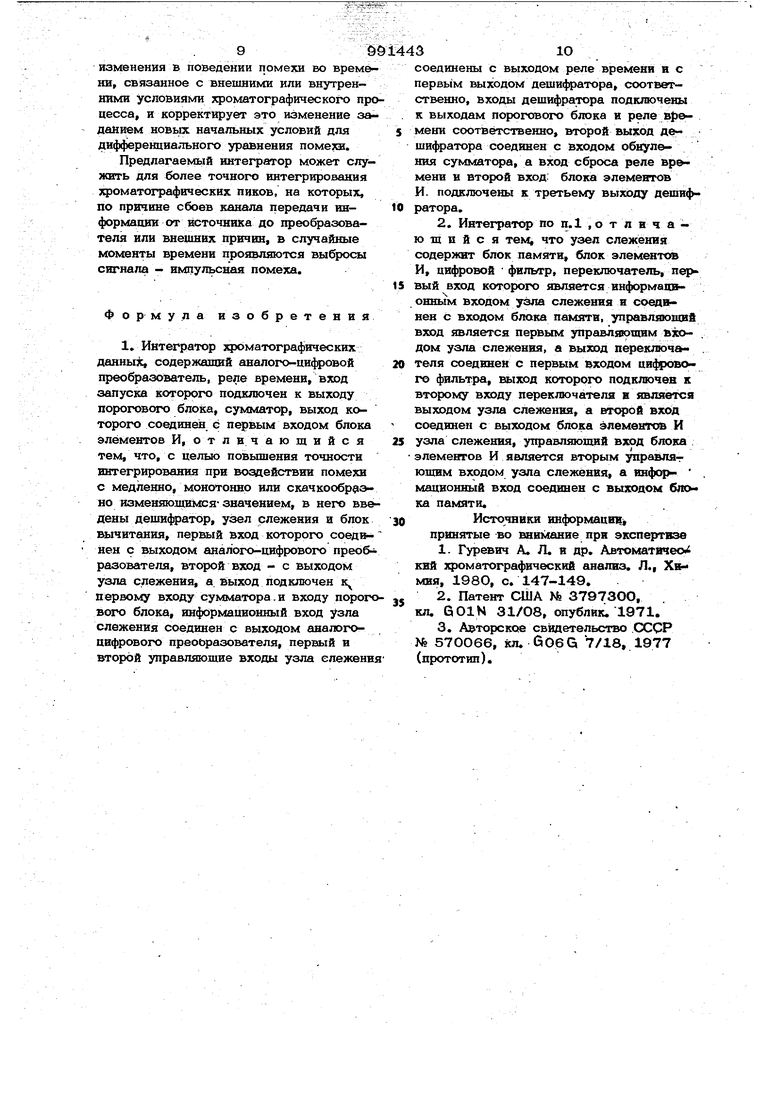

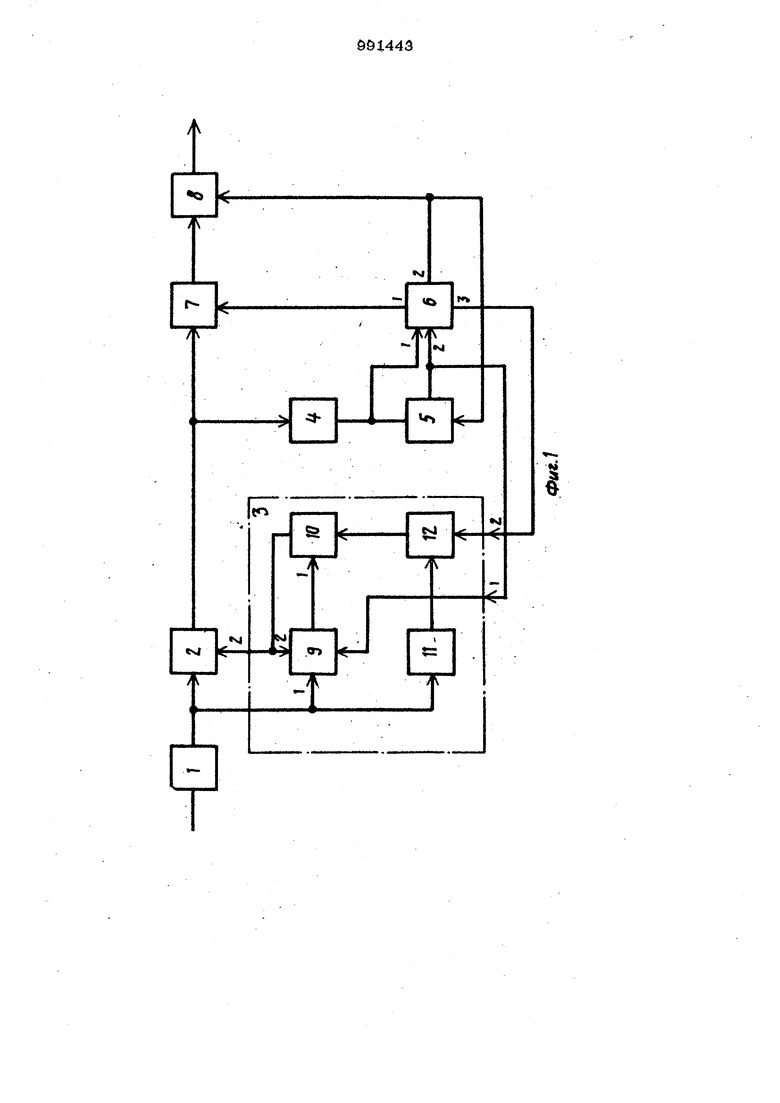

Наиболее близким к предлагаемому изобретению по технической сущности является шггегратор зфоматографических данных, содержащий аналого-ци4фювой преобразователь (напряжение-число-импульснь1й код), выход которого соединен с входом блока интегрирования (счетчик импульсов), выход KOTOjJbro подключен к первому входу элемента И, второй вход элемента И подключен к выходу реле времени, вход запуска которого подключен к входу обнуления блока интегрирования и к выходу блока сравнения с порогом, содержащего счетчик , HivmynbcoB, дешифратор, два элемента ИЛИ, управляющий триггер, вход блока сравнения с порогом соединен с выходом аналого-цифрового преобразователи ,3 Однако этот интегратор также имеет пониженную точность интегрирования при наличии на входе преобразователя помехи с медленно, монотонно или скачкообразно изменяющейся во времени про изводной.. Цель изобретения - повышение точно ти интегрирования при воздействии помехи с медленно, монотонно или скачкообразно изменяющимся значением. Поставленная цель достигается тем, что в интегратор хроматографических данных, содержащий аналого-цифровой преобразователь, реле, времени, вход запуска которого подключен к выходу порогового блока, сумматор, выход которого соединен с первым входом блока элементов. И, введены дешифратор, узел слежения и блок вычитания, первый вход которого соединен с выходом аналогоцифрового преобразователя, второй вход с Выходом узла слежения, а выход подключен к первому входу сумматора и входу порогового блока, информационный вход узла слежения соединен с вых дом аналого-цифрового преобразователя, первый и второй управляющие входы у&ла слежения соединены с выходом реле времени и с первым выходом дешифратора соответственно, входы дешифратора подключены к выходам порогового блока и реле времени соответственно, второй выход дешифратора соединен с входом обнуления сумматора, а вход сброса реле времени и второй вход блока элементов И подключены к третьему . выходу деши4 атора. Узел слежения содержит блок памяти блок элементов И, цифровой фильтр, переключатель, первый вход которого является информационным входом узла еле жения и соединен с входом блока памяти, управляющий вход 5голяется первым управляющим входом узла слежения, а выход переключателя соединен с первым входом цифрового фильтра, выход которо го подключен к второму входу переключателя и является выходом узла слежения, а второй вход соединен с выходом блока элементов И узла слежения, управ ляющий вход блока элементов И являетс вторым управляющим входом узла слеже ния, а информационный вход соединен с выходом блока памяти. На фиг, 1 дана схема интегратора; на фиг. 2 - временные диaгpalvcмы, пояс- шпрщие eix работу. Предлагаемый уштегратор хроматографИ1еских данных (фиг, 1) содержит аналого-цифровой преобразователь (АЦП) 1, блок 2 вычитания, узел 3 слежения, пороговый блок 4, реле 5 времени, дешифратор 6, сумматор 7, блок элементов И 8. Узел 3 слежения состоит из переключателя 9, цифрового фильтра 1О, блока 11 памяти, блока элементов И 12, На информационных шинах АЦП 1 с выхода, синхронно с заданным периодом формируется код числа, пропорциональный мгновенному значению аналогового ВХОДНО1Ч) cKrijana и поступающий по информационным шинам на входные шины первого входа блока 2 вычитания и входные шины узла 3 слежения. На выходных шинах блока 2 вычитания синхронно с периодом работы аналого-цифрового преобразователя 1 формируется код числа, равный разности кодов с первого и второ- . . ГС входов блока 2 вычитания и поступающий с тем же периодом на вход сумматора 7 и вход порогового блока 4, „который выполнен на дешифраторе, двух элементах ИЛИ и управляющем триггере, С выхода порогового блока 4 подается логический сигнал нуля или единицы на первый вход дешифратора 6 и вход запуска реле 5 времени, представляющий из себя формирователь импульса упра:&ляемой длительности по входу сброса. Выходной сигнал с реле 5 времени поступает на второй вход дешифратора 6, формирующего с трех выходов соответ ствевно логические функции Va-XiXi, .г, у - логические сигналы первого и второго входов дешифраторов; - логические сигналы пер(,Va,N вого, второго, третьего выходов дешифратора,. Первый выход деши4ратора 6 соединен с входом управления последовательного сумматора 7 и сигналом логической единицы, разрешает его работу. Второй выход дешифратора 6 соединен с входом сброса реле 5 времени и с управляющим входом блока элементов И 8, на информационный вход которого поступает с выходу последовательного сумматора 7 значение накопленного кода. С выхода реле 5 времени и третьего выхо да дешифратора 6 поступают соответстве но управляющие логические сигналы на, первый и второй управляющие входы узл 3 слежения. Узел 3 слежения преднаэначен для отслеживания медленно йзмеш юшейся во времени помехи, возникающей на входе преобразователя из-за случайного или программного изменения параметров зфоматографического процесса, наличия на хроматограмме фоновых си1 налов.(пнк растворителя), сдвига нулевой Яйнии и т,п. Данная помеха представ ляется волновой моделью и описывается в общем случае линейным дифференциаль ным управлением И-го порядка с вынуж дающим воздействием в его правой части, представленным, в виде последовательности случайно ПОЯВЛ5ПОЩИХСЯ импульсных функций различного порядка с интервалом между импульсными функциями, превышающим длительность ;фО- матографического пика. Первый управляющий вход узла 3 служит для переключения режима работы блока из состояния отслеживания сигнала помехи с пр&. образователя без зфоматографического пика в состояние отслеживания сигнала помехи совместно с зфоматографическим пиком и обратно, С узла 3 сл&жения снимается сигнал, описывающий свободно решение разностного уравнения помехи, полученного при дискретизации дифференциального уравнения помехи на входе преобразователя. Второй управляю тинй вход узла 3 служит для подачи сиг нала, устанавливающего параметры начальных условий разностного уравнения .помехи. Узел 3 слежения состоит из блсжа 11 памати, блока элементов И 12. ивфрсжого фильтра 10, переключателя 9, на первый вход которого по ин формационным шинам поступает синхронно с работой преобразователя 1 код... 1исла с входа узла 3, второй вход переключателя, 9 соедийен по информационным шинам с выходом цифрового фильтра 10 и выходом узла 3, Выход переключателя 9 связан по информацион ным шинам с первым входом цифрового фильтра 1О, Управляющий вход перек/початейя 9 соединен с первым управл5вощнм входом узла 3 и по сигналу логического нуля или единицы подключает со ответственно выход переключателя 9 к первому или второму входам. Цифровой фшпыгр 10 во второму входу соединен с выходом блока элемента И 12 и реалвзован л а -И каскадной цифровой линии задержки на сдвиговом регистре и выполняющий синхронно с преобразователем 1 преобразование кода числа на первом вхЪде в код числа на выходе по формуле. v)C..M)Tl+iia KlC -i)Tl - V«NXUk-N)Tl, roe|x(l.-i) - множество проши лых значений кодов чисел, nocTyiпившях на вход цифрового фильо ра; - множество весо l jl UNвых коэффвциевтов фильтра; j| - порядок диффере цнально1Ч уровня помехи. Цифровой фильтр 10 является фяль тром нижних частот, верхняя частота среза которого выбирается из условия VEcp ic, - где f р - частота среза; - минимальная часто1 спектра полезного сигнала; - верхняя частота спектра сшлнала помехи. Блок 11 памяти своим информадио ньш входом соединен с входными пшна- ми узла 3, а выходом соединен с-входом блока элементов И 12, управляющий вход которого соединен с вторым упрай --. ляющим входом узла слежения. Конструктивно блок 11 памяти выполнен на каскадной цифровой линии задержки на сдвиговом регистре, инфсфмационный вход которого через блок, элементов И 12, . равляемый сигналом с второго управляющего входа узла 3, поступает на второй вход цифрового фильтра 10, Блок 11 памяти выполняет функцию запоминания последних текущих значений кодов чисел формируемых с выхода преобразоватепя 1, и по сигналу логической единицы с в-горого управляющего входа узла 3 через блок элементов И 12 производится запись кодов чисел в сдвиговый регистр цифрового фильтра 10. Временная диах рамма управления работой интегратора приведена на фиг, 2, Режим работы уэла 3 слежения в состоянии отслеживаи ния сигнала пометя совместно с зфоматографическим пиком реализуется переключением работы цифрового фильтра 10 на себя посредством переключателя 9. Интегратор работает следующим обра зом. Первоначально с выхода аналого-ци(| рового преобразователя 1 поступает сиг нал помехи на вход блока 2 вычитания и вход узла 3 слежения. Начальные условия разностного управления помехи установлены и определяются входным сигналом с преобразователя 1. Сигналы на управляющих входах узла 3 отсутств ют. Логический нуль с первого выхода дешифратора 6 запрещает интегрировани и значение сигнала с выхода сумматора 7 держит равным нулю. Логический нул с второго выхода дещифратора 6 запрещает прохождение сигнала на внещнее устройство. На третьем выходе дешифратора 6 тоже логический нуль. Максимальная длительность времени генерации логической единицы с выхода реле времени задается большем, максимально возможной длительности хроматограф ческого пика и определяется из соотношения с г . где - верхняя частота спектра сигн ла помехи; - минимальная частота спектра Полезного сигнала; Тр - максимальная длительность времени генерации реле. При появлении на входе аналого-цифрового преобразователя 1 сигнала троматографического пика, сигнал с выхода блока 2 вычитания превысит значение порога, заданное в порюговом блоке 4, который на выходе выдает сигнал логической единшш и запускает реле 5 времени. С первого выхода дешифратора 6 логической единицей снимается запрет на суммирование кода, поступающего с блока 2 вычитания. Со второго и третье го выходов дещифратора 6 снимаются нули и на блоке элементов И 8 происходит запрет выдачи значения накопленной суммы в сумматор 7 на внешнее устройство. Когда время срабатьгоания реле 5 превышает длительность пика, в момент, когда заканчивается хроматографический пик, вырабатывается сигнал логической единицы с второго входа дешифратора б, который разрешает через блок элементов И 8 прохождение нако№ленной суммы с выхода сумматора 7, величина которой пропорциональна величине интеграла пика, на вход преобразователя. На первом выходе дешифратора 6 устанавливается значение логического нуля, который запрещает суммирование и сбрасывает накопленную сумму в сумгматоре 7 в нуль. Одновременно сигнал со второхчэ выхода дешифратора 6 по входу сброса реле 5 прекращает генерацию сигнала с выхода реле 5, после чего сигнал с второго выхода дешифратора 6 устанавливается в нуль н возвращает реле 5 времени в первоначальный ждущий режим. На время генерации сигнал с выхода реле 5 по первому управляющее му входу узла 3 слежения переводится в режим отслеживания сигнала помехи при наличии хроматографического пика, что выражается-в генерации с выхода дешифратора 6 синхронно с преобразователем 1 кода свободного решения разностногчэ уравнения помехи, начальные условия которого определяются значениями кодов сигнала до начала хроматографического пика. Сигнал логической единицы с третьего выхода дешифратора 6 не появляется и коррекция начальных условий ди(} ференциального уравнения помехи не происходит. Временная диаграмма работы дешифратора 6 совместно с реле 5 Бр&мени показана на фиг. 20. Если на входе преобразователя сигнал помехи изменил свое поведение во времени из-за влияния внешних условий, скачка производной значения сигнала или других параметров зфоматографического процесса и длительность этого воздействия превышает максимальное время срабатывания реле 5; то сигнал разрешения выдачи кода сумматора 7 на внешнее устрю ство, подаваемый на блок элемента И 8, не поступает, сумматор 7 прекращает свою работу, а с третьего выхода дешифратора 6 на второй управляющий вход узла 3 поступает сигнал логической единицы, по которому происходит коррекция начальных условий разностного уравнения помехи и дальнейщая генерация с выхода узла 3 кода свободного рещения уравнения помехи в с новыми начальными услстнями. Временная диаграмма работы дешифратора 6 и реле 5 времени показана на фиг. 2J. Таким образом, предлагаемый интегратор интегрирует хроматографические пики с заданным ограничением во врем&нв, на фоне сигнала помехи, описываемой известным линейным дифференциальным управлением, обнаруживает случайные

изменения в поведении помехи во времени, связанное с внешними или внутренними условиями хроматографического процесса, и корректирует это изменение за данием новых начальных условий для

дифференциального уравнения помехи.

Предлагаемый интегратор может служить для более точногю интегрирования лроматографических пиков, на которых, по сбоев канала передачи информации от источника до преобразователя или внешних причин, в случайные моменты времени проявляются выбросы сигнала - импульсная помеха.

.

Формула изобретения

1, Интегратор чоматографических данных, содержавши аналого-цифровой

преофазователь, реле времени, вход запуска которого подключен к выходу порогового блока, сумматор, выход которого соединен с первым входом блока элементов И, о т л и ч а ю щ и и с я тем, что, с целью повышения точности интегрирования при воздействии помехи с медленно, монотонно или скачкообразно изменяющимся- значением, в него введены дешифратор, узел слежения и блок вычитания, первый вход которого соедийен с выходом аналого-цифрового прео& разователя, второй вход - с выходом узла слежения, а выход подключен к первому входу сумматора.и входу порого вого блока, информационный вход узла слежения соединен с выходом аналогоцифрового преобразователя, первый и второй управляющие входы узла слежени

соединены с выходом реле времени и с первым выходом дешифратора, соответственно, входы дешифратора подключены к выходам порогового блока к реле в{эемени соответственно, второй выход дешифратора соединен с входом обчуления сумматора, а вход сброса реле вр мени и второй вход блока элементов И. подключены к третьему выходу дешиф ратора,

2. Интегратор по п.1 , о т л и ч а - ю ш и и с я тем, что узел слежения содержит блок памяти, блок элемш1тов И, цифровой фильтр, переключатель, пер вый вход которого является информацвонным входом узла слежения и 4х едввен с входом блока , управляющий вход является первым управляющим ьэсодом узла слежения, а выход переключ теля соединен с первым входом цифрового фильтра, выход которого подключен к второму входу переключателя н является выходом узла слежения, а второй вход соединен с выходом блока элементов И узла слежения, управляющий вход блока элементов И является вторым управляющим входом узла слежения, а ннформационный вход соединен с выходом 6ло« ка памяти.

Источники информацн принятые во внимание при экспертизе

1.Гуревич А. Л. и др. Автоматичео. кЕй зфоматографический анализ. Л., Хии мня, 1980, с. 147-149.

2.Патент США № 37973ОО, . кл. eOlN 31/08, опублик. 1971.

3.Авторское свидетельство .СССР № 57О066, кл. GO G 7/18, 1977 (прототип).

/

«О

3

1Г м

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство слежения за информационной дорожкой носителя оптической записи | 1988 |

|

SU1638724A1 |

| РЕЛЕ НАПРАВЛЕНИЯ МОЩНОСТИ | 2001 |

|

RU2195000C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛА | 2012 |

|

RU2498343C1 |

| Устройство для психофизиологическихиССлЕдОВАНий | 1979 |

|

SU827029A1 |

| Устройство для отделения хроматографического микропика от склона основного пика | 1985 |

|

SU1256047A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2409822C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

М

4

.9

ч

Авторы

Даты

1983-01-23—Публикация

1981-10-23—Подача