(54) АНАЛОГОВЫЙ ДЕКОДЕР РАСШИРЕННОГО

Изобретение предназначено для использования в системах передачи информации по декаметровым и тропосферHbit-i радиолиниям.

Известны декодирующие устройства кодов Хэмминга, исправляющие стирания и содержащие основной регистр сдвига, информационный вход которого соединен с подвижным контактом первого переключателя, первый неподвижный контакт которого подключен к основной входной шине, а второй неподвиж ный контакт - к вьлходной шине и выходу последнего разряда основного сдвигового регистра, разрядные вьосоды которого соединены с первыми входами логического блока, вторые входы которого подключены к соответствукядим разрядньм выходам маркерного сдвигового регистра, информационный вход которого через замыкающую кнопку соединен с выходом его последнего разряда, при этом выходы.логического блока подключены к соответствующим первым установочным входам основного и маркерного регистров fljТакие декодирующие устройства позволяют исправлять ошибки до второй кратности включительно и некоторые ошибки более высокой кратности. ОднаКОДА ХЭММИНГА

ко при декодировании в них не используется дополнительный символ общей проверки на четность, что приводит к низкой помехоустойчивости.

Наиболее близким к изобретению по технической сущности является аналоговый декодер, содержащий основной сдвиговый регистр, информационный вход которого соединен с подвижным

10 контактом первого переключателя, первый неподвижный контакт которого подключен к основной входной шине, а второй неподвижный контакт - к выходной шине и выходу последнего раз15ряда основного сдвигового регистра, часть разрядных выходов которого соединена с первыми входами логического блока, вторые входы которого подключены к соответствующей части разряд20ных выходов маркерного сдвигового регистра, информациоиньой вход которого через замыкающую кнопку соединен с выходом его последнего разряда; выходы логического блока подключены

25 к части первых установочных входов основного-и маркерного сдвиговых регистров; блок определения номера наименьшего из нескольких чисел, первые и вторые выходы которого соедине30ны с соответствующими частями вторых

установочных входов основного и маркерного сдвиговых регистров, а входы подключены к соответствующей части разрядных выходов сдвигового регистр памяти мадежностей,информационный вход которого соединен с подвижныгл контактом второго переключателя, первый неподвижный контакт которого соединен с входной шиной надел ностей а второй неподвижный контакт - с выходом его послед1 его разряда j.

В известном декодере стирсчются, а затем восстанавливаются наименее надежные символы, причем из рассмотрения исключается дополнительный символ общей проверки на четность, вследствие чего декодер обладает низкой помехоустойчивостью, позволяя исправлять ошибки кратности до n-k-1 где п - длина расширенного кода Хэмминга; k - число информационнг-лх символов .

Целью изобретения является повышение поглехоустойчивости декодеров расширенного кода Хэмминга :а счет использования для декодирования информации о всех символах принятой коддовой комбинации и увеличения кратности исправляем1лх оищбок до n-k включительно.

Указанная цель достигается тем, что в аналоговый декодер расширенного кода , содержащий octiOBную входную шину, ocHOBHOii сдвиговый регистр, информационный вход которог соединен с подвижным контактом пе1звого переключателя, второй неподвижный контакт которого Ю киючеп к выходной шине и выходу последднехО разряда основного сдвигового рехистра, част разрядных выходов к-OTopoio соед1Н-1ена с первыми входами логического блока, вторые входы которого гюдцслючены к соответствующим разрядным выходам маркерного сдвигового регистра, инфомационный вход которого iCiieo замл-якащую кнопку соединен с в1-лходом его последнего разряда, при этом выхо;ды логическо1о блока подключены к первым установочным входам соответствующих разрядов основного и маркерного сдвиговых регистров, вторые установочные входы которых соединены соот ветственно с первыми и вторыми выходами блока определения номера наименьшего из нескольких чисел, входы которого подключены к соответствующи разрядным выходам сдвигового регистр памяти надежностей, информационный вход которого соединен с подвижным контактом второго переключателя, второй неподвижный контакт которого подключен к выходу последнего разряда сдвигового регистра памяти надежностей, и входную шину надежностей, введены дополнительный разряд основного сдвигового регистра, дополнительный разряд сдвигового регистра памяти надежностей, причем информационные входы этих разрядов соединены с основной входной шиной и входной 1йиной надежностей соответственно а выходы - с nepBbiNtti неподвижными KOFJTaKTaMH первого и второго переключателей соответственно, дополнительный разряд маркерного сдвигового регистра, дoпo п итeльный блок определения номера наименьшего из нескольких чисел, входы которого соединены с соответствующими выходами разрядов включая дополнительный, регистра памяти надежностей, а первые и вторые выходы - с соответствующими вторыми установочными входами разрядов, включая дополнительные, основного и маркерного сдвиговых регистров, первые установочные входы которых подключен к выходам доподшительного логического блока, первые и вторые входы которого соединены с выходами указанных разрядов, включая дополнительные, основного и маркерного сдвиговых регистров соответственно.

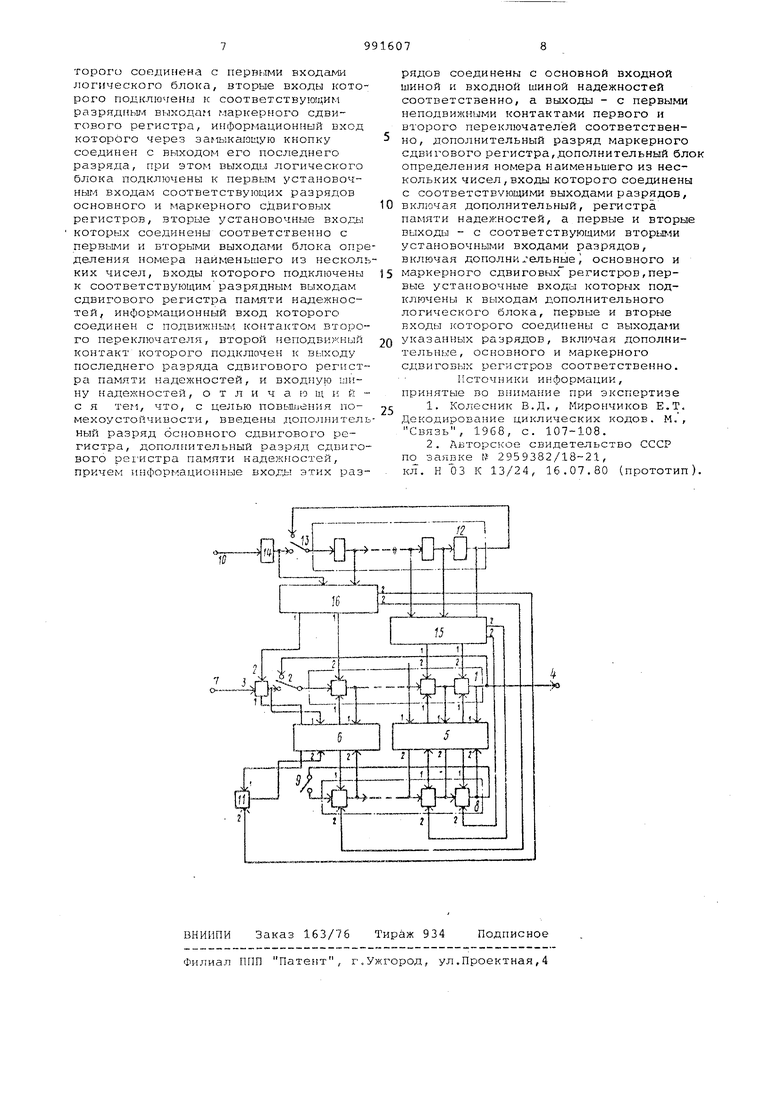

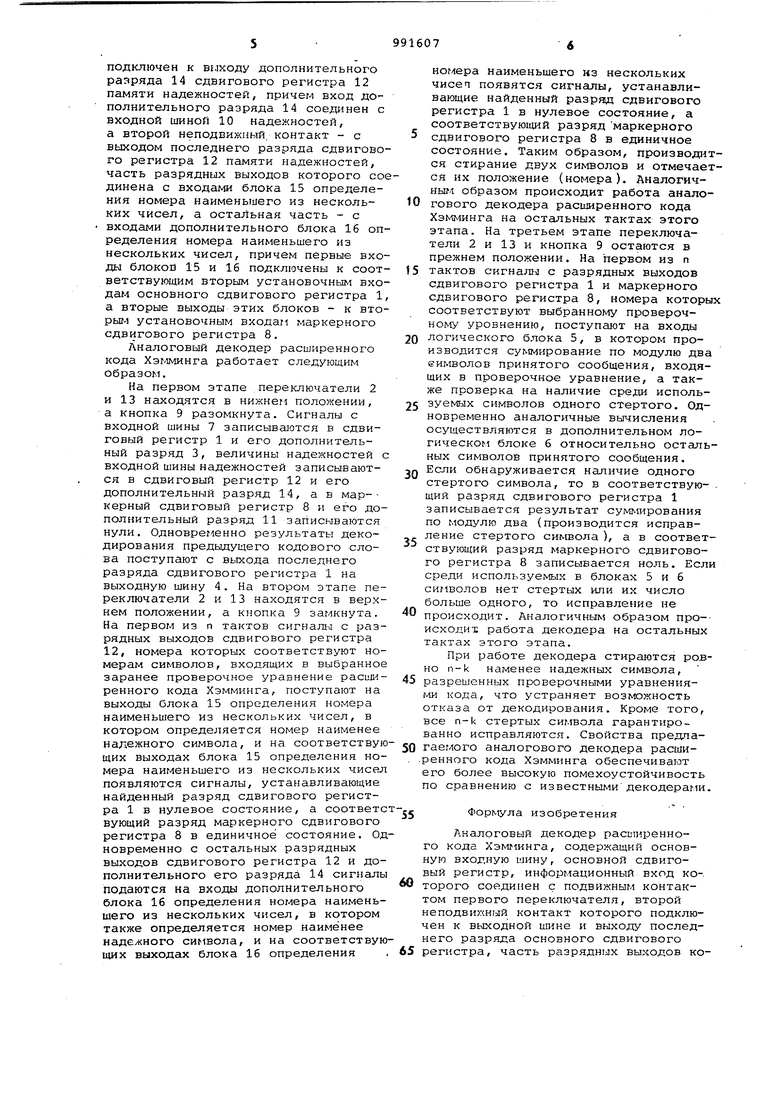

На чертеже предс1авлена блок схема аналогового .декодера pacuivipeHHoго кода Хэмминга.

Декодер соддержит основной сдвиговый регистр 1, информационный вход которого соедлинен с подвижным контактом riepiioro переклю- ателя 2, первый 11еио,.(ный -сонтагст которог-о подключен к выходу доподпштельного разряда 3 ос1;о июго сдвигового peiiicTpa 1, а второй неподвижный конта ;т - к выходной uiiiHC 4 и В1..1ХОДУ последнего разряД(1 осноиного сдв1-:гового регистра 1, часть разрядных выходов которого соединена с перныгли входами логического блока 5 , а остальная, часть разрядных В1ЛХОДОВ - с nepuuiiii входам дополнительного логического блока б, в том числе I выход дополнительного разрядг.а 3 , и формационный вход которого подк.гпочсн к основной входной iUUie 7; маркерный сдвиговы регистре и.нфор.-.ацнонны вход которого через зам1--1Кс1ющу10 кнопку 9 соединен с выходом его последнего разряда, часть разрядных выходов соединена с вторыми входами логического блока 5, осталъная часть - с вторьиди входами догюлшггельного логического блока 6; входную iijHHy 10 надежностей, в том числе и выход дополнигельного разряда 11 .маркерного сдвигового регистра 8, причем первые установочные ВХОДЕ- рггзрядов основного и маркерного сдвигов 1х регистров, включая дополнительь ые разряды, подключены к соответствующим выходам логических блоков 5 и 6; сдвиговый регистр 12 памяти надежностей, информационный вход которого соединен с подвижным входом второго переключателя 13/ первый неподвижный контакт КОТОРОГО

подключен к выходу дополнительного разряда 14 сдвигового регистра 12 памяти надежностей, причем вход дополнительного разряда 14 соединен с входной шиной 10 надежностей, а второй неподвижный, контакт - с выходом последнего разряда сдвигового регистра 12 памяти надежностей, часть разрядных выходов которого соединена с входами блока 15 определения номера наименьшего из нескольких чисел, а остальная часть - с входами дополнительного блока 16 определения номера наименьшего из нескольких чисел, причем первые входы блокой 15 и 16 подключены к соответствующим вторым установочным входам основного сдвигового регистра 1, а вторые выходы этих блоков - к вторыг-1 установочным входам маркерного сдвигового регистра 8.

Аналоговый декодер расширенного кода Хэмминга работает следующим образом.

На первом этапе .переключатели 2 и 13 находятся в нижнем положении, а кнопка 9 разомкнута. Сигналы с входной шины 7 записываются в сдвиговый регистр 1 и его дополнительный разряд 3, величины надежностей с входной шины надежностей записываются в сдвиговый регистр 12 и его дополнительный разряд 14, а в мар- керный сдвиговый регистр 8 и его дополнительный разряд 11 записываются нули. Одновременно результаты декодирования предыдущего кодового слова поступают с выхода последнего разряда сдвигового регистра 1 на выходную шину 4. На втором этапе переключатели 2 и 12 находятся в верхнем положении, а кнопка 9 замкнута. На первом из п тактов сигналы с разрядных выходов сдвигового регистра 12, номера которых соответствуют номерам символов, входящих в выбранное заранее проверочное уравнение расширенного кода Хэмминга, поступают на выходы блока 15 определения номера наименьшего из нескольких чисел, в котором определяется номер наименее надежного символа, и на соответствующих выходах блока 15 определения номера наименьшего из нескольких чисел появляются сигналы, устанавливающие найденный разряд сдвигового регистра 1 в нулевое состояние, а соответсвующий разряд маркерного сдвигового регистра 8 в единичное состояние. Одновременно с остальных разрядных выходов сдвигового регистра 12 и дополнительного его разряда 14 сигналы подаются на входы дополнительного блока 16 определения номера наименьшего из нескольких чисел, в котором также определяется номер наименее надежного символа, и на соответствующих выходах блока 16 определения

номера наименьшего нз нескольких чисеп появятся сигналы, устанавливающие найденный разряд сдвигового регистра 1 в нулевое состояние, а соответствующий разряд маркерного сдвигового регистра 8 в единичное состояние. Таким образом, производится стирание двух символов и отмечается их положение (номера). АналогичHHfi образом происходит работа анало0гового декодера расширенного кода Хэмминга на остальных тактах этого этапа. На третьем этапе переключатели 2 и 13 и кнопка 9 остаются в прежнем положении. На первом из п

5 тактов сигналгл с разрядных выходов сдвигового регистра 1 и маркерного сдвигового регистра 8, номера которых соответствуют выбранному проверочному уровнению, поступают на входы логического блока 5, в котором про0изводится суммирование по модулю два еимволов принятого сообщения, входящих в проверочное уравнение, а также проверка на наличие среди используемых символов одного стертого. Од5новременно аналогичные вычисления осуществляются в дополнительном логическом блоке 6 относительно остальных символов принятого сообщения. Если обнаруживается наличие одного

0 стертого символа, то в соответствую- . щий разряд сдвигового регистра 1 записывается результат cyм 5иpoвaния по модулю два (производится исправление стертого символа ), а в соответ5ствующий разряд маркерного сдвигового регистра 8 записывается ноль. Если среди используемых в блоках 5 и 6 символов нет стертых или их число больше одного, то исправление не

0 происходит. Аналогичным образом про-исходих работа декодера на остальных тактах этого этапа.

При работе декодера стираются ровно n-k наменее надежных символа,

5 разрешенных проверочными уравнениями кода, что устраняет возможность отказа от декодирования. Кроме того, все n-k стертых символа гарантированно исправляются. Свойства предла0гаемого аналогового декодера расши.ренного кода Хэмминга обеспечивают его более высокую помехоустойчивость по сравнению с известными декодерами.

Формула изобретения

5

Аналоговый декодер расширенного кода Хэм 1инга, содержащий основную входную шину, основной сдвиговый регистр, информационный вход ко-,

0 торого соединен с подвижным контактом первого переключателя, второй неподвижный контакт которого подключен к выходной шине и выходу последнего разряда основного сдвигового

5 регистра, часть разрядных выходов которого соеди 1ена с первь.тми входами логического блока, вторые входы которого подклю гены к cooтвeтcтвyю ци 4 разрядиьПЛ выходгш маркерного сдвигового регистра, информационный вход которого через замыкающую кнопку соединен с выходом его последЕ его разрях а, при этом выходы логического блока подключены к первым установочным входам соответствующих разрядов основного и маркерного сдвиговых регистров, вторые установочные вхорд: 1 которых соединены соответственно с первыми и вторыми выходагчи блока определения номера наименьшего из нескольких чисел, входы которого подключены к соответствующимразрядным выходам сдвигового регистра паг-ляти надежностей, информационный вход которого соединен с подвих ньм контактом второго переключателя, второй неподвикныГ5 контакт которого поддключен к выходу последнего разряда сдвигового регистре памяти надежностей, и входную i;iH-ну надежностей, отличаю щ и и с я тем, что, с целью повышения помехоустойчивости, введены дополнительный разряд основного сдвигового регистра, дополнительный разряд сдвигового рехистра памяти надежностей, причем информационные входы этих разрядов соединены с основной входной шиной и входной шиной надежностей соответственно, а выходы - с первыми неподвижными контактами первого и второго переключателей соответственно, дополнительный разряд маркерного сдвигового регистра,дополнительный блок определения номера наименьшего из нескольких чисел,входы которого соединены с соответствующими выходами разрядов, включая дополнительный, регистра памяти надежностей, а первые и вторые выходы - с соответствующими вторыми установочными входами разрядов, включая дополни жельные ) основного и 5 маркерного сдвиговых регистров,первые установочные входы которых подключены к выходам дополнительного логического блока, первые и вторые входы которого соединены с выходами указанных разрядов, включая дополнительные, основного и маркерного сдвиговых регистров cooTBeTCTBeHFio.

Источники информации, принятые во внимание при экспертизе

1.Колесник В.Д., Мирончиков Е.Т. Декодирование циклических кодов. М., Связь, 1968, с. 107-108.

2.Лвторское свидетельство СССР по заявке № 2959382/18-21,

кл. Н 03 К 13/24, 16.07.80 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый декодер кода Хэмминга | 1980 |

|

SU945986A1 |

| Аналоговый декодер кода Абрамсона | 1981 |

|

SU988165A1 |

| Аналоговый декодер кода с ортогональными проверками | 1986 |

|

SU1401614A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАЧАЛА БЛОКА ДАННЫХ ВО ВНЕШНЕЙ ПАМЯТИ | 1991 |

|

RU2024966C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Декодер кодов Рида-Соломона | 1988 |

|

SU1690202A1 |

| Устройство для формирования тестов | 1985 |

|

SU1297059A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Ассоциативное запоминающее устройство | 1981 |

|

SU978196A1 |

V ---lM -i

/

Авторы

Даты

1983-01-23—Публикация

1981-07-13—Подача