Изобретение относится к вычислительной технике, а именно к внешним запоминающим устройствам (ВЗУ), и может быть использовано в контроллерах ВЗУ.

Известно устройство, определяющее начало блока данных во внешней памяти ЭВМ [1] и содержащее демодулятор, счетчик, шесть RS-триггеров, восемь элементов И, семь элементов ИЛИ, элемент НЕ.

Недостаток устройства - недостаточно высокая надежность определения начала блока при работе с накопителями с высоким уровнем ошибок в считанных данных.

Известно устройство, определяющее начало блока данных во внешней памяти ЭВМ [2] и содержащее селектор синхросигналов, сдвиговые регистры, счетчики, два пороговых блока, триггер, элементы И, элементы ИЛИ, элементы НЕ.

Недостаток устройства - большой объем оборудования, возрастающий пропорционально количеству маркеров в заголовке блока.

Наиболее близким по технической сущности к изобретению является устройство, определяющее начало блока данных во внешней памяти ЭВМ [3] и содержащее сдвиговый регистр, декодер канального кода, схему обнаружения маркеров, счетчик, преобразователь кодов. Устройство определяет начало блока данных, обнаружив любую последовательность r маркеров из множества маркеров заголовка блока.

Недостатками рассмотренного устройства являются большой объем оборудования, возрастающий пропорционально количеству выделяемых подряд маркеров в заголовке блока, и недостаточно высокая надежность определения начала блока данных.

Цель изобретения - упрощение устройства за счет уменьшения разрядности сдвигового регистра и схемы обнаружения последовательности маркеров и повышение надежности определения начала блока данных путем кодирования имен маркеров помехоустойчивым кодом.

Цель достигается тем, что в устройство, содержащее сдвиговый регистр, декодер канального кода, первый селектор кода, первый счетчик, преобразователь кодов, на D-вход сдвигового регистра поступает считываемая с носителя информация, на С-входы сдвигового регистра и первого счетчика и второй вход первого селектора кода поступают тактовые импульсы, вторые выходы сдвигового регистра подключены к первым входам первого селектора кода, введены регистр, блок сравнения кодов, второй селектор кода, второй счетчик, первый и второй коммутаторы, первый и второй элементы И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЕ, первые выходы сдвигового регистра подключены к входам декодера канального кода, вторые выходы декодера канального кода подключены к первым входам блока сравнения кодов и вторым входам первого коммутатора, выход первого селектора кода подключен к первому входу первого элемента И, второму входу второго коммутатора, второму входу элемента ИЛИ-НЕ, входу Do второго счетчика, выход блока сравнения кодов подключен к второму входу первого элемента И, выход первого элемента И подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого коммутатора подключены к D-входам регистра, выходы регистра подключены к входам преобразователя кодов и входам второго селектора кода, выходы преобразователя кодов подключены к первым входам первого коммутатора и вторым входам блока сравнения, выход второго коммутатора подключен к С-входу регистра и R-входу первого счетчика, выход первого счетчика подключен к первому входу второго коммутатора, второму входу второго элемента И, второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первому входу элемента ИЛИ-НЕ, выход второго селектора кода подключен к первому входу второго элемента И, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к входу управления режимом прием/счет второго счетчика, выход элемента ИЛИ-НЕ подключен к С-входу второго счетчика, выход второго счетчика подключен к управляющим входам первого и второго коммутаторов, к третьим входам второго элемента И и элемента ИЛИ-НЕ, на входы D1-Dv-1 второго счетчика подаются сигналы логического нуля, на R-вход второго счетчика подается сигнал СБРОС, первые выходы декодера канального кода являются информационными выходами устройства, выход второго элемента И является выходом устройства, индицирующим начало блока данных.

Дополнительно введенные второй счетчик, второй элемент И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, ИЛИ-НЕ позволяют перейти от параллельного выделения любой последовательности из r маркеров подряд, когда они находятся в сдвиговом регистре, к последовательному. При этом длина сдвигового регистра уменьшается в r раз.

Дополнительно введенные блок сравнения кодов, первая схема И приводят к вырождению схемы обнаружения маркеров прототипа в значительно более простой первый селектор кода.

Дополнительно введенные регистр, коммутаторы и соответствующее включение преобразователя кодов позволяет использовать для кодирования имен маркеров помехоустойчивый код, что приводит к уменьшению вероятности неправильного определения начала блока.

В результате проведения сопоставительного анализа заявляемого технического решения и аналогичных решений, обнаруженных в патентной и технической литературе, был сделан вывод о наличии существенных отличий у заявляемого решения.

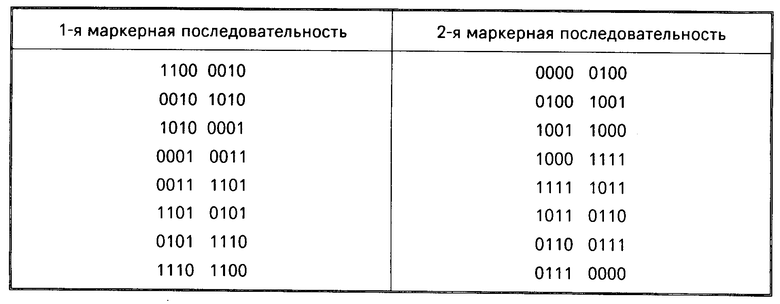

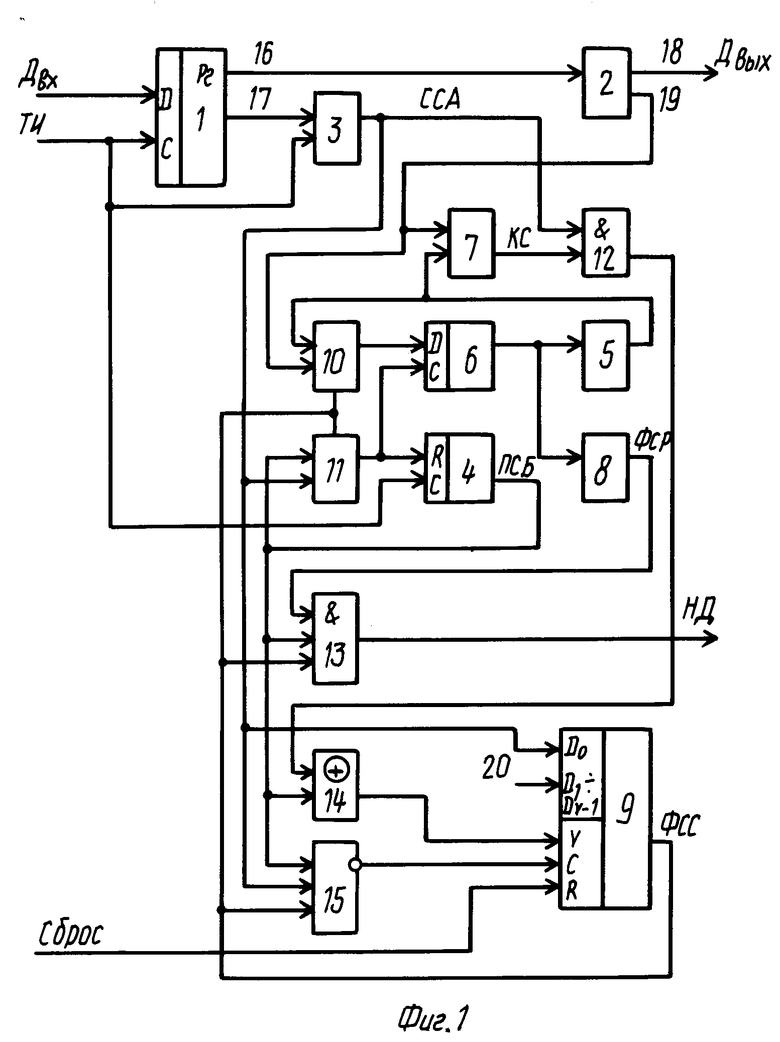

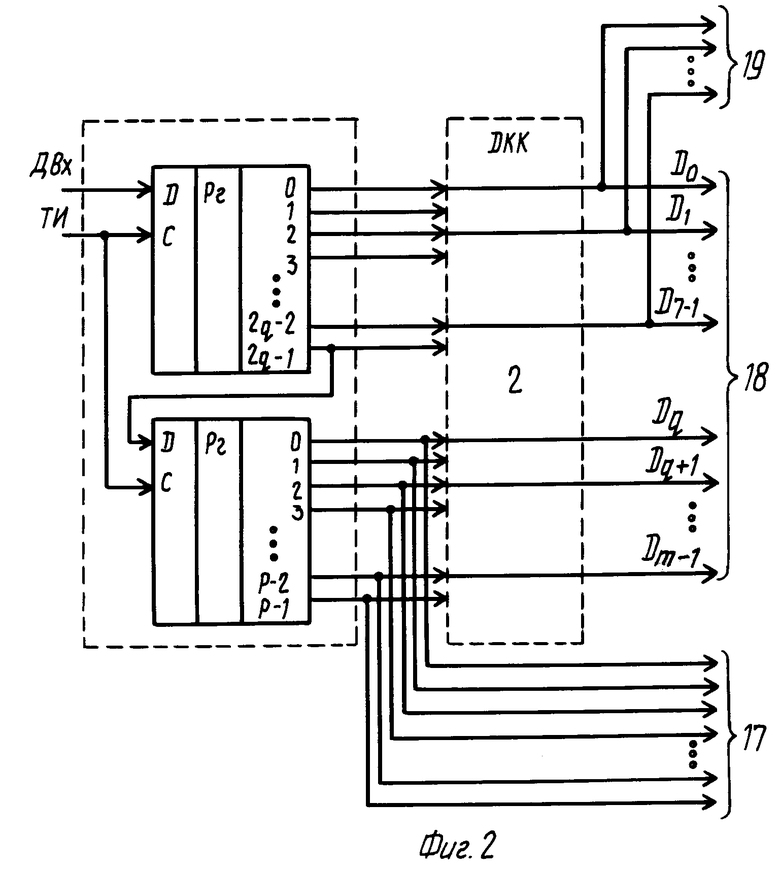

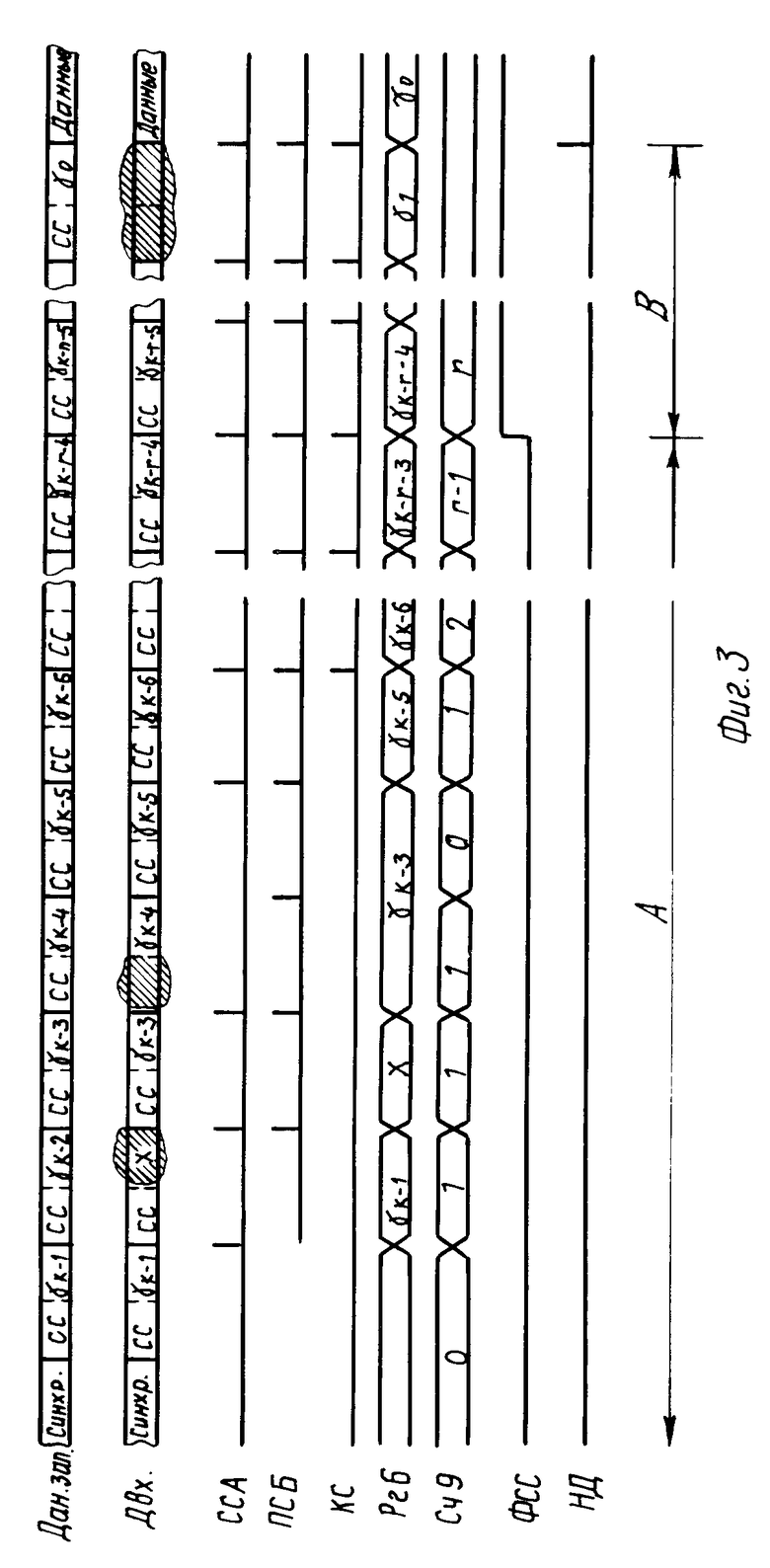

На фиг. 1 показана схема устройства для определения начала блока данных (УОНБД) во внешней памяти ЭВМ; на фиг. 2 - сдвиговый регистр и декодер канального кода МФМ; на фиг. 3 - временные диаграммы работы УОНБД при наличии ошибок в маркерной последовательности; на фиг. 4 - граф, поясняющий работу счетчика маркеров (второго счетчика).

Устройство для определения начала блока данных (фиг. 1) содержит сдвиговый регистр 1, декодер канального кода 2, первый селектор кода 3, первый счетчик 4, преобразователь кодов 5, регистр 6, блок сравнения кодов (БСК) 7, второй селектор кода 8, второй счетчик 9, первый и второй коммутаторы 10 и 11, первый и второй элементы И 12 и 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент ИЛИ-НЕ 15. На фиг. 1 и 2 цифрами обозначены первые и вторые выходы сдвигового регистра - 16 и 17, первые и вторые выходы декодера канального кода - 18 и 19, сигналы логических нулей - 20.

На фигурах используются следующие обозначения сигналов: Dвх - входные данные в последовательном виде; Dвых - выходные данные в параллельном виде; ТИ - тактовые импульсы; ССА - синхросигнал активен; КС - коды на входах блока сравнения кодов совпали; ФСР - финальное состояние регистра; ПСБ - перенос счетчика бит (первого счетчика); НД - начало данных; ФСС - финальное состояние счетчика маркеров (второго счетчика).

Кроме того, при описании изобретения использованы следующие обозначения:

k - количество маркеров в маркерной последовательности;

r - количество выделенных подряд маркеров, при котором принимается решение о нахождении заголовка данных;

v - наименьшее целое большее или равное log2(r+1);

l - длина маркера (в битах канального кода);

w - наименьшее целое большее или равное log21;

p - длина синхросигнала (в битах канального кода);

q - разрядность кода имени маркера;

m - разрядность шины Dвых;

n - длина кодового слова помехоустойчивого кода;

d - минимальное кодовое расстояние помехоустойчивого кода;

η - число триггерных элементов в блоке;

γi - имя i-го маркера.

На фиг. 1 и 2 первые выходы 16 сдвигового регистра 1 являются l-разрядными; вторые выходы 17 сдвигового регистра 1 - p-разрядными; вторые выходы (19) декодера канального кода 2, выходы первого коммутатора 10, регистра 6 и преобразователя кодов 5 - q-разрядными; первые выходы (18) декодера канального кода 2 - m-разрядными; сигналы логического нуля 20-(v-1)-разрядными.

Сдвиговый регистр 1 является l-разрядным; первый счетчик 4 - w-разрядным (с коэффициентом пересчета l); регистрт 6 - q-разрядным; второй счетчик 9 - v-разрядным (с коэффициентом пересчета r+1).

Декодер канального кода 2 представляет собой комбинационную логическую схему на l входов и m выходов (сигналы вторых выходов декодера являются подмножеством сигналов первых выходов) и может быть реализован на ПЗУ, ПЛМ или дискретных логических компонентах. В случае применения канального кода МФМ декодер вырождается в совокупность перемычек (см. фиг. 2). При этом выходы 18 декодера соединяются со всеми его нечетными входами, выходы 19 соединяются с q младшими нечетными входами.

Счетчики 4 (в режиме счета и обнуления) и 9 (в режиме счета и приема информации), регистр 1 срабатывают по положительному фронту сигналов поданных на С-входы. При этом счетчик 9 увеличивает свое содержимое на единицу, если на вход управления режимом прием/счет подается логический нуль; в противном случае в счетчик 9 загружается информация с D-входов. Вход R счетчика 9 - асинхронный. В регистр 6 загружается информация с D-входов по отрицательному фронту сигнала, поданного на С-вход.

На выходе счетчика 4 (ПСБ) формируется логическая единица, когда счетчик находится в состоянии l-1, и сигнал на его С-входе равен нулю. На выходе счетчика 9 (ФСС) формируется логическая единица, когда счетчик находится в состоянии r.

На выходы коммутаторов 10, 11 подаются сигналы с их вторых входов (19 и ССА соответственно) при наличии логического нуля на управляющих входах, в противном случае на их выходы подаются сигналы с их первых входов.

На выходе блока сравнения кодов 7 формируется логическая единица только в случае равенства кодов на его входах, на выходе селектора кода 3 формируется логическая единица только в случае наличия на его первых входах заданной кодовой комбинации и логического нуля на втором входе (стробирующем), второй селектор кода 8 работает так же как первый только без стробирования. Блок сравнения кодов 7 и селекторы кодов 3, 8 могут быть реализованы в виде комбинационной схемы известным образом на ПЗУ, ПЛМ или дискретных логических компонентах.

Преобразователь кодов 5 представляет собой комбинационную схему с q-разрядными входами и выходами и может быть реализован на ПЗУ, ПЛМ или дискретных логических компонентах.

Для определения начала блока данных на носитель информации непосредственно перед байтами данных записывается заголовок (см. фиг. 3). Заголовок содержит область синхроимпульсов, необходимых для установления синхронизации схемы ФАПЧ (на фиг. 3 область обозначена: СИНХР) и последовательность из k l-разрядных маркеров - указателей начала блока. Каждый маркер содержит p-разрядный синхросигнал СС и q-разрядное имя γi (в битах канального кода МФМ разрядность кода имени равняется 2q).

В качестве синхросигнала используется последовательность бит канального кода, отличающаяся от любой комбинации бит канального кода, записанной на носителе.

Каждый маркер расположен от начала блока данных на расстоянии, определяемом именем маркера. Канкатенация кодов имен r соседних маркеров γi, ..., γi-r+1 образует n-разрядное слово блочного помехоустойчивого кода с минимальным кодовым расстоянием d. Таким образом любые две последовательности из r маркеров, в том числе перекрывающиеся, отличаются друг от друга не менее, чем в d разрядах. Это позволяет уменьшить вероятность неверного определения начала блока при поражении кодов имен маркеров ошибками, что особенно важно при большом числе маркеров и высокой вероятности ошибок.

Помехоустойчивый код выбирается таким образом, чтобы для заданных k и n обеспечить максимальное минимальное кодовое расстояние d. Пример такого кода для r=2 будет приведен ниже.

Рассмотрим обработку заголовка блока данных УОНБД в соответствии с фиг. 3. В работе УОНБД можно выделить два этапа: первый - выделение r маркеров подряд, второй - формирование временной задержки от момента выделения r-го маркера до начала блока данных. На фиг. 3 этим этапам соответствуют временные интервалы: А - интервал времени от момента установки в ноль второго счетчика сигналом СБРОС в области СИНХР до момента времени перехода второго счетчика 9 в состояние с номером r; В - интервал времени от момента фиксации r маркеров подряд до момента формирования импульса начала блока данных.

Процесс выделения подряд r маркеров из принимаемой УОНБД информации представлен в виде графа на фиг. 4. Вершины графа, пронумерованные от 0 до r, отображают состояния счетчика 9, подсчитывающего выделенные подряд маркеры. Переход из одного состояния в другое происходит при выполнении определенных условий (a, b, c, d), являющихся логическими функциями сигналов ССА, ПСБ, КС (см. на фиг. 4). По сигналу СБРОС счетчик из любого состояния независимо от условий a, b, c, d переходит в состояние 0 (на фиг. 4 не показано).

В нулевом состоянии счетчик будет находиться до тех пор, пока не будет выделен хотя бы один синхросигнал маркера. Переход из нулевого состояния счетчика в единичное происходит в случае обнаружения синхросигнала маркера независимо от его имени. Переход из i-го в i+1 состояние (i = 1, 2, 3, ..., r-1) происходит в случае, если следующий выделенный маркер обнаружен ровно через l бит канального кода от начала предыдущего (период следования маркеров - l) и имя его соответствует ожидаемому. В противном случае происходит переход в нулевое состояние, если следующий синхросигнал не обнаружен на расстоянии меньшем или равном l бит от начала предыдущего, или в единичное состояние, если код имени следующего выделенного маркера не соответствует ожидаемому или его синхросигнал обнаружен на расстоянии меньшем l бит от начала синхросигнала предыдущего маркера.

Работу УОНБД в процессе выделения r маркеров подряд поясняет фиг. 3. На фиг. 3 приведен пример обработки УОНБД заголовка блока с тремя пораженными ошибками маркерами: у второго маркера поражено ошибками имя, у четвертого - синхросигнал, у последнего - и имя, и синхросигнал.

УОНБД работает в интервале А следующим образом.

Сигнал СБРОС устанавливает в ноль второй счетчик 9. Нулевой потенциал на выходе счетчика 9 поступает: на третий вход элемента ИЛИ-НЕ 15, разрешая прохождение импульсов ПСБ и ССА с первого или второго входа элемента ИЛИ-НЕ 15 на его выход; на третий вход элемента И 13, закрывая его; и на управляющие входы коммутаторов 10 и 11, в результате чего выходы этих коммутаторов логически соединяются со вторыми их входами.

В области СИНХР импульс переноса счетчика 4 ПСБ поступает на вход С счетчика 9 через открытый низкими уровнями сигналов ФСС и ССА, элемент ИЛИ-НЕ 15. В счетчик 9 загружается нулевой код с D-входов, так как на его вход V поступает единичный потенциал, полученный в результате сложения по модулю два на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 14 активного сигнала ПСБ и пассивного сигнала, полученного с выхода, закрытого низким уровнем сигнала ССА, элемента И 12. Описанная процедура соответствует на графе (фиг. 4) переходу из вершины 0 в вершину 0 по условию а.

Обнаружив первый синхросигнал маркера в последовательности бит канального кода, селектор 3 вырабатывает сигнал ССА. Содержимое счетчика 9 увеличится на единицу по фронту сигнала ССА, поступившего через элемент ИЛИ-НЕ на вход С счетчика, так как на вход управления режимом счетчика V поступает низкий уровень сигнала, полученный путем сложения по модулю два на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 14 низкого уровня сигнала ПСБ и низкого уровня сигнала с выхода, закрытого пассивным сигналом КС, элемента И 12. Код имени выделенного маркера γk-1 со вторых выходов декодера канального кода 2 перепишется в регистр 6 по фронту импульса ССА, который поступает на вход C регистра 6 через коммутатор 11. Синхросигналом ССА, поступающим через коммутатор 11 на вход R счетчика 4, происходит установка этого счетчика в ноль.

Так как начальное состояние регистра 6 не определено и ПСБ до обнаружения первого импульса ССА не привязан к заголовку, кроме рассмотренной возможны следующие ситуации:

- в момент обнаружения первого синхросигнала сигналы ПСБ и КС имеют высокие уровни;

- в момент обнаружения первого синхросигнала cигнал КС имеет высокий уровень, а ПСБ - низкий. В первом случае содержимое счетчика 9 увеличится на единицу, во второй - в счетчик 9 записывается единица. Все три рассмотренные ситуации соответствуют на графе переходу из вершины 0 в вершину 1 по условию d.

Преобразователь кода 5 преобразует код γk-1, поступающий на его входы с выходов регистра 6, в код γk-2 , который поступает на вторые входы блока сравнения кодов. В момент выделения селектором 3 синхросигнала второго маркера на первые входы блока сравнения кодов поступит пораженный ошибками код имени маркера Х (Х ≠γk-2) со вторых выходов декодера 2. Пассивный сигнал КС с выхода БСК 7, поступая на второй вход элемента И 12, закрывает его. Сигнал с выхода закрытого элемента И 12 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. На второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ поступает активный сигнал ПСБ с выхода счетчика 4. Счетчик 9 устанавливается в единицу по фронту сигнала ССА, поступающего на вход С счетчика через элемент ИЛИ-НЕ 15, так как на вход управления режимом работы V подана логическая единица с выхода элемента ИCКЛЮЧАЮЩЕЕ ИЛИ, а на входы параллельной загрузки Do-Dv-1 подается код единицы. Код Х перепишется в регистр 6 по фронту импульса ССА. Описанная процедура соответствует на графе переходу из вершины 1 в вершину 1 по условию b.

Преобразователь кода 5 преобразует код Х в код Х1 (Х1≠ γk-3 ), который поступает на вторые входы блока сравнения кодов. В момент выделения селектором 3 синхросигнала третьего маркера на первые входы блока сравнения кодов поступит код имени третьего маркера γk-3 со вторых выходов декодера 2. Пассивный сигнал КС с выхода БСК 7, поступая на второй вход элемента И 12, закрывает его. Сигнал с выхода закрытого элемента И 12 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. На второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ поступает активный сигнал ПСБ с выхода счетчика 4. Счетчик 9 устанавливается в единицу по фронту сигнала ССА, так как на вход управления режимом работы V подана логическая единица, а на входы параллельной загрузки Do-Dv-1 подается код единицы. Код γk-3 перепишется в регистр 6. Описанная процедура соответствует на графе переходу из вершины 1 в вершину 1 по условию b.

Рассмотрим реакцию УОНБД на маркер с пораженным синхросигналом. Пораженный ошибками код синхросигнала со вторых выходов регистра 1 поступает на первые входы селектора 3 во время формирования сигнала переноса ПСБ с первого счетчика 4. Пассивный сигнал с выхода селектора 3, поступая на первый вход элемента И 12, закрывает его. Счетчик 9 устанавливается в ноль по фронту сигнала ПСБ, поступающего на вход С счетчика 9 через элемент ИЛИ-НЕ 15, так как в момент формирования переноса счетчика 4 активен сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 (логический ноль - на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и логическая единица - на его втором входе). Установка в ноль счетчика 9 будет происходит за счет записи в счетчик кода нуля с его входов параллельной загрузки Do-Dv-1. Описанная процедура соответствует на графе переходу из вершины 1 в вершину 0 по условию a.

Выделив пятый синхросигнал маркера из потока бит канального кода, селектор 3 вырабатывает сигнал ССА. Пассивный сигнал КС с выхода БСК 7 (на первые входы БСК подан код γk-5 со вторых выходов декодера 2, а на вторые входы подается код γk-4 с выходов преобразователя кодов), поступая на второй вход элемента И 12, закрывает его. Сигнал с выхода закрытого элемента И 12 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. Если на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ поступает активный сигнал ПСБ с выхода счетчика 4, то счетчик 9 устанавливается в единицу по фронту сигнала ССА, поступающего на вход С счетчика через элемент ИЛИ-НЕ 15, так как на вход управления режимом работы V подана логическая единица с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а на входы параллельной загрузки Do-Dv-1 подается код единицы. Если на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в момент выделения сигнала ССА поступает пассивный сигнал ПСБ с выхода счетчика 4 (в случае нарушения синхронизации выделителя после второго дефекта), то содержимое счетчика 9 (ранее установленного в ноль) увеличится на единицу по фронту сигнала ССА, так как на вход управления режимом работы V подан логический ноль с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. По фронту импульса ССА код γk-5 перепишется в регистр 6, и счетчик 4 сбрасывается в ноль. Описанная процедура соответствует на графе переходу из вершины 0 в вершину 1 по условию d.

В момент выделения селектором 3 синхросигнала шестого маркера на первые входы блока сравнения кодов поступит код имени шестого маркера γk-6 со вторых выходов декодера 2. Преобразователь кода 5 преобразует код γk-5 , поступающий на его входы с выходов регистра 6, в код γk-6, который поступает на вторые входы блока сравнения кодов. Активный сигнал КС с выхода БСК 7, поступая на второй вход элемента И 12, открывает его. Сигнал ССА через открытый элемент И 12 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14. На второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ поступает активный сигнал ПСБ с выхода счетчика 4. Содержимое счетчика 9 увеличивается на единицу по фронту сигнала ССА, поступающего на вход С счетчика через элемент ИЛИ-НЕ 15, так как на вход управления режимом работы V подан логический ноль с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Код γk-6 перепишется в регистр 6 по фронту импульса ССА. Описанная процедура соответствует на графе переходу из вершины 1 в вершину 2 по условию с.

Аналогично УОНБД отреагирует на седьмой, восьмой, .., r+4 маркер. Содержимое счетчика 9 будет увеличиваться на единицу по фронту сигнала ССА, а код имени последнего выделенного маркера будет переписываться в регистр 6. На графе это соответствует последовательным переходам по условию с в вершины 3, 4, ..., r.

При достижении счетчиком 9 состояния r завершается первый этап работы УОНБД - выделение r маркеров подряд (интервал А фиг. 3), и начинается второй этап - формирование временной задержки (интервал В фиг. 3).

Каждый маркер расположен от начала блока данных на расстоянии, определяемом именем маркера. В регистре 6 в момент окончания интервала А будет храниться код имени последнего маркера из выделенной последовательности r маркеров (код γk-r-4 , фиг. 3). Начало блока данных можно определить, меняя содержимое регистра 6 в интервале В каждый раз через l бит канального кода (период следования маркеров - l) по принятому закону следования имен маркеров до получения финального состояния γo.

Работает УОНБД в интервале В следующим образом.

При достижении счетчиком 9 состояния r на его выходе вырабатывается сигнал ФСС. Единичный потенциал на выходе счетчика 9 поступает: на третий вход элемента ИЛИ-НЕ 15, запрещая прохождение через элемент ИЛИ-НЕ 15 на вход С счетчика 9 сигналов ССА и ПСБ; на третий вход элемента И 13, открывая его; и на управляющие входы коммутаторов 10 и 11, в результате чего выходы этих коммутаторов логически соединяются с первыми их входами. Сигнал ФСС будет активен до тех пор, пока счетчик 9 не будет установлен в ноль сигналом СБРОС.

В интервале В УОНБД не реагирует на входную последовательность данных. Счетчик 4 сбрасывается в момент окончания импульса ПСБ, поступающего через коммутатор 11, на вход R счетчика 4. Сигнал переноса счетчика 4 через коммутатор 11 поступает на С вход регистра 6, вызывая запись в этот регистр кода следующего имени маркера, полученного путем преобразования блоком 5 ранее хранившегося в регистре 6 кода.

На выходе селектора кода 8 формируется логическая единица в случае наличия на его входах кода имени последнего маркера в маркерной последовательности. Сигнал ФСР с выхода селектора 8 поступает на первый вход элемента И 13.

Сигнал НД, индицирующий начало блока информации, вырабатывается на выходе элемента И 13 из сигнала ФСР путем стробирования его импульсом переноса счетчика 4.

Контроллер ВЗУ, в состав которого входит заявляемое устройство, получив сигнал НД, начинает прием блока информации по шине Dвых.

Рассмотрим пример реализации устройства для r = 2, k = 8, n = 8 и канального кода МФМ. Синхросигнал представляет собой последовательность восьми канальных бит вида 01000001. В устройстве используются две маркерные последовательности: первая для определения начала блока адресной информации, записанной отдельно; вторая для определения начала блока данных пользователя. Для кодирования имен маркеров используются полуслова смежного класса расширенного кода Хэмминга. Слова кода образуют две цепочки (для двух маркерных последовательностей), в которых вторая половина кодового слова является первой половиной следующего кодового слова. Все слова смежного класса приведены в таблице.

Минимальное кодовое расстояние между двумя словами в смежном классе равно 4. Таким образом при верном считывании синхросигналов неверное определение начала блока из-за искажений имен маркеров может быть лишь при поражении ошибками 4 или более бит кодов имен двух соседних маркеров.

При этом регистр 1 может быть выполнен на двух микросхемах типа К 555 ИР8, регистр 6 на микросхеме К 555 ТМ9, счетчик 4 на микросхеме К 555 ИЕ18, счетчик 9 на микросхеме К 555 ИЕ10, селектор 3 на микросхеме К 556 РТ4, блоки БСК, ПК, селектор 8, коммутаторы 10 и 11, элементы И 12 и 13, ИЛИ-НЕ 15, ИСКЛЮЧАЮЩЕЕ ИЛИ 14 могут быть выполнены на микросхеме К 556 РТ2.

Введение небольшого числа дополнительных несложных блоков приводит к уменьшению длины сдвигового регистра в r раз. При этом схема обнаружения маркеров вырождается в значительно более простую схему селектора кода.

Оценим возрастание объема оборудования прототипа и заявляемого устройства при увеличении r. В прототипе прямо пропорционально r возрастает разрядность (и следовательно число триггерных элементов) сдвигового регистра 1: η = lr. Причем l, как правило, довольно большая величина. В прототипе также прямо пропорционально r возрастает число входов схемы обнаружения маркеров, что приводит к пропорциональному увеличению числа логических элементов в схеме.

В заявляемом устройстве при увеличении r возрастает лишь разрядность счетчика 9, причем в логарифмическом масштабе: η = =log2(r+1).

Очевидно, поскольку объем оборудования прототипа возрастает значительно быстрее объема оборудования заявляемого устройства, существует такое r, при котором объем оборудования заявляемого устройства меньше объема оборудования прототипа. Определим это значение r в случае использования заголовка блока данных, приведенного в примере.

Случай r = 1 не представляет интереса: при этом и устройство [3] и заявляемое устройство вырождаются в устройство [1]. Сравним объем оборудования прототипа и заявляемого устройства при r = 2.

В устройство вводится следующее дополнительное оборудование: 4-разрядный регистр 6, блок сравнения двух 4-разрядных кодов 7, селектор 4-разрядного кода 8, 2-разрядный счетчик 9, 4-разрядный коммутатор на два входа 10, одноразрядный коммутатор на два входа 11, два элемента И 12 и 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент ИЛИ-НЕ 15.

В то же время разрядность сдвигового регистра 1 уменьшается с 32 разрядов до 16 разрядов. Разрязность счетчика 4 уменьшается с 7 разрядов до 4. От схемы выделения маркера прототипа, содержащей один селектор кода на 17 входов (один вход - стробирующий), семь селекторов кода на 16 входов, схему ИЛИ на 7 входов, схему И на два входа, в заявляемом устройстве остается один селектор кода на 9 входов (один вход - стробирующий).

Выразим разность объемов оборудования прототипа и заявляемого устройства в виде числа элементарных логических элементов И-НЕ. Инверсию сигналов на входах и выходах логических элементов учитывать не будем, так как она в основном используется в селекторах кода, число и разрядность которых в прототипе значительно больше, чем в заявляемом устройстве.

Введение счетчика 9 с учетом более сложной его организации примерно эквивалентно уменьшению разрядности счетчика 4. Введение 4-разрядного регистра 6 и уменьшение объема оборудования сдвигового регистра 1 на 16 триггеров дает в результате упрощение устройства на 12 D-триггеров, работающих по фронту, что эквивалентно 60 элементам И-НЕ на 2 входа и 12 элементам И-НЕ на 3 входа.

Блок сравнения 7 содержит 12 элементов И-НЕ на два входа и один на 4 входа. Селектор 8 содержит элемент И-НЕ на 4 входа. Коммутатор 10 содержит 12 элементов И-НЕ на 2 входа. Коммутатор 11 содержит 3 элемента И-НЕ на 2 входа. Элементы 12 и 13 могут быть реализованы с помощью элементов И-НЕ соответственно на 2 и 3 входа. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 может быть реализован с помощью 3 элементов И-НЕ на два входа. Элемент ИЛИ-НЕ 15 может быть реализован с помощью элемента И-НЕ на 3 входа. В итоге дополнительно введенные блоки (за исключением блоков 4 и 9) усложняют заявляемое устройство на 31 элемент И-НЕ на два входа, 2 элемента на 3 входа, 2 элемента на 4 входа.

За счет сокращения схемы обнаружения маркеров прототипа устройство упрощается примерно на 8 элементов И-НЕ на 16 входов.

Таким образом при обработке заголовка блока данных, приведенного в примере, и r=2 заявляемое устройство упрощается примерно на 29 элементов И-НЕ на 2 входа, 10 элементов И-НЕ на 3 входа, 6 элементов И-НЕ на 16 входов. При увеличении r упрощение устройства по сравнению с прототипом будет значительно больше.

Предусмотренное в устройстве использование для кодирования имен маркеров помехоустойчивого кода таким образом, что канкатенация любых r соседних маркеров является словом помехоустойчивого кода, позволяет минимизировать вероятность неверного обнаружения начала блока данных в случае поражения ошибками имен маркеров.

Вышеописанное кодирование может быть использовано в случае применения любого канального кода, имеющего слова постоянной длины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Устройство для синхронизации внешних блоков памяти | 1985 |

|

SU1254457A1 |

| Устройство для контроля многоканального аппарата цифровой магнитной записи | 1988 |

|

SU1607011A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Устройство для автоматического поиска участка записи на магнитной ленте | 1987 |

|

SU1515200A2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

Изобретение относится к вычислительной технике, а именно к внешним запоминающим устройствам (ВЗУ), и может быть использовано в контроллерах ВЗУ. Цель изобретения - упрощение устройства и повышение надежности определения начала блока данных. Упрощение достигается за счет перехода от параллельной обработки (r) маркеров к последовательной. При этом длина сдвигового регистра уменьшается в (r) раз, схема обнаружения маркеров вырождается в значительно более простую схему селектора кода. Повышение надежности определения начала блока данных достигается путем введения в устройство блоков и связей, позволяющих использовать кодирование имен маркеров помехоустойчивым кодом, таким образом, что канкатенация имен (r) соседних маркеров образует кодовое слово. 4 ил.

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАЧАЛА БЛОКА ДАННЫХ ВО ВНЕШНЕЙ ПАМЯТИ, содержащее сдвиговый регистр, информационный вход которого подключен к шине входных последовательных данных, синхровход - к шине тактовых импульсов, а вторые выходы - к первым входам первого селектора кода, первый счетчик, синхровход которого подключен к шине тактовых импульсов, преобразователь кодов, декодер канального кода, шину выходных параллельных данных, отличающееся тем, что, с целью упрощения устройства и повышения надежности определения начала блока данных, в него введены последовательно соединенные регистр, выход которого подключен к входу преобразователя кодов, второй селектор кодов, второй элемент И по его первому входу и шина начала данных, шина сброса, шина логического нуля, последовательно соединенные блок сравнения кодов, первый и второй входы которого подключены соответственно к второму выходу декодера канального кода и выходу преобразователя кодов, первый элемент И, другой вход которого подключен к выходу первого селектора кода, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход которого подключен к второму входу второго элемента И и к выходу переноса первого счетчика, два коммутатора, элемент ИЛИ - НЕ и второй светчик, выход которого подключен к третьему входу элемента ИЛИ - НЕ, третьему входу второго элемента И и управляющим входам первого и второго коммутаторов, выходы которых соединены соответственно с D-входом и C-входом регистра, подключенным к входу сброса первого счетчика, первый и второй входы первого коммутатора соединены соответственно с выходом преобразователя кодов и вторым выходом декодера канального кода, первый выход которого подключен к шине выходных параллельных данных, первый и второй входы второго коммутатора соединены соответственно с вторым входом второго элемента И, подключенным к первому входу элемента ИЛИ - НЕ, и с выходом первого селектора кода, подключенным к второму входу элемента ИЛИ - НЕ и к D0-входу второго счетчика, остальные D-входы которого подключены к шине логического нуля, вход управления режимом прием/счет - к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, C-вход - к выходу элемента ИЛИ - НЕ, R-вход - к шине сброса, а второй вход первого селектора кода соединен с шиной тактовых импульсов.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США N 4862443, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1994-12-15—Публикация

1991-07-02—Подача