j EECSri

-Ss

Изобретение относится к 1 г Г П Ггпт- тельной технике и может fih испо:1Ь- зовано в ;;истемах передач -: нигкрет- ной информации,

Цель изобретения - повымеиие т см хоустойчирости декодера зя {-чет обес печения :-арантi-ipoванного - сп ;анле:чия веех cTeijTbix симнолоз.

На фи;-, изображена б: ск-с:хема аналоговог о декодера кода с отгготч: - нальнымт проверками; на ги1 ,2--5 - ф у нк у д-ю н ные г х е fi,i с t; с. тв с т с т н е s-i -- но нодблока н блоке дегаилрйли П . формирователя ш-нтулъсов стираьия, лог н

ческо1 о бдс;ка н блока упг)авле пая; ла фиг,6-9 - примеры вынолис -- к глттиет- ственио -/зла сравнения : Myj ij- типлекемрования 5 узл- (ифраи.и:И;, селектора числа едини :, и )) пател/: сиглгалов у1:танопки на Фяг , 0 - временные дна; )аммы работы блока ления„

Анало -онын декодер (дск;;,т;ер с мягкпм решением, декодтер для приема в )делом,, декодер i полутгеирг-рыв- ном канале) содержит (фнт ,. ) с:: новнс1й сдвиг овый регистр 1, регистр 2 надеж}1ос тей, маужерный говый регис; 1 р 3, первый и в-орой мультинлекслзры 4 и 5; 6,, блок / дешифрании., блок 8 комму та ::,ии5 9 вьщеления макси гума, формз1ровател, ;0 импульсов стирания, блок I cyisi- маторов по модулю два. анализатор i i проверочных уравнений и блок 3 угг- равлеиия,, На фиг. 1 обозначены инфор- мадионный вход 14 вкод 15 над Ж}1Ос- тейр вход 16 дикловой сиихронизадки, вход 7 сбр оса и выход 18,.

Основно) и -иркер1к,1Й с:дБиг::)вые регистры 1 м 3 ii4eif)T по л рачря:1;ов г де п - длина кода.

Сдвиговый регистр 2 1адежностей в каждом из н своих разря;, ОЕ ссз/гержит га-разрядгггле буферьсые регис р : 1 для параллельнсп ; эзг;иси и сдвиг;- п-бит- иых кодовых комбина ий (сигналов) .

Блок 7 дешифрации служит для определения номеров наименьших из скольких с.овокупностей чисел, Он содержит г подблоков (г -- число кетпи- виальных ортогональных проверок); каждый из которьж выполнен (фиг,2) на узлах 19 сравнения, узлах 20 мулт)- типлексирования и узле 21 детифраиии На фиг, 2 обозначены входы 22 и вых Т- ды 23 подблока. Число входов 22 и

г ыходо -| 23 тавио чис:; - ;pflHi U сп MMiio.rioEj ,я;ч,г;-: ;;pf. лррочнг с внение KOJI- ,

;а 21 . 1 ии; ; отзетствуюшем па ;-г (.-: 1)

5

0

0

)лок 9 ныде,:шиия мз к г и;---; : л ::рсл- (;тгвляет co6oi: один подб. / (фиг . 2) , } лотг/рсм добаг лсч после;;);};) узе,1 20;;fi.-fi м;, лм liT: л Kciijic/Ba iifiH :

делен ПуНКТИрО -О , Н чХО;,Ы к: ; пр;); г- HtV ЛЯЮГСЯ nepniilMlI Яг:ХОДгм;; ллгкл ;) J ч

ВЫХОД) узла 2: uercujip-nuiH - - Topi---п )дами, М:)И лл1;-:г-1, - го гуля :;сялл;п Г{ л ;;а л,:х(;л-; v3j; 2; КОТ ; ; ,1Й со(1 т зе т;; н vc г л я к г i г-. аль /ю м

И - ЧМССЛ, К ;Л :., :- гл ; 1 il -qbдяе гея на выхол. V3j;ri ,ir /r,j

Формирователь )Э И invibi ч г т;---: :- ния выполн ен (фиг.З) па уялс- 2Д спн- пе;.ия (идентично:- узлгу iV -. ;;; 7 и 9), э:гементе 1Г 25, ( ггях i--- V. 26 ; элементах И 27. На .Ьи; . i .-,По-,на- чен1-)1 первые - трс тьи ижЬс р-; л ли и-и входы 28 - 30. Т равлЯ 0:цие f; -:n;:bi , 32 блокир;)вки и л,гхол.,: ; 3

лок 1 1 сумматором по --к.(улю дня С л ужи т для суммитк;ва ния л о мо;ду:л дна символов вхо, Л)01() к-лу;а. :-xoj tjnufx }( каждое из ортог-онач-.лых ч :;o ji:-;о - нь: урачнений. Он согто сг и:1 г . ров но мо/тулю дь;-5 хлдь - i :;; ключеиы к выходаь xoi - г к; j ,, n- iiUiX Г яярядов регистр;; 1, т,;- х ,LfOB , в КОТ01ЭЫХ тгт1иса;:ь: ос- .ч-; лы., -хо- дя):и-1е я данное ::ро-мерочное уТ) };ис л символ, для KO i Oporo i-;y:;; :iKC xjxix. - опальная система плояег; :;к тспвог- регистт:;;; 1 ) „

Анализатор 2 ту)овсрочмп х vi)aF:- e- иий служит для оп 5елсл лг,я л.ил чтл; к проверочных уравиулия. холл ixuiorn иестертого с.им1:ола и тки в ; гог.; сиг на.чои ис : pa ij cxv;; : г;е; :-ix ;xj и сигналов стирании в )е;ист ;1 j- Ана/1изатор 12 Bbtnojuie;- ((Ьи; , ) на г селекторах 34 числа сдили)., г форми- зователях 35 сигна ов ухт-а1:ськи, первом и втором э.ементе iOi ЗЬ и 3/, пергклм и втором узлах 38 и 39 пере- 1 ;л10чения, На фи::.4 обозначены ме1)ТЛ; е и вторые информадион}1ые нхс,;::;, 40 и 4, вход 42 блоки 5(, Срнме и что- оые выходь --З и 44 ,

Блок 13 управления выполнен (фиг.5) на первом и втором триггерах 45 и 46, элементе Ш1И 47 и элементе И 48. На фнг.5 обозначены первый - третий выходы 49 - 51.

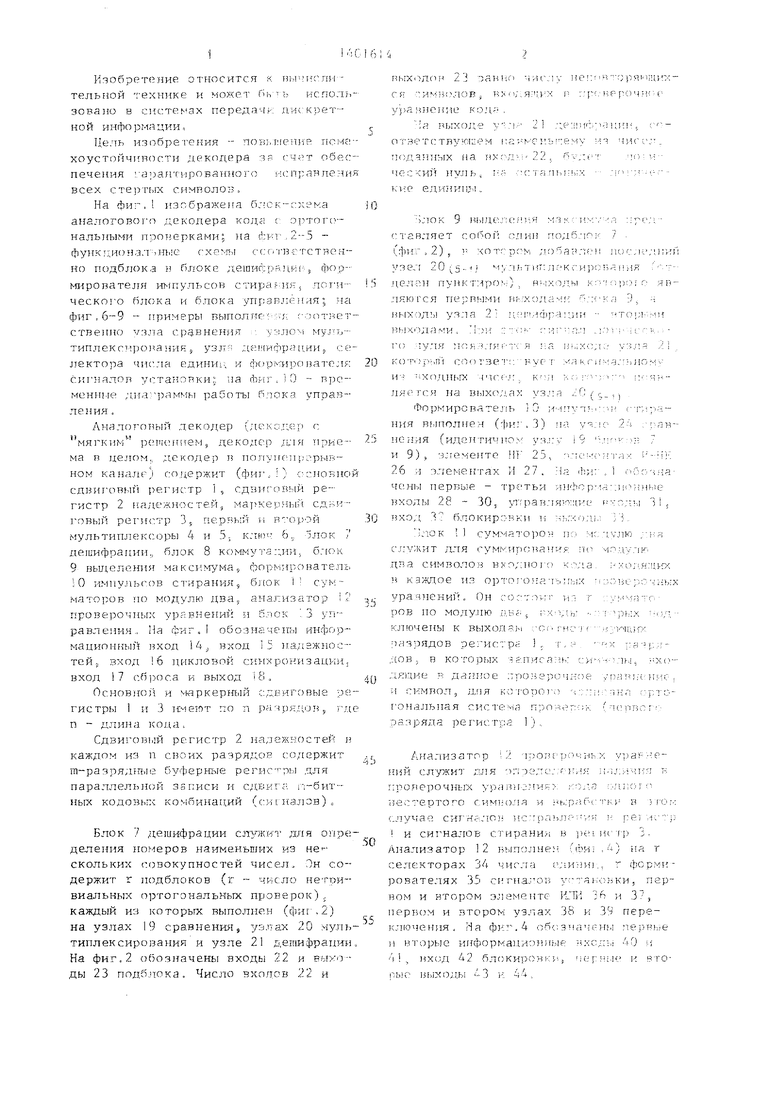

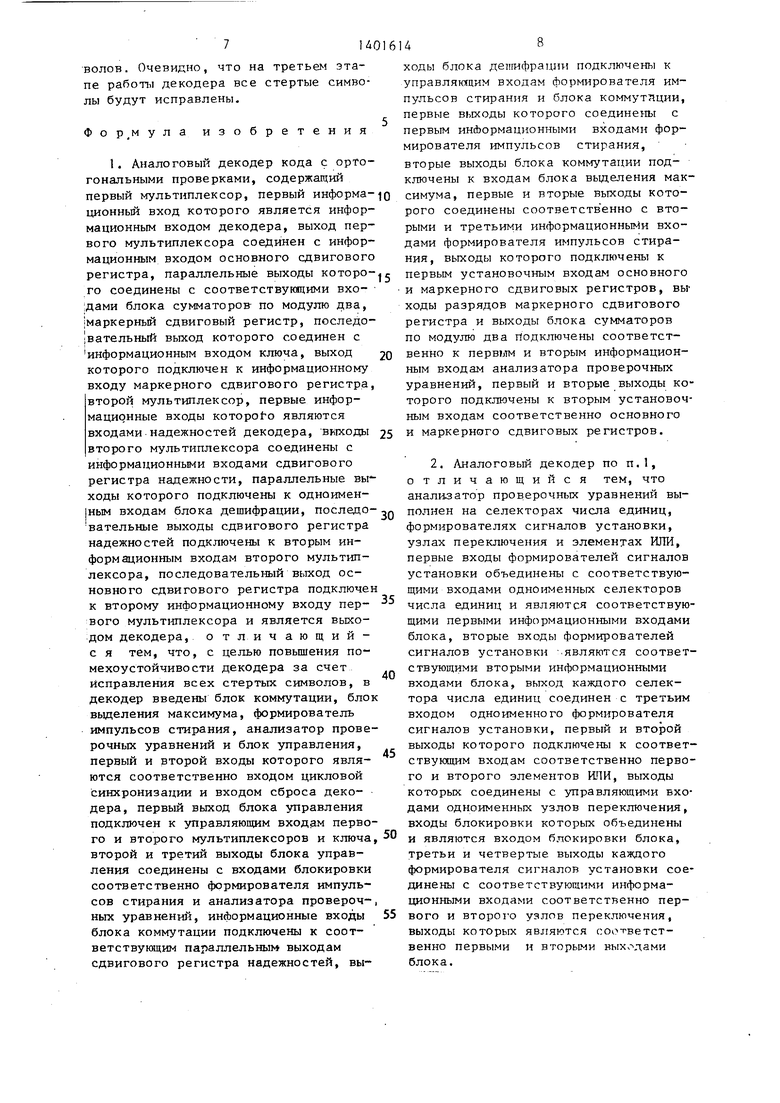

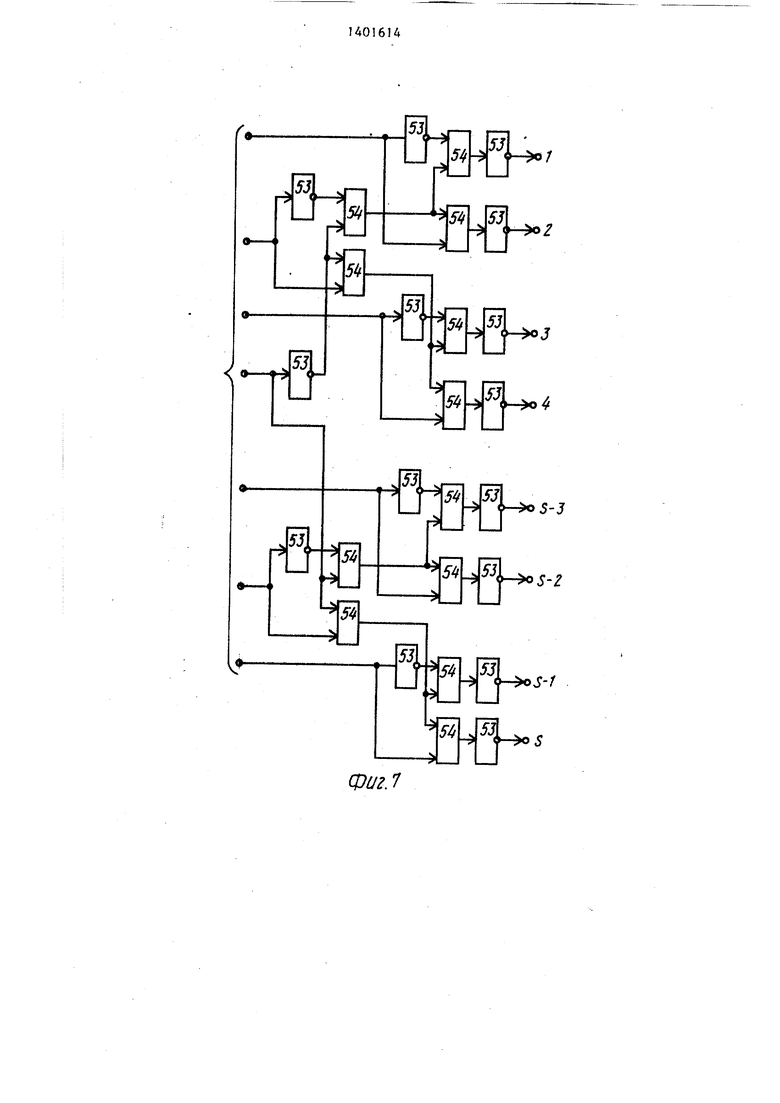

Узел 19 сравнения и узел 20 iyль- типлексирования блока 7, узел дешифрации блоков 7 и 9, селектор 34 и формирователь 35 анализатора 12 выполнены (фиг.6 - 9) на элементах ИС- КЛЮЧЛЮЩЕ;Е или 52, элементах НЕ 53, элементах И 54 и элементах ИЛИ 55. В узлах 20 мультиплексирования блока 9 необходимо выполнить соединения в соответствии с пунктирным перекрестием (фиг.6). В селекторе 34 (фиг.8) при увеличении числа входов следует добавить элементы, обведенные пунктиром. На фиг. 9 обозначены первые, второй и третий входы 56 - 58, первый, второй, третьи и четвертые выходы 59-62 формирователя 35 анализатора 12.

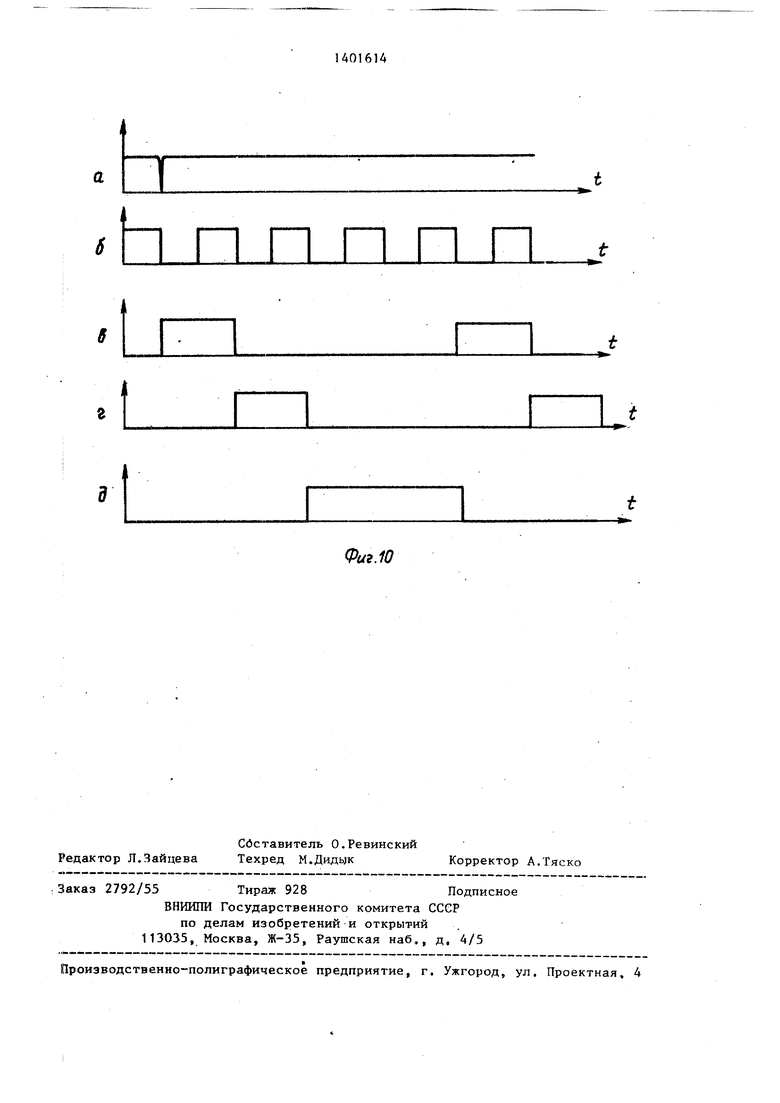

На фиг.10 обозначены следующие сигналы: а - на входе 17 сброса; б - на входе 16 цикловой синхронизации; в, г и д - на выходах 49-51 блока 13 управления,

Здесь логическому нулю соответствует высокий потенциал.

На фиг.1 не показаны цепи тактирования регистров 1 - 3.

Аналоговый декодер кода с ортогональными проверками работает следующим образом.

Перед началом работы декодера, после того как в системе связи достигнута устойчивая цикловая и тактовая синхронизация 5 на вход 17 сброса поступает импульс, устанавливающий блок 13 управления в исходное состояние, после чего декодер начинает декодировать nocTynapour jTo информацию.

Декодирование осуществляют в три этапа. Первый и второй из этих этапов длится п-периодов тактовой синхронизации каждый, а третий - 2п. В течение всех этих этапов тактовой синхронизации поступают на так- тируем1,е элементы (регистрь 1 - 3) , а управление режимом работы декодера производится при помощи блока 13 управления (фиг,10). На вход 16 блока 13 поступа от импульсы цикловой синхронизаггии, }тмс;К);ие частоту следование в п-раз частоты следования импульсов тактовой синхронизации. На перром кмходе 49 блока 13

0

5

0

5

5

0

, с

ИЗ .мх четь;рех ит- г}ульсоп цик.човой синхронизации устанавлира- ется логи ( еск)П1 О, подключающий к выходам мультиплексоров 4 и 5 их вторые и paз ыкaющий ключ 6. На остальных трех импульсах на первоь выходе 49 блока 13 - логииеская ; подключающая к выходам ьгультиплексо- ров 4 и 5 1-ж первые входы и замыкающая ключ 6. На втором выходе 50 блока 13 логическая появляется на каждом втором i-зшульсе цикловой синхронизации, а на остальных iis 5 импульсов - О. На третьем выходе 5 блока 13 логическая 1 появляется на каждом третьем и четвертом км- пульсаХ; и О - на первоь и втором. НЕ первом этапе га-битные С11г:- йлы, пропорццональ Гр надежностям символов кодовой комбинации параллельно поступают на вхоц второго мультиплексора 5 с входов 5 и записываются в сдвиговом peiHicrpe 2, Одновременно символы кодового слова с входа 14 проходят через мультиплексор 4 и записываются в основном сдвиговом регистре 1 „ с вь;хода которого результат декодирования предыдущего кодового слова поступает ма выход 8 декодера,, Маркерны;-: регистр 3 на этом таг;е заполняется нулями благодаря разомкнутому клтачу 6. На втором и третьем этапах р1згистры 1 - 3 работают i3 режиме циклического сдвига,: что обеспечивается состояниями чу. гьтип - : лексорор 4 :-: 5, а так же 6,

На первог- из п тактов второго этапа сигналь с рар1рядцых выходов сдвигового регистра 2, номера которых соответствуют :-iO iepaM символов, входящих в правые части уразнентлй ортогональной системы проверок, поступают на входы блока 7, в котором определя ются номера naHNfenee надежных символов. Эттг номера с выходов блока 7 поступают на управ.-тяюшие входы б.чока 8 коммутации формирователя 10 иь171ульсов стиранпя. На выходах блока 8 коммутации появля:-гтг,ч надежности найденных наи е1гее нйде:-;1гъ::ч символов , Наибольшая ii3 этих ;p;:H4ii;i надтежгчостей, пройдя блок 9 в:- 1йле11;.ш шксимума, поступает ня ;.-орые входы 29 йормп- рователя 10 т: Т1 льсор, стирани.я, .г периые 2R кг тппогс с пертшх ны- ходо} блока 8 Ki-r;:.iy попадает величина ;;я дсч;:;: Г-ти С 1 вола , о г ;оси- . тельпс , ортот-опальная сист -ема п : пверочп,р-; урявлемт. Если зтя надежность болТ), наибо ;ы 1е из найде1;г:-:,гх надежно с тей, то па пыхст цах форм; рэвателя 10 пок;ия с ; ситиалы, устанавлиБающие разр---;л, оч нсви о- го сдвиг |цого рг-гистрЯд :- о:-1ер.5 которых гпипадатт с номерам -; иайдаиных СгМволоя, н нулевое состс гг-цмг: (символы стиракил) 5 а соответсч Bvioiuvie разряды марке рно I d с-двисовс 141 ре{ ист : я 3 - в едиличнсе состоящее (гт1;:ртые символы зафиксируются) „/ Нало : нч}{ым обра:юм происходит раОота декодера H остальных л-тактах этого -«таг;;. Ни друпгх этачаХ; благодаря ,г;(- ис тпию сигнала блокировки, погт,( riro ;;i:My tta вход 32 г|11трмирователя «) 1,гпу:гьсон cтиpaJ ия с втг)рого В,:хода lO слока 13 yripaBjiein-iH, симБГчаы ио с- ира1 ггс:я и не фнксиоуготся,

На третьем этапе муль иплетихтры -t и 5 и 6 не ме ияют слоп о состояния. На первом из 2in тйл-стов сигналы с рая)ядньгх выходов маркерног О сдвиговот о регистра 3 Г1ос:тупач)т на первые входы анализатора 12 is кото-ром производится npOfiepKa наличие: в каждом И , проверочных урарч- ени;1 системы ор-огонал ьных npopjepoK одного стерто ;Т1 симвсча, Kcjih 1:1 каком- либо уравнении такое нати- чие обнаружится, то благодаря выходным сигиа-- лам анализатора 12, пос тупаюятим на вторые установочные вход;,.; основного и маркер;-:сл о сдвиговых pi;ivHCTpOB 1--i , стертьй символ направляется -гак, чтобы урав1; ень:е зь полняло ; ь, соо у-- ветствуниций разряд маркерного 1зегистра 3 устанавли а ется н к. улйвое состояние. Если не об наруже -( уравнений с единствеHHbiM Ртертым си1-1яолом5 тс кснравленке не производите:: :, Значение исправляемого символа :JHpeдeJ:яeт- ся но со(1тветствующему сигнатгу на выходе блока 1 1 5 в котором нроизнодитс суммирование по модулю два ::иг-« юлов , входящих н проверочное }/р;1зненр е ортогональной системы, Указгигчые проверки и иснравления проиэводлтс.я и на втором такте, причем циклрзмеский сдвиг содержимого регистрсп 1 - 3 не производится. ЛнaJIOгичяь образом происходит работа н а остальггых так-- тах этого этапа. На другш; этапах благодаря действикч сигнала блоккров- ки, посту1 аю1цего ка вход i2 анализатора 12 с третьего выхода 51 блока 13 упраяле.ния, иснравления симнол;:-/,-: не производятся.

верочн;1Я } ; R - синдпом чект М),-; ;coti6iueiM i .

JV GTOHOM . ay iC i Bh pa aio (i) n-k нси: вестн} ;х () г 1-гчи --а, :ь;-, - si-i значениями .адежио л-ей, Пг:з 4О;к- несть осущс ст ;:е иия laKfro слтязана с в М ) рл-нго Т -V .г инсйно ГС ;;.Висим| ГХ Vрачнсчсь . ( .;4jrraTbj чт-о VI:. е в|1 ;:ел счнь с :- ; PI-л :: с rfi)), а сие ; ::: - и ;7рпч :у -гцгчх Ч(ЧП1Й (I) ri :iHHi;Ma ет r.iyin-nit/v ;,и;: :

0

Ч

/де Н, и S - пое:7бра:чо:ча ;;; - ;n;ont- рочная ;-;а pujia с HHJ:- COO i-ii Т - н чо

Поскольку любое ПрОВ(; .);м ifi :Г r;;;iiнение может получено : v-rfr. ;-:: нейной комбина ;ии чокото - - / ;: )anii: НИЙ (2/5 то Нрк СГИ1)аЧИИ :Ч МЧСЧЮ}; Ч:

ос . аль гьк урач}-1ениях ;-;: :

С ,ГерТО никаких ДОПОЛЧН / -.-.:: -: Ч- Х HMiiO-лов., кроме сте1)тых в ула нсчия}; ( , ; . При исправлении симзоло}; ча - рс-тьем :г аг:е нри оассмотоении ;-ccfA ных уравнений кода -п yj-a--ч Ч и , нее (-тертые симзс: -.: Ч ;: ci ;- .

Таким образом,, чр- рас :, чг ; IPHJIL: пгех возможных чроверо -ич-.гх :-ч-а 1чс:ч- .ода будет стерто,, а i-i :ч;а;з.-с ;:О n-k симво.чон lori cTJH i bib;;;; : - гч-и:-:-- хо П|; Овсрочнь(Х уранно ий кс :-{оде ;- nbJTb не jiac смот r-eiio ;а jn:: - работь декодера, Чсег; -гчкс-: гк-- Hy iesrci lie бопее Ч(:Ч-1 Г:-k у:jc -ч; чти

де окажутся стео 1 ыми по ч,:;--lO - v i-;ojiy, Суммируя - (. n l нчх . в кото)и:с иходит один и : 11 же симчо:; . . :jwjic по.г;учить lie 1041;: е г-к--: чт Ч: -чо-ч-;он уранг ение ne::i c i ei: rb:x : т :-чс -ч- . ПичеЙЧЪГМН КОмбиН: 1:ИЯМИ :: Т Х , -.; .- i,;..,j,,;; iOKH j обра зона 74:- не бо.чее ч

волов. Очевидно, что на третьем этапе pa6oTiii декодера все стертые символы будут исправлены,

Ф о ула изобретения

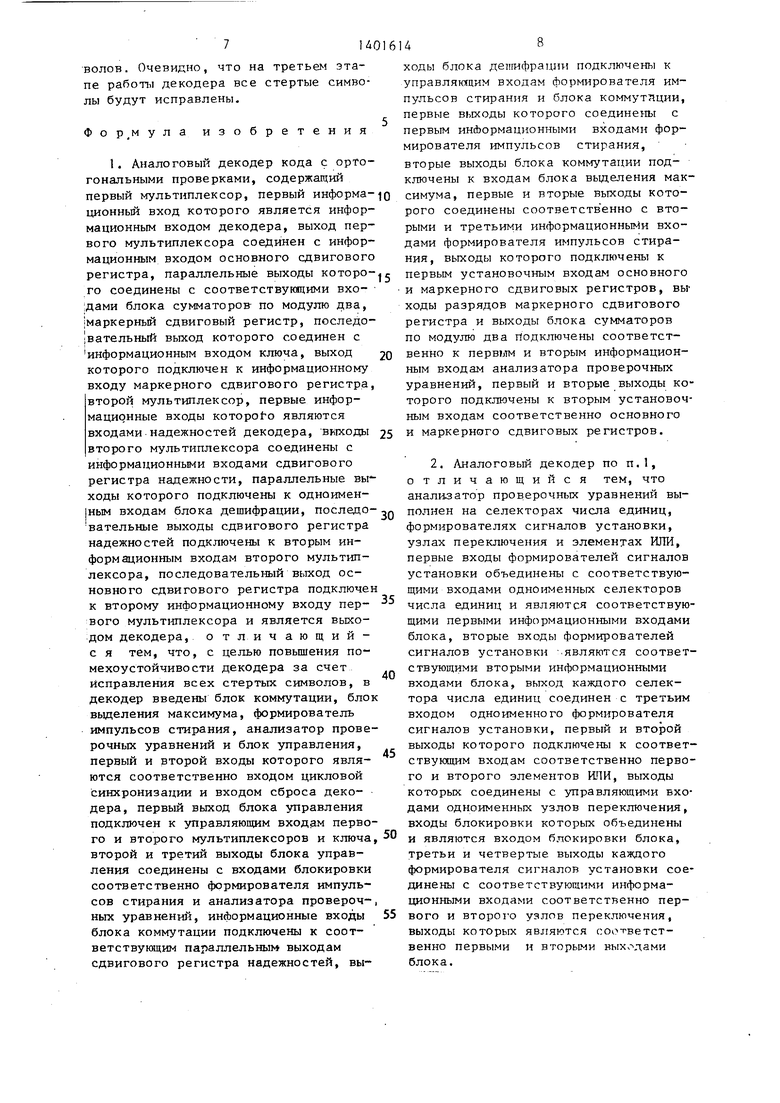

1. Аналоговый декодер кода с ортогональными проверками, содержащий первый мультиплексор, первый информационньй вход которого является информационным входом декодера, выход первого мультиплексора соединен с информационным входом основного сдвигового регистра, параллельные выходы которого соединены с соответствующими вхо- ;дами блока сумматоров- по модулю два, |маркерный сдвиговый регистр, последо- |вательный выход которого соединен с информационным входом ключа, выход которого подключен к информационному входу маркерного сдвигового регистра второй мультиплексор, первые информационные входы KOTOpofo являются входами надежностей декодера, второго мультиплексора соединены с информационными входами сдвигового регистра надежности, параллельные вы ходы которого подключены к одноимен- |ным входам блока дешифрации, последо- вательные выходы сдвигового регистра надежностей подключены к вторым информационным входам второго мультиплексора, последовательш11й выход основного сдвигового регистра подключен к второму информационному входу первого мультиплексора и является выходом декодера, отличающий- с я тем, что, с целью повышения помехоустойчивости декодера за счет исправления всех стертых символов, в декодер введены блок коммутации, блок выделения максимума, формирователь импульсов стирания, анализатор проверочных уравнений и блок управления, первый и второй входы которого являются соответственно входом цикловой синхронизации и входом сброса декодера, первый выход блока управления подключен к управляющим входам первого и второго мультиплексоров и ключа второй и третий выходы блока управления соединены с входами блокировки соответственно формирователя импульсов стирания и анализатора проверочных уравнений, информационные входы блока коммутации подключены к соответствующим параллельным выходам сдвигового регистра надежностей, вы

r 0 5 5

0

5

0

5

0

ходы блока депгифрации подключены к управляюгдим входам формирователя импульсов стирания и блока коммутации, первые выходы которого соединены с первым информационными входами формирователя импульсов стирания, вторые выходы блока коммутации подключены к входам блока выделения максимума, первые и вторые выходы которого соединены соответств енно с вторыми и третьими информационньЫи входами формирователя импульсов стирания, выходы которого подключены к первым установочным входам основного и маркерного сдвиговых регистров, вы ходы разрядов маркерного сдвигового регистра и выходы блока сумматоров по модулю два Подключены соответственно к первым и вторым информационным входам анализатора проверочных уравнений, первый и вторые выходы которого подключены к вторым установочным входам соответственно основного и маркерного сдвиговых регистров.

2. Аналоговый декодер по п.1, отличающийся тем, что анализатор проверочных уравнений выполнен на селекторах числа единиц, формирователях сигналов установки, узлах переключения и элементах ИЛИ, первые входы формирователей сигналов установки объединены с соответствующими входами одноименных селекторов числа единиц и являются соответствующими первыми информационными входами блока, вторые входы формирователей сигналов установки являются соответствующими вторыми информационными входами блока, выход каждого селектора числа единиц соединен с третьим входом одноименного формирователя сигналов установки, первый и второй выходы которого подключены к соответствующим входам соответственно первого и второго элементов ИЛИ, выходы которых соединены с управляющими входами одноименных узлов переключения, входы блокировки которых объединены и являются входом блокировки блока, третьи и четвертые выходы каждого формирователя сигналов установки соединены с соответствующими информационными входами соответственно первого и BTOpoi o узлов переключения, выходы которых являются соответственно первыми и вторыми выходами блока.

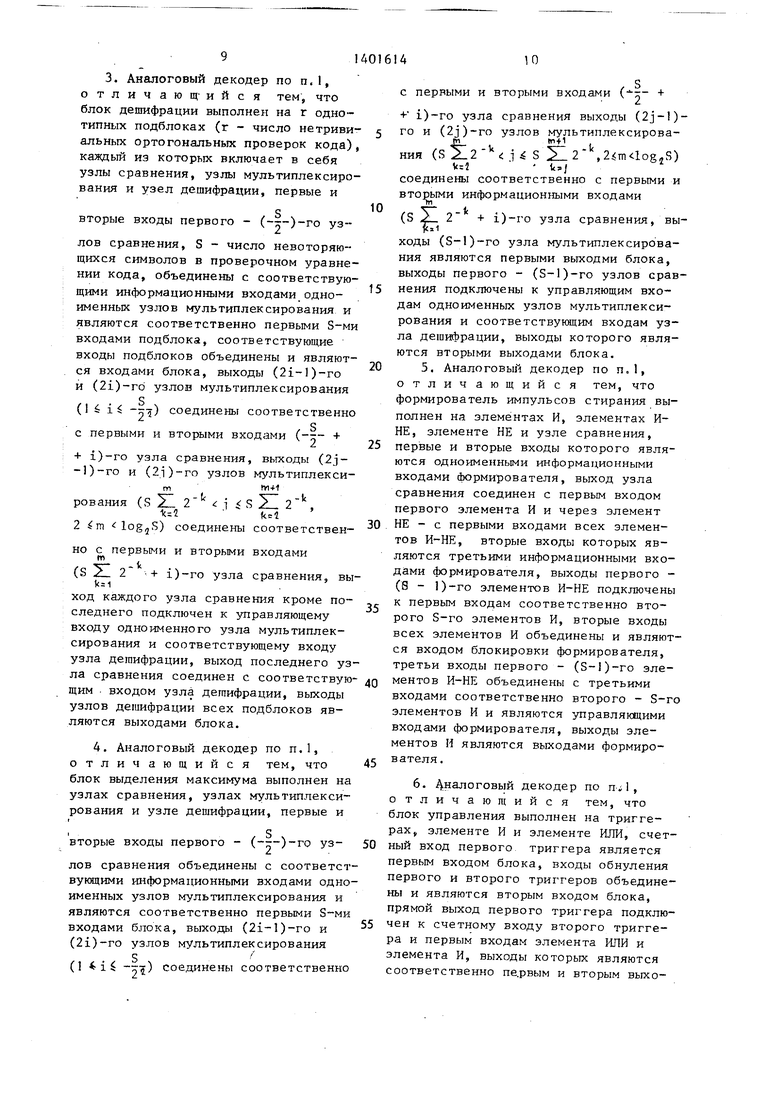

3. Аналоговый декодер по п.1, отличаю щ ийся тем, что блок дешифрации выполнен на г однотипных подблоках (г - число нетриви- альных ортогональных проверок кода), каждый из которых включает в себя узлы сравнения, узлы мультиплексирования и узел дешифрации, первые и

S

вторые входы первого - (---)-го узлов сравнения, S - число невоторяю- щихся символов в проверочном уравнении кода, объединены с соответствующими информационными входами одноименных узлов мультиплексирования и являются соответственно первыми S-ми входами подблока, соответствующие входы подблоков объединены и являются входами блока, выходы (21-1)-го

и (2i)-ro узлов мультиплексирования

g (1 6 i5 Tl) соединены соответственно

, S

с первыми и вторыми входами (-г- +

+ i)-ro узла сравнения, выходы (2j- -1)-го и (2i)-ro узлов мультиплекситW-H

, - t . , г -t

рования (S Z 2 i S 2 2 ,

2 im : log,jS) соединены соответственно с первыми и вторыми входами №

Г у 2 + i)-ro узла сравнения, вы .

ход каждого узла сравнения кроме по

следнего подключен к управляющему входу одноименного узла мультиплексирования и соответствующему входу узла дешифрации, выход последнего узла сравнения соединен с соответствую- щим . входом уэла дешифрации, выходы узлов дешифрации всех подблоков являются выходами блока.

4. Аналоговый декодер по п.1, отличающийся тем, что блок выделения максимума выполнен на узлах сравнения, узлах мультиплексирования и узле дешифрации, первые и

с

вторые входы первого - (---)-го узлов сравнения объединены с соответст- вукщими информационными входами одноименных узлов мультиплексирования и являются соответственно первыми S-ми входами блока, выходы (2i-l)-ro и (2i)-ro узлов мультиплексирования

S

(1 -94 соединены соответственно

0

5

Q

5

0

f ,

с первыми и вторыми входами +

+ i)-ro узла сравнения выходы (2J-1)- го и (2j)-ro узлов мультиплексироваmln + 1

ния (S 2l2 i ,2.m logjS)

izl t:-/

соединены соответственно с первыми и вторыми информационными входами

hi

г--- 4

(S А 2 + i)-ro узла сравнения, выТй

ходы (S-l)-ro узла мультиплексирования являются первыми выходми блока, выходы первого - (S-l)-ro узлов сравнения подключены к управляющим входам одноименных узлов мультиплексирования и соответствующим входам узла дешифрации, выходы которого являются вторыми выходами блока.

5.Аналоговый декодер по п.1, отличающийся тем, что формирователь импульсов стирания выполнен на элементах И, элементах И- НЕ, элементе НЕ и узле сравнения, первые и вторые входы которого являются одноименными информационными входами формирователя, выход узла сравнения соединен с первым входом первого элемента И и через элемент НЕ - с первыми входами всех элементов И-НЕ, вторые входы которых являются третьими информационными входами формирователя, выходы первого - (S - 1)-го элементов И-НЕ подключены к первым входам соответственно второго S-ro элементов И, вторые входы всех элементов И объединены и являются входом блокировки формирователя, третьи входы первого - (S-l)-ro элементов И-НЕ объединены с третьими входами соответственно второго - S-ro элементов И и являются управляющими входами формирователя, выходы элементов И являются выходами формирователя.

6.Аналоговый декодер по , отличающийся тем, что блок управления выполнен на триггерах, элементе И и элементе ИЛИ, счетный вход первого триггера является первым входом блока, входы обнуления первого и второго триггеров объединены и являются вторым входом блока, прямой выход первого триггера подключен к счетному входу второго триггера и первым входам элемента ИЛИ и элемента И, выходы которых являются соответственно пе.рвым и вторым выхоII140I6Uдами блока, инверсный выход второго триггера соединен с вторым входом элемента И, прямой выход второго

тр эл до

12

триггера подключен к второму входу элемента ИЛИ и является третьим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Аналоговый декодер расширенного кода Голея | 1988 |

|

SU1580566A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Аналоговый декодер кода Хэмминга | 1980 |

|

SU945986A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Аналоговый декодер кода Абрамсона | 1981 |

|

SU988165A1 |

| Аналоговый декодер расширенного кода Хэмминга | 1981 |

|

SU991607A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Декодер линейных кодов,исправляющий стирания | 1982 |

|

SU1112554A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи дискретной информации позволяет повысить помехоустойчивость декодера за счет обеспечения гарантированного исправления всех стертых символов. Аналоговый декодер кода с ортогональными проверками содержит основной сдвиговый регистр 1, сдвиговый регистр 2 надежностей, мар- кернь й сдвиговый рег истр 3, мультиплексоры 4, 5, 6( блок 7 деигиф- pauiiH; ГЗлок 11 сумматоров по модули два. Благодаря введению блока 8 коммутации, блока 9 выделения максим ма, формирователя 10 импульсов стирания, анализатора 12 проверочных уравнений и блока 13 ; т1равления в декодере обеспечивается исправле}-гие n-k стертых сиь5волов. 5 з.п. ф-лы, 10 ил. С2 9.

W,

I гУг1

28 29

tSi

tDi/z.l

Ф1/гЛ

f

77

5

Q

a

Т

rr

46

:

/

-

47

4

-

& 48

фиг. 5

Ц)иг.б

фигЛ

57 О-

OJ5,

9Л 29«ij г

59 61,

Фи.8

61г61з

OufS

Фи.Ю

| Колесник В.Д,, Мирончиков Е,Т | |||

| Декодирование циклических кодов | |||

| - М.: Связь, 1968, с, 103-108 | |||

| Аналоговый декодер кода Хэмминга | 1980 |

|

SU945986A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-07—Публикация

1986-08-07—Подача