1

:

;о Изобретение относится к регулирующим и управляющим системам общего назначения и может быть исполь зовано для испытания, контроля и диагностики неисправностей устройст ввода-вывода двоичной информации, представленной в виде кодовых комби наций. По основному авт„ св. № 1038926 известно устройство, содержащее блок элементов И, блок задания начального кода, первым входрм соединенный с выходом первого формирователя и с первыми входами блока элементов И, вторые входы которого подключены к выходам блока задания начального кода, и последовательно соединенные генефатор импульсов, счетчик импульссв, дешифратор и вто рой формирователь импульсов, выход которого соединен с R-входом счетчика импульсов, входом первого формирователя импульсов и входом генератора импульсов, а также блок управления, блок сумматоров, -ра-гистр числа, дополнительный элемент И, блок установки адреса и ком мутатор, выходами через регистр числа соединенный с выходами устрой ства, с первыми входами коммутато ра и блока сумматоров,вторые входы которого подключены к выходам блока задания начального кода, вторым входбм соединенного с входом второго формирователя импульсов и с первым выходом блока управления, второ выход которого соединен с вторым входом коммутатора, третьи входы коммутатора соединены с первыми выходами блока сумматоров, Рд-гвыход переноса которого подключен к PJQвходу переноса блока сумматоров, третий выход блока управления соеди нен с первым входом дополнительного элемента И, вторым входом подключен ного к выходу генератора импульсов, выходом - к С-входу регистра числа, вторые входы которога соединены с выходом блока элементов И, блок установки адреса выходом соединен с S-входами счетчика импульсов, в котором блок задания начального кода содержит элемент И, переключатель, установочный регистр и последовательно соединенные элемент задержки, элемент И-НЕ и сдвигающий регистр, выходами подключенный к вы ходам блока, первый вход элемента И соединен с входом блока, второй вход - с переключателем, а выход с С -входом сдвигающего регистра, С.-вход которого соединен с выходом элемента задержки, Уу,-вход - с выходом D-входы - с выходами установочного регистра, первыми входами подключенного к шине логической 1, а вторыми входами - к шине логического О, второй вход элемента И-НЕ соединен с входом блока, первый вход переключателя подключен к шине логической 1, а второй вход - к шине логического О. Устройство обеспечивает формирование проверочных тестов типа псевдослучайный, сдвиговый, шахматный, постоянный коды, а также тест с упорядоченной структурой двоичных кодов, изменяющихся по принципу +1. Эти тесты позволяют проверить радиоэлектронные блоки в том числе и блоки с многоадресной оперативной памятью. В данном устройстве первый разряд адреса при последовательной смене адресов изменяет свое состояние при каждом очередном обращении к ЗУ. Второй разряд адреса меняет свое значение через два такта (через два адреса), а третий разряд - череэ четьфе такта и т.д. т.е. каждый следующий разряд адреса переключается в два раэа реже предыдущего. Последний разряд адреса сменит свое состояние один раз при переходе во вторзто половину адресов проверяемого ОЗУ f13. Однако проверка адресной части контролируемого блока в различных разрядах адресных шин происходит с разной частотой смены кодов. При этом лишь первый разряд подвергается активному воздействию кодами с максимальной частотой смены символов. Другие же разряды адресных шин не проверяются на максимальное быстродействие, что снижает достоверность проверки радиоэлектронных блоков с памятью. Особенно это сказывается в полупроводниковых ЗУ, содержащих адресные дешифраторы внутри микросхемы. В таких ЗУ необходимо проверять устойчивую работу при предельных (минимальных) временных соотношениях составляющих времени цикла по различным адресным цепям с целью проверки воспроизводимости динамических параметров на идентичность

цепей ЗУ по времени задержки в адресном дешифраторе.

Целью изобретения является повышение достоверности контроля и расширение области применения устройст на путем проверки на максимальное быстродействие каждого разряда адресных шин.

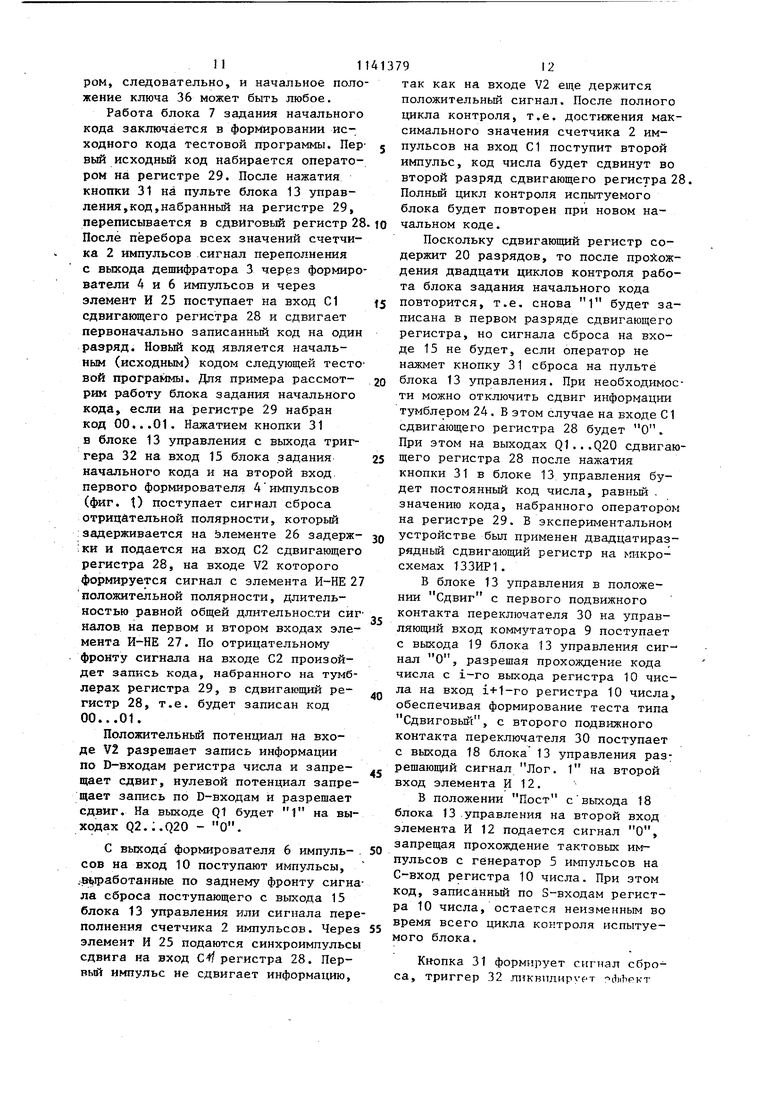

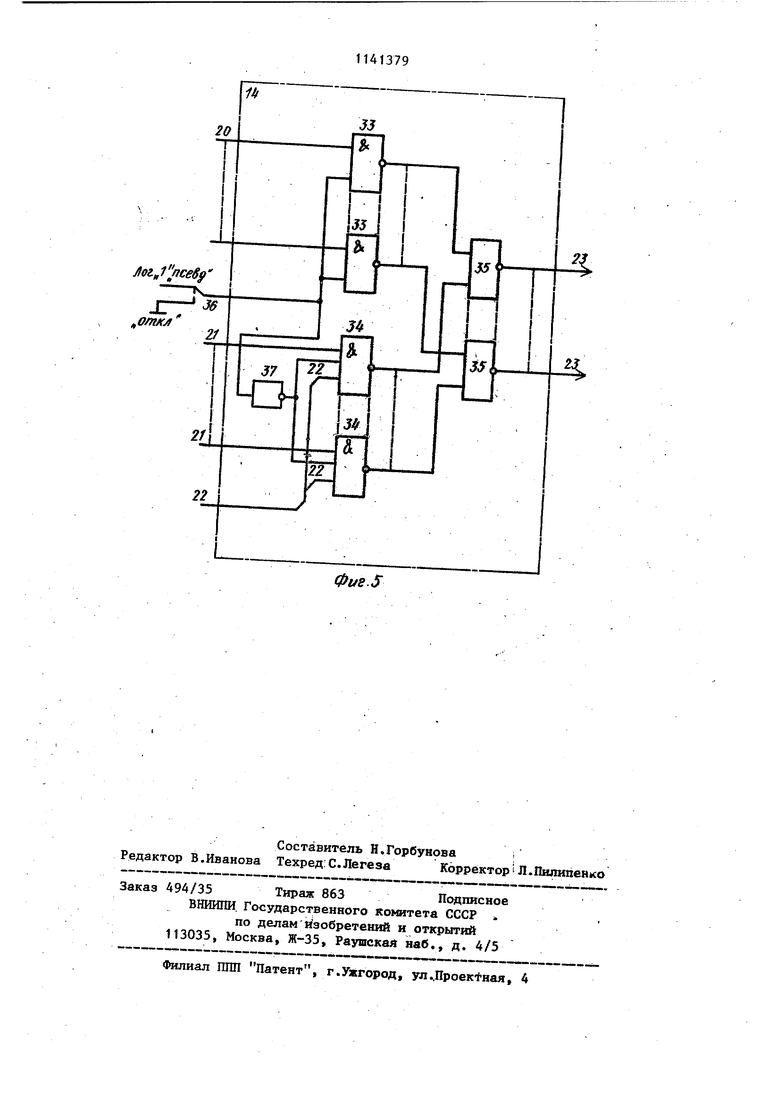

Поставленная цель достигается тем, что в устройство введены переключатель режимов и коммутатор адреса, содержащий группы вторых, третьих и четвертых элементов И-НЕ, элемент НЕ, подключенньй входом к первым входам вторых элементов И-Н а выходом - к первым входам третьих элементов И-НЕ, соединенных вторыми входами с соответствующими вторыми выходами блока установки адреса, третьими входами - с соответствуйщи ми разрядными выходами счетчика импульсов, а выходами - с первыми входами четвертых элементов И-НЕ, подключенных вторыми входами к выходам вторых элементов И-НЕ, связанны вторыми входами с соответствующими выхода Ш регистра числа, а первыми входами через переключатель режимов с шинами Логический О и Логическая 1, причем выходы четвертых элементов И-НЕ являются адресными выходами устройства.

В предлагаемом устройстве для задания тестов цель достигается рутем трансляции двоичных кодов через вновь введенный коммутатор адреса, группу входов которых поступают упорядоченные коды с выходов счетчика импульсов, а на другую группу входов - коды с выхода регистра числа, образующего совместно с сумматором, коммутатором числа и блоком задания начального кода генератор псевдослучайных чисел, который при этом устанавлива ётся оператором в режим формирования упорядоченных кодов с циклическим сдвигом начального кода тестовой программы. В этом слзгчае при включении оператором в коммутаторе адреса управляющего ключа на адресные выходы устройства через коммутатор адреса будут проходить коды, реализующие проверку каждого разряда адреса проверяемого блока на мак симальнсе быстродействие. При отключении в коммутаторе управляницего ключа на адресные выходы через коммутатор адреса будут проходить упорядоченные коды с выходов счетчика импульсов.

Существенным отличийуц известного устройства от предл аг аеного являетс наличие в последнем коммутатора адрса, который позволяет использовать имеющийся в составе известного устройства генератор псевдослучайных чисел для формирования программы опроса адресов, обеспечивающих проверку с одинаковой достоверностью всех разрядов адреса на максимальное быстродействие во всем информационном объеме проверяемой памяти.

Известны устройства, позволяющие проверять динамические характеристи-ки адресных входных цепей запоминающих устройств галопирующими тестами. Принцип контроля блоков памяти галопирующими тестами основан на организации проверки всех возможных адресных переходов. Это осуществляется последовательной выборкой каждого адреса после воздействия на все другие адреса. При этом обращения производятся в следзпощей последовательностй смены адресов;

1-й цикл 0-0-1-0-2-0-3-0-4-0...0(N-1), где 0,1,2,3.... номер адреса;

2-й цикл 0-1-1-1-2-1-3-1-4-...1(N-1);

3-й 1ЩКЛ. 0-2-1-2-2-2-3-2-4-2...2(N-1);

(Ы-1)-й цикл 0-(N-1)-1-(N-1)-2(N-1)-3- ;

) ... ... (N-I)-(N-I).

Такая организация обеспечивает j все возможные адресные переходы :и определенную динамику смены сигналб вПв каждом разряде адресных шин. Но при этом не обеспечивается проверка каждого разряда адресных шин на максимальную частоту смены сигналов. Это видно, если расписать кодовые комбинации, поступающие на адресные шины испытуемого блока памяти

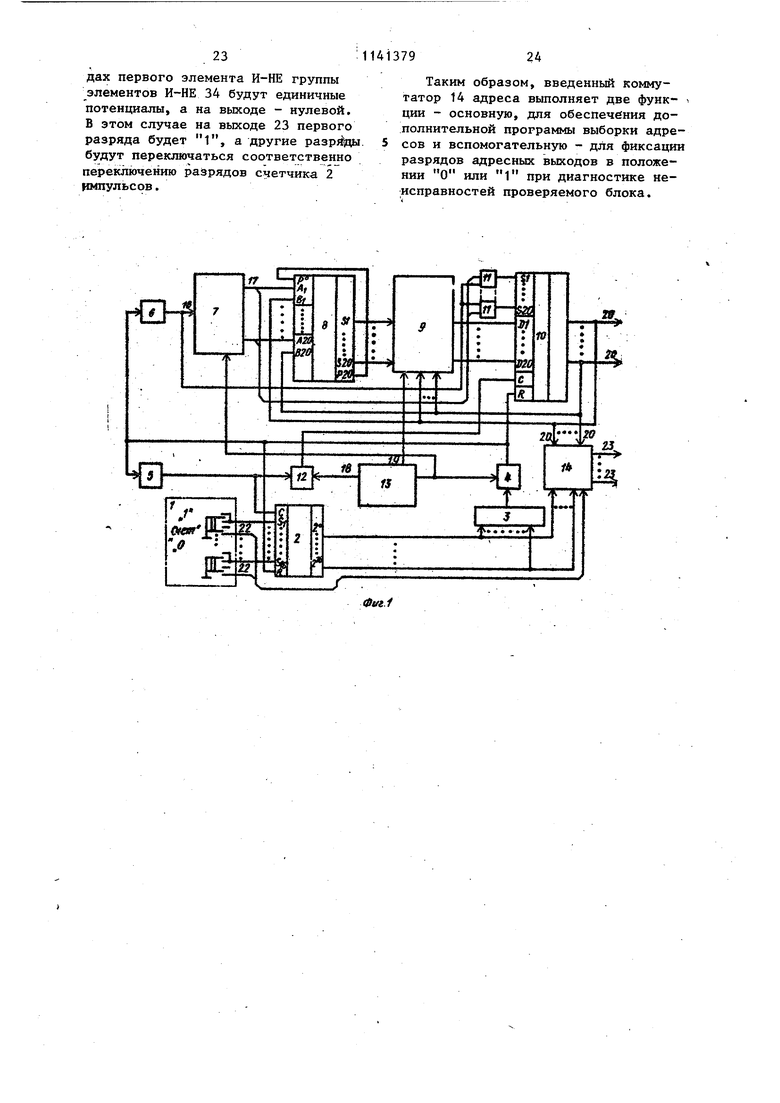

1-й цикл ;№ адреса :0 0...0 О О О

О 0...0 О О , 1 0...0 О 1

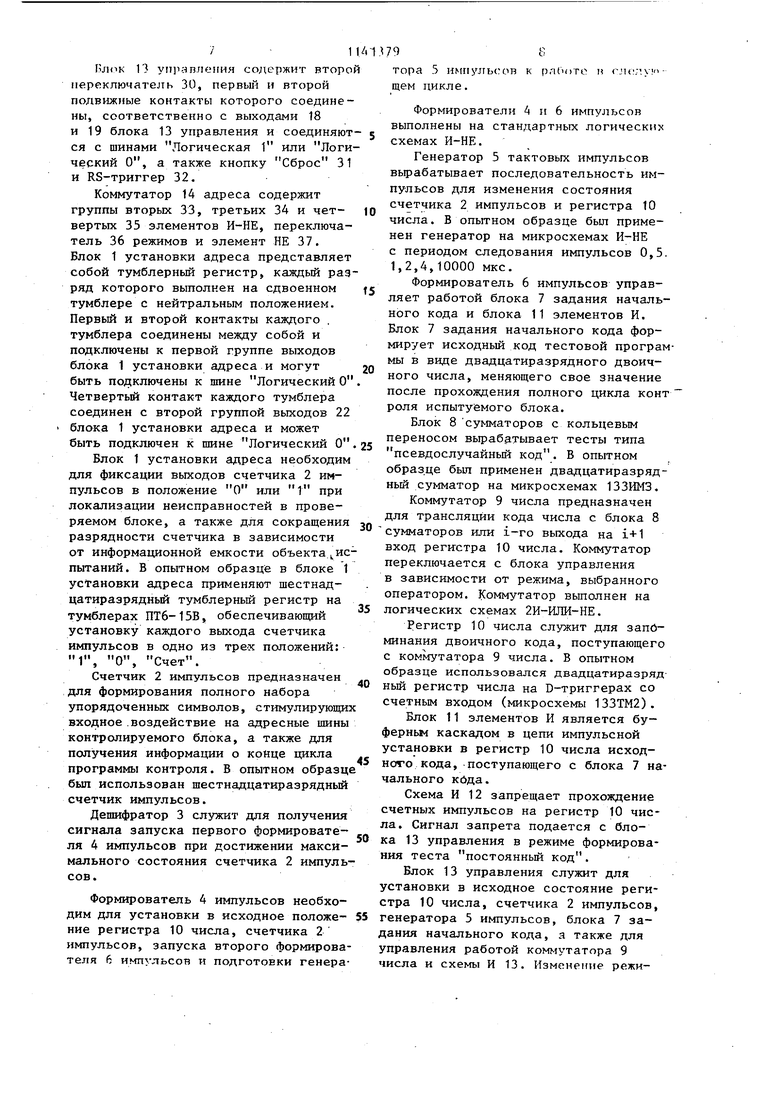

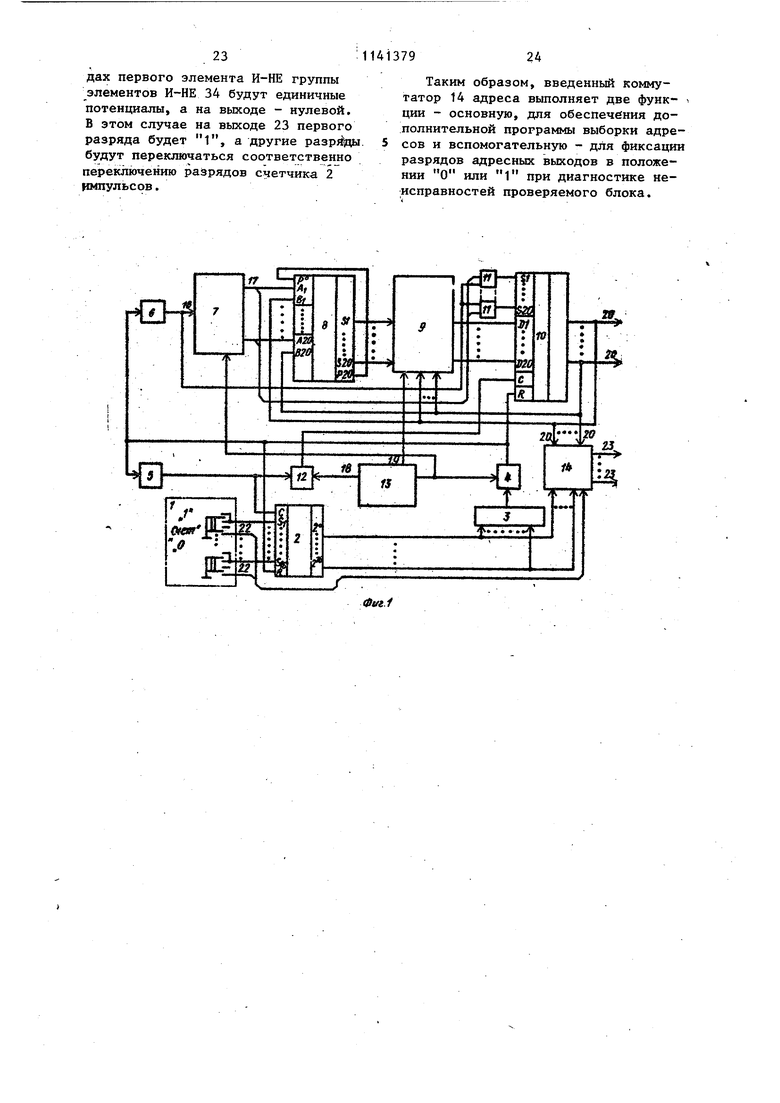

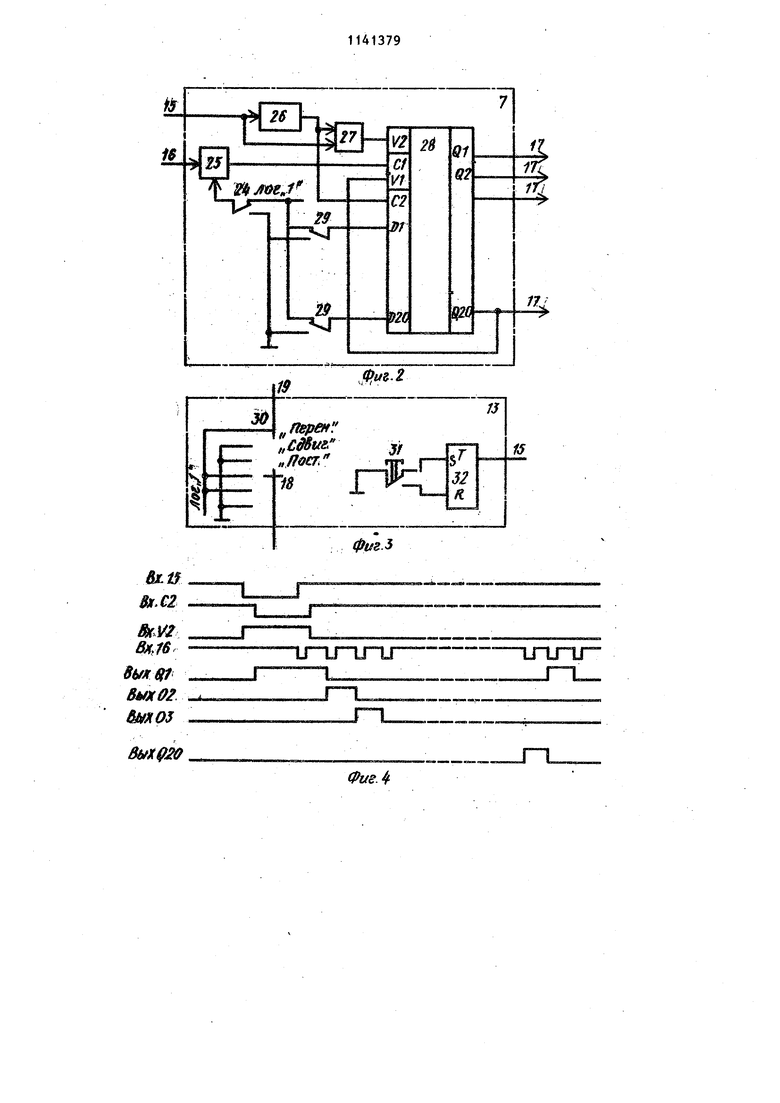

о 0...0 о о О,..О 1 О 0...0 О О О..,0 1 1 0...1 о о 0...0 о о ..О О о 1 0.. N-1 1 1,..1 1 (N-1)-и цикл № адреса 0...0 О О1...1 1 1 О...О О 1 1...1 1 1 0...0 1 О 1...1 1 1 0...0 1 1 1...1 1 1 1...1 1 1 1... 1 1 1 Из этих кодовых последовател ностей видно, что определенная сигналов в каждом разряде адрес обеспечивается, но воздействие симальной частотой смены сигнал в каждом разряде обеспечивается лишь на отдельных участках адре что снижает достоверность прове адресных входов полупроводников микросхем. Кроме того, полная п ка всех адресных переходов осущ ляется за N циклов контроля, каждый из которых содержит N тактов обращения. Следовательно, полный контроль запоминающего устройства осуществляется за N обращения. Известны микросхемы (например, МК 4164 (США) информационной емкостью 64К слов ( ) . В этом случае полный контроль всех адресных переходов галопирующим тестом осуществится за 2х(2) обращений (где 2 - учитывает цикл записи и считывания). Изобретение обеспечивает проверку динамических характеристик каждого разряда адресных шин испытуемых полупроводниковых запоминающих устройств за 2x20N обращений (при потребуется 2x20x2 обращений) , что значительно быстрее, чем проверка галопирующим тестом. При этом обеспечивается полная проверка на максимальное быстродействие каж- цого разряда адресных шин. На фиг. 1 приведена функциональная схема устройства для задания тестов; на фиг. 2 - принципиальная схема блока задания начального кода; на фиг. 3 - принципиальная схема блока управления; на фиг. 4 - времен-, ная диаграмма работы блока задания начального кода; на фиг. 5 - принципиальная схема коммутатора адреса. Устройство (фиг. 1) содержит блок 1 установки адреса, счетчик 2 импульсов, депшфратор 3, второй формирователь 4 импульсов, генератор 5 тактовых импульсов, первый формирователь 6 импульсов, блок 7 задания начального кода, блок 8 сзгмматоров, коммутатор 9, регистр 10 числа, блок 11 элементов И, дополнительный элемент И 12, блок 13 управления, коммутатор 14 адреса, первый выход 15 блока управления, выход 16 первого формирователя импульсов, выходы 17 блока задания начального кода, второй 18 и третий 19 выходы блока управления, выходы 20 регистра числа, выходы 21 счетчика импульсов, вторые выходы 22 блока установки адреса, адресные выходы 23 устройства. Блок 7 задания начального кода содержит переключатель 24, элемент И 25, элемент 26 задержки, элемент И-НЕ 27, сдвиговый регистр 28, установочньй регистр 29. / 1 Iiji(iK 13 yiT)(HH содержит второ переключатель 30, первьш и второй подвижные контакты которого соединены, соответственно с выходами 18 и 19 блока 13 управления и соединяют ся с шинами Логическая 1 или Логи ческий О, а также кнопку Сброс 31 и RS-триггер 32. Коммутатор 14 адреса содержит группы вторых 33, третьих 34 и четвертых 35 элементов И-НЕ, переключатель 36 режимов и элемент НЕ 37, Блок 1 установки адреса представляет собой тумблерный регистр, каждый раз ряд которого выполнен на сдвоенном тумблере с нейтральным положением. Первый и второй контакты каждого , тумблера соединены между собой и подключены к первой группе выходов блока 1 установки адреса и могут быть подключены к шине Логический О Четвертьй контакт каждого тумблера соединен с второй группой выходов 22 блока 1 установки адреса и может быть подключен к шине Логический О Блок 1 установки адреса необходим для фиксации выходов счетчика 2 импульсов в положение О или Т при локалиэации неисправностей в проверяемом блоке, а также для сокращения разрядности счетчика в зависимости от информационной емкости объекта ис пытаний. В опытном образце в блоке 1 установки адреса применяют шестнадцатиразрядный тумблерный регистр на тумблерах ПТ6-15Б, обеспечивающий установку каждого выхода счетчика импульсов в одно из трех положений: 1, О, Счет. Счетчик 2 импульсов предназначен для формирования полного набора упорядоченных символов, стимулирующих входное .воздействие на адресные шины контролируемого блока, а также для получения информации о койце цикла программы контроля. Б опытном образц был использован шестнадцатиразрядный счетчик импульсов. Дешифратор 3 служит для получения сигнала запуска первого формирователя 4 импульсов при достижении максимального состояния счетчика 2 импульсов. Формирователь 4 импульсов необходим для установки в исходное положание регистра 10 числа, счетчика 2 импульсов, запуска второго формирователя 6 импульсов и подготовки генера98тора 5 и rIyJть(:on к р.-Пото и г.П(;. цикле. Формирователи 4 и 6 импульсов выполнены на стандартных логических схемах И-НЕ. Генератор 5 тактовых импульсов вырабатывает последовательность импульсов для изменения состояния счетчика 2 импульсов и регистра 10 числа. Б опытном образце был применен генератор на микросхемах И-НЕ с периодом следования импульсов 0,5. 1,2,4,10000 МКС. Формирователь 6 импульсов управляет работой блока 7 задания начального кода и блока 11 элементов И. Блок 7 задания начального кода формирует исходный код тестовой программы в виде двадцатиразрядного двоичного числа, меняющего свое значение после прохождения полного цикла конт роля испытуемого блока. Блок 8 сумматоров с кольцевым переносом вьфабэтывает тесты типа псевдослучайный код. Б опытном образде был применен двадцатиразрядньй сумматор на микросхемах 133ИМЗ. Коммутатор 9 числа предназначен для трансляции кода числа с блока 8 сумматоров шти i-ro выхода на i+1 вход регистра 10 числа. Коммутатор переключается с блока управления в зависимости от режима, выбранного оператором. Коммутатор вьтолнен на логических схемах 2И-ИЛИ-НЕ. Регистр 10 числа служит для запбминания двоичного кода, поступающего с коммутатора 9 числа. В опытном образце использовался двадцатиразрядный регистр числа на D-триггерах со счетным входом (микросхемы 133ТМ2). Блок 11 элементов И является буферньм каскадом в цепи импульсной установки в регистр 10 числа исходного кода, -поступающего с блока 7 начального кбда. Схема И 12 запрещает прохождение счетных импульсов на регистр 10 числа. Сигнал запрета подается с блока 13 управления в режиме формирования теста постоянньй код. Блок 13 управления служит для установки в исходное состояние регистра 10 числа, счетчика 2 импульсов, генератора 5 импульсов, блока 7 заания начального кода, а также для правления работой коммутатора 9 исла и схемы И 13. Изменение режи91MOB работы осуществляет оператор с помощью кнопки и переключателя, вы веденных на панель управления. Коммутатор 14 адреса, в зависимос ти от положения переключателя 36, пропускает двоичньй код с выходов 2 счетчика 2 импульсов или с выходов 2 регистра 10 числа на адресные выходы 23 устройства. Устройство работает следукнцим образом. Начальное состояние блоков устрой ства определяется положением установочных тумблеров в блоке 1 установ ки адреса, переключателя 24 и установочного регистра 29 в блоке 7 задания начального кода, переключателя 30 и кнопки 31 в блоке 13 управления, переключателя 36 в коммутаторе 14 адреса. Положение тумблеров в блоке 1 установки адреса определяет количест во разрядов, работающих в счетном режиме в счетчике 2 импульсов, в зависимости от информационной емкости испытуемых многоадресных блоков памя ти. Например, при проверке блока информационной емкостью 8К слов (8192 слова 2 ) первые тринадцать тумблеров должны быть установлены в нейтральное положение, а остальные тумблеры - в нулевое. При этом первы тринадцать разрядов 2 счетчика импульсов будут работать в счетном режиме, а 14-16 разряды установлены в состояние 1, так как на 14-16 S-входы счетчика 2 импульсов поступят нулевые потенциалы. Положение переключателя 24 в бло ке 7 задания начального кода опреде ляет режим работы этого блока. При включении переключателя 24 блок 7 задания начального кода работает в режиме сдвига исходного кода, набранного оператором на установочном (тумблерном) регистре 29, после пол ного перебора состояний счетчика 2 импульсов о При отключении переключа теля 24 блок 7 задания начального кода будет иметь всегда на выходах 1 информацию, равную набранной на регистре 29, так как сдвиг информации будет запрещен на элементе И 25. Сл довательно, исходное состояние блока 7 определяется выбранным, с помощью переключателя 24 режимом рабо ты блока 7 задания начальнсго кода и ис ходным кодом, набранным на регистре 29 10 Положение переключателя 30 в блоке 13 управления определяет режим работы устройства при формировании тестов типа постоянньй код, сдвиговый код, псевдослучайный код. В положении Пост переключателя 30 на выходах 20 регистра 0 числа код будет иметь значение кода на выходах 17 блока 7 задания начального кода. В положении Сдвиг переключателя 30 информадая на выходах 20 регистра 10 числа будет сдвигаться на один разряд относительно кода на выходе 17 блока 7 задания начального кода при каждом такте работы устройства (т.е. при изменении состояния счетчика 2 импульсов на -(-1). В положении Перем переключателя 30 информация на выходах 20 регистра числа 10 будет изменяться по псевдослучайному закону в зависимости от кода на выходах 17 блока 7 задания начального кода. Начальное положение переключателя 30 может быть произвольным к зависит от выбранного оператором режима формирования тестов. Кнопка 31 в блоке 13 управления в исходном состоянии обеспечивает подачу на триггера 32 потенциала О, а на R-вход,- 1. При этом на выходе 15 триггера 32 будет 1 При нажатии на кнопку 31 на выходе 15 будет О, обеспечивая формирование сигнала начальной установки для блока задания начального кода 7 через формирователь 4 импульса, представляющий собой элемент И, сигнал начальной установки отрицательной полярности поступает на R-вход регистра 10 числа, устанавливая его в начальное состояние (состояние О). Положение переключателя 36 в коммутаторе 14 адреса обеспечивает прохождение двоичных кодов со счетчика 2 импульсов или с выхода регистра 10 числа. При этом, если ключ 36 установлен в положение Псевд, то разрешается прохождение чисел с выхода регистра 10 числа через коммутатор 14 адреса на выходы 23 устройства, а при отключении ключа 36 коммутатор 14 адреса пропускает коды адреса с выходов счетчика 2 импульсов. Режим работы коммутатора 14 адреса выбирается произвольно оператором, следовательно, и начальное положение ключа 36 может быть любое.

Работа блока 7 задания начального кода заключается в фop a poвaнии исходного кода тестовой программы. Первый исходный код набирается оператором на регистре 29. После нажатия кнопки 31 на пульте блока 13 управления, код, набранный на регистре 29, переписывается в сдвиговьй регистр 28 После перебора всех значений счетчика 2 импульсов сигнал переполнения с выхода дешифратора 3 через формирователи 4 и 6 импульсов и через элемент И 25 поступает на вход С1 сдвигающего регистра 28 и сдвигает первоначально записанный код на один разряд. Новый код является начальным (исходным) кодом следующей тестовой программы. Для примера рассмотРИМ работу блока задания начального кода, если на регистре 29 набран код 00...01. Нажатием кнопки 31 в блоке 13 управления с выхода триггера 32 на вход 15 блока задания начального кода и на второй вход. первого формирователя 4импульсов (фиг. t) поступает сигнал сброса отрицательной полярности, который :задерживается на Элементе 26 задерж ки и подается на вход С2 сдвигающего регистра 28, на входе V2 которого формируется сигнал с элемента И-НЕ 27 положительной полярности, длительностью равной общей длительности сигналов, на первом и втором входах элемента И-НЕ 27. По отрицательному фронту сигнала на входе С2 произойдет запись кода, набранного на тумблерах регистра 29, в сдвигающий регистр 28, т.е. будет записан код 00...01.

Положительньй потенциал на входе V2 разрешает запись информации по D-входам регистра числа и запрещает сдвиг, нулевой потенциал запрещает запись по D-входам и разрешает сдвиг. На выходе Q1 будет 1 на выходах Q2.:.Q20 - О,

С выхода формирователя 6 импульсов на вход 10 поступают импульсы, .в{,1работанные по заднему фронту сигнала сброса поступающего с выхода 15 блока 13 управления или сигнала переполнения счетчика 2 импульсов. Через элемент И 25 подаются синхроимпульсы сдвига на вход С4f регистра 28. Первый импульс не сдвигает информацию.

так как на входе V2 еще держится положительный сигнал. После полного цикла контроля, т.е. достижения максимального значения счетчика 2 импульсов на вход С1 поступит второй импульс, код числа будет сдвинут во второй разряд сдвигающего регистра 2 Полный цикл контроля испытуемого блока будет повторен при новом начальном коде.

Поскольку сдвигающий регистр содержит 20 разрядов, то после прохождения двадцати циклов контроля работа блока задания начального кода повторится, т.е. снова 1 будет записана в первом разряде сдвигающего регистра, но сигнала сброса на входе 15 не будет, если оператор не нажмет кнопку 31 сброса на щшьте блока 13 управления. При необходимости можно отключить сдвиг информации тумблером 24 . В этом случае на входе С1 сдвигающего регистра 28 будет О. При этом на выходах Q1...Q20 сдвигающего регистра 28 после нажатия кнопки 31 в блоке 13 управления будет постоянный код числа, равный . значению кода, набранного оператором на регистре 29. В экспериментальном устройстве был применен двадцатиразрядньй сдвигающий регистр на микросхемах 133ИР1.

В блоке 13 управления в положении Сдвиг с первого подвижного контакта переключателя 30 на управляющий вход коммутатора 9 поступает с выхода 19 блока 13 управления сигнал О, разрешая прохождение кода числа с i-ro выхода регистра 10 числа на вход i+l-ro регистра 10 числа, обеспечивая формирование теста типа Сдвиговый, с второго подвижного контакта переключателя 30 поступает с выхода 18 блока 13 управления раз: решающи сигнал Лог. 1 на второй вход элемента И 12.

В положении Пост свыхода 18 блока 13 .управления на второй вход элемента И 12 подается сигнал О, запрещая прохождение тактовых импульсов с генератор 5 иьтульсов на С-вход регистра 10 числа. При этом код, записанный по S-входам регистра 10 числа, остается неизменным во время всего цикла контроля испытуемого блока.

Кнопка 31 формирует сигнал сброса, триггер 32 ликвчпнр т г чЬЬркт

дребезга контактов при нажатии и отпускании оператором кнопки 31. С выхода триггера 32 из блока 13 управления сигнал сброса поступает на второй вход первого формирователя 4 импульсов и на первьй вход 15 блока 7 задания начального кода.

Предлагаемое устройство обеспечивает формирование тестов типа псевдослучайный код, сдвиговый код, постоянный код, упорядоченный адресный код и вновь введенный дополнительный теЬт - псевдослучайный адресньй код. Указанные тесты позволяют проводить испытания, контроль и диагностику блоков радиоэлектронной аппаратуры, в том числе блоки с многоадресной полупроводниковой памятью.

Формирование теста типа псевдослучайный код.

В блоке 13 управления переключатель 30

оператор Устанавливает в поПерем. В этом случае с блоложение

ка,13 управления поступает сигнал на управлякнций вход коммутатора 9, разрешающий прохождение числа с выхода блока 8 сумматоров на D-вхбды регистра 10 числа, одновременно с блока 13 управления поступают сигналы разрешения на первый вход эле1 . , .мента И 12. Дпя приведения устройства в исходное состояние в блоке 13 управления нажатием кнопки 31 формирУется сигнал сброса отрицательной полярности, который проходит через второй формирователь 4 иипульсов и устанавливает в начальное состояние счетчик 2 импульсов, регистр 10 числа, генератор 5 импульсов, кроме того, сигнал сброса отрицательной полярности с выхода 15 блока 13 управления поступает для установки в исходное состояние блока 7 задания начального кода, в котором оператор предварительно набирает исходный код с помощью регистра 29. Исходный код с выхода 17 блока 7 установки на чального кода через блок 11 элементов И записывается в регистр 10 числа, формируя двоичный код, который является первым испытательным информационным стимулом псевдослучайного теста, затем тактовые импульсы с генератора 5 импульсов поступают на счетный вход счетчика 2 импульсов и через элемент И 12 - на счетный вход регистра 10 числа.

Исходное число с блока 7 задания начального кода поступает на первые А-входы блока 8 сумматоров, на вторые В-входы которого приходит двоичнйй код с выхода регистра числа.

В блоке 8 сумматоров происходит сложение исходного числа с кодом, ранеезаписанным в регистре 10 числа с блока 7 задания начального кода. Например, из блока 7 задания начального кода поступило число 00011001, набранное оператором на тзтблерном регистре 29 в блоке 7 задания начального кода (для примера взято восьмиразрядное слов), которое является первым проверочным стимулом. Вторым проверочным стимулом будет результат от сложения

00011001 +

00011001

00110010

с выхода блока 8 сумматоров двоичный код транслируется через коммутатор на D-входы регистра 10 числа и при поступлении первого тактового импульса с элемента И 12 записывается в него. Так заканчивается формирование второго информационного стимула, который с выходов 20 регист-ра 10 числа посылается в испытуемый блок и на вторые В-входы блока 8 сумматоров, где происходит сложение результирующего кода с исходным кодом,

Т 6

00110010 +

00011001 01001011

При поступлении на счетный вход регистра 10 числа тактового импульса результат суммирования записывает ся через коммутатор 9 в регистр 10 числа, образуя третий испытательный стимул тестов. Аналогично фудет получен четвертый тест

01001011 +

oooligoi oTTooioo

Чтобы проанализировать полученные тесты выпишем их в порядке следования

00011001

00110010

01001011

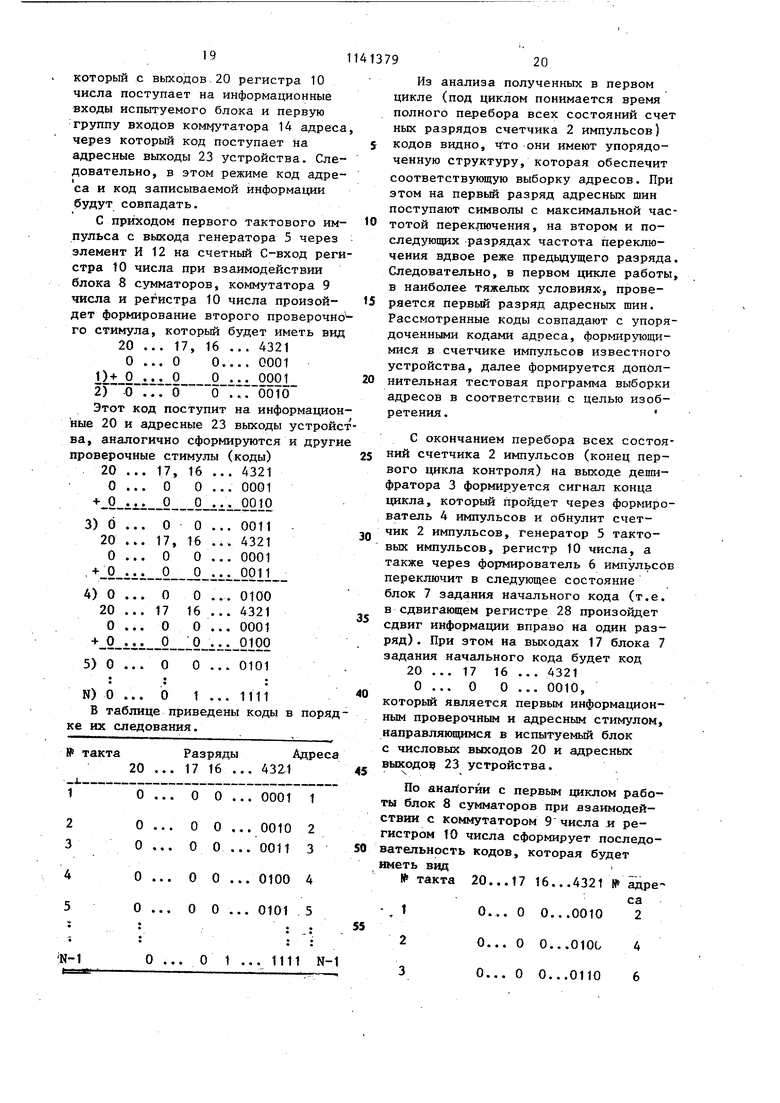

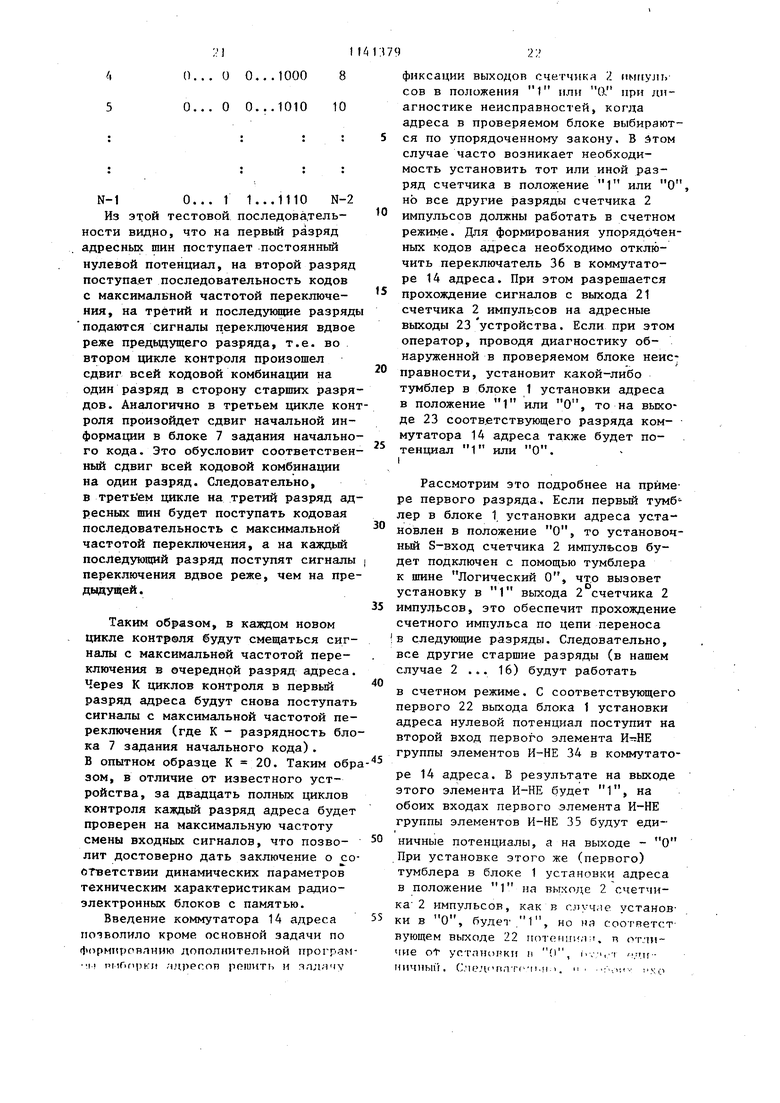

01100100 Представленные тесты не имеют упорядоченной структуры, но строго детерминированы во времени, т.е. могут быть повторены в той же последовательности, что необходимо при конт роле блоков запоминающих устройств, когда в первом цикле проверки осуществляется запись информации, а в следующем будет, считывание. Такие тесты носят название псевдослучайные. Всего в предлагаемом устройстве может быть сформировано за один полный цикл контроля тестов, где М - информационная емкость испытуемого блока, ,2,3...16 разрядность счетчика 2 импульсов . Одновременно с формированием испы тательных тестов на контролируемый блок с выходов 23 коммутатора 14 адреса посылаются коды адреса (адресные стимулы), по которым записываются проверочные тесты в испытуемый блок. При этом, если переключатель 36 в коммутаторе 14 адреса отключен, то нулевой потенциал с переключателя 36 поступает на первые входы вторых элементов И-НЕ 33, на всех выходах которого при этом будут единичные потенциалы, поступающие на вторые входы четвертых элементов И-НЕ 35 Следовательно, через элементы И-НЕ 35 в- этом случае будут проходить на выход 23 устройства упорядоченные коды адреса с выходов 21 счетчика 2 импульсов. Упорядоченные коды адреса вырабатываются следующим образом. iНа блоке 1 установки адреса оператор задает необходимую разрядность счетчика 2 импульсов. С блока 13 управления через первый формирова|тель 4 импульсов поступает сигнал на обнуляющий вход счетчика 2 импульсов устанавливая его в нулевое состояние Код первого адресного стимула на выходах 21 счетчика 2 импульсов имеет вид 00 ... 00. Этот код прохо. дит через коммутатор 14 адреса на выходы 23 и направляется на адрес ные шины испытуемого блока. По этому адресу в проверяемый блок записывается первый испытательный код, поступающий на информационные входы проверяемого блока с выходов 20 регистра 10 числа. С приходом первого тактового импульса на счетный вход счетчик 2 импульсов меняет свое состояние по принципу +1, формируя код адресного стимула, посыпаемого через коммутатор 14 на адресные выходы 23 устройства. По этому адресу в испытуемый блок поступает второй информационный стимул с выходов 20 регистра 10 числа. При достижении максимального состояния счетчика 2 импульсов сигнал с выхода дешифратора 3 запускает первый формирователь 4 импульсов, с выхода которого сигнал устанавливает регистр 10 и счетчик 2 импульсов в нулевое состояние и подготавливает генератор 5 импульсов к работе в следующем такте. По заднему фронту сигнала первого формирователя 4 импульсов запускается формирователь 6 импульсов, который управляет работой блока 7 задания начального кода и блоком элементов И 11. Таким образом, с выходов 23 счетчика 2 импульсов в- испытуемый блок посьтаются тесты в виде двоичного кода 00000000 00000001 000 ..... 0010 0000011 000 0100 Эти тесты имеют упорядоченную структуру и определяют порядок выбора адреса, по которому посьшается проверочный тест с выходов 20 регистра 10 числа. Вновь введенный коммутатор 14 адреса позволяет осуществлять, выбор адресов проверяемого блока памяти не только по упорядоченному закону, но и по псевдослучайному. Для этого необходимо ключ 36 коммутатора 14 адреса установить в положе11ие Псевд. При этом с выхода элемента НЕ 37 на первые входы третьих элементов И-НЕ 34 (в коммутаторе 14 адреса) поступит нулевой потенциал. Следовательно, на первых входах элементов И-НЕ 35 будут единичные потенциалы, разрешающие прохождение псевдослучайных кодов с выходов 20 регистра 0 числа через открытые элементы И-НЕ 33 и 35 на адресные выходы 23 устройства. Это позволяет проверять устойчивость записи, хран ния и считьшания информа ции в контролируемых блоках с памятью при про извольном порядке выбора адресов, что обеспечивает максимальное приближение к реальным условиям работы блоков памяти в цифровых вычислител ных системах. Режим формирования теста типа сдвиговый код и разновидностей шахматного кода. В блоке 13 управления оператор устанавливает переключатель 30 в по ложение Сдвиг. В этом режиме с бл ка 13 управления поступает сигнал на управляющий вход коммутатора 9, При этом входы регистра 10 числа от ключаются от выходов сумматора 8, н через коммутатор 9 соединяются со своими выходами,причем выход 1-го разряда регистра 10 числа соединяется с D-входами i+1-го разряда, выход последнего разряда регистра 10 числа соединяется с D-входом первого разряда, образуя кольцевой сдвиговы регистр. Исходный код числа с блока 7 задания начального кода по импульсу второго формирователя 6 через блок 1 элементов И записывается по S-входа в регистр 10 числа. Записанный код является первым информационным стимулом, который посылается с выходов 20 регистра 10 числа в испыту мый блок, в ячейку, соответствующую поступившему адресному стимулу с вы хода 23 счетчика 2 импульсов. С приходом первого тактового импульса на счетный вход регистра 10 числа код, записанный в него, сдвигается на один шаг, образуя следующий информационный стимул. При установке в блоке 7 чередующегося кода 101010 ... 10 на выходе регистра 10 числа будут формировать ся коды типа шахматный тест, кото рый может иметь разновидность вида 1100 1100 ... 1100 и другие. Режим формирования теста типа постоянный код. Переключатель 30 в блоке 13 упра ления должен быть установлен в поло жение Пост. В этом режиме с блока 13 управления поступает сигнал на элемент И 12, запрещающий прохождение тактовых импульсов на счетный вход регистра 10 числа. Поэтому в регистре 10 числа будет постоянная информация, записанная по S-входам с блока 7 установки начального кода через блок 1t элементов И. Для изменения кода в регистре 10 числа необходимо с помощью р егистра 29 в блоке 7 установки начального кода установить новый код, далее при нажатии кнопки 3 в блоке 13 управления формируется сигнал сброса, который поступает через первый формирователь 4 импульсов на обнуляющий вход регистра 10 числа и счетчика 2, а также подготавливает генератор 5 к работе. По входу 15 сигнал сброса записывает исходный код в блоке 7 задания начального кода, с выхода которого новый код поступает на входы блока элементов И 11 и с приходом сигнала с выхода формирователя 6 импульсов на управляющий вход блока элементов И 11, код переписывается по S-входам в регистре числа 10 и направляется в испытуемый блок. Далее, в процессе контролирования испытуемого блока, код с выхода регистра 10 числа не меняется. Режим проверки на максимальное быстродействие (максимальную частоту переключения) каждого разряда адресных шин испытуемого блока проводится при использовании псевдослучайного теста. Для этого переключатель 36 в коммутаторе 14 адреса необходимо установить в положение Псевд, в блоке 13 управления переключатель 30 - в положение Перем ; включить ключ 24 и установить код 00 ... 01 на установочном регист-ре 29 в блоке 7 задания начального кода. При нажатии кнопки Пуск в блоке 13 упрайления сигнал сброса поступает с выхода 15 блока 13 управления через первый формирователь 4 импульсов и обнуляет счетчик 2 импульсов, генератор 5 тактовых импульсов, регистр 10 числа, блок 7 задания начального кода, При этом двоичный код переписывается в сдвигающий регистр 28 блока 7 задания начального кода и через блок элементов И 11 переписывается в регистр 10 числа. Код 00 ... 01 является первым проверочным стимулом, который с выходов 20 регистра 10 числа поступает на информационные входы испытуемого блока и первую группу входов коммутатора 14 адрес через который код поступает на адресные выходы 23 устройства. Сле довательно, в этом режиме код адр са и код записываемой информации будут совпадать. С приходом первого тактового и пульса с вькода генератора 5 чере элемент И 12 на счетный С-вход ре стра 10 числа при взаимодействии блока 8 сумматоров, коммутатора 9 числа и регистра 10 числа произой дет формирование второго провероч го стимула, который будет иметь в 20 ... 17, 16 ... 4321 О ... О 0.... 0001 1)+ О .. О О ...0001 . ооТо Этот код поступит на информаци ные 20 и адресные 23 выходы устро ва, аналогично сформируются и дру проверочные стимулы (коды) 20 ... 17, 16 ... 4321 О ... О О ... 0001 f О .,. О О ... 0010 5) О ... О О ... 0101 «« N) О ... О 1 ... 1111 В таблице приведены коды в пор ке их следования. № такта Разряды Адре 20 ... 17 16 ... 43Z1 I.и, „-Г -Lnfl-ll Т о ... о о ... 0001 1 О...ОО... 00102 О...ОО... ООН3 О...ОО... 01004 О...ОО... 01015 1111 N Из анализа полученных в первом цикле (под циклом понимается время полного перебора всех состояний счет ных разрядов счетчика 2 импульсов) кодов видно, что они имеют упорядоченную структуру, которая обеспечит соответствующую выборку адресов. При этом на первый разряд адресных шин поступают символы с максимальной частотой переключения, на втором и последующих разрядах частота переключения вдвое реже предьщущего разряда. Следовательно, в первом цикле работы, в наиболее тяжелых условиях-, проверяется первый разряд адресных шин. Рассмотренные коды совпадают с упорядоченными кодами адреса, формирующимися в счетчике импульсов известного устройства, далее формируется дополнительная тестовая программа выборки адресов в соответствии с целью изобретения. С окончанием перебора всех состояний счетчика 2 импульсов (конец первого цикла контроля) на выходе дешифратора 3 формируется сигнал конца цикла, который пройдет через формирователь 4 импульсов и обнулит счетчик 2 импульсов, генератор 5 тактовых импульсов, регистр 10 числа, а также через формирователь 6 импульсов переключит в следующее состояние блок 7 задания начального кода (т.е. в сдвигающем регистре 28 произойдет сдвиг информации вправо на один разряд) . При этом на выходах 17 блока 7 задания начального кода будет код 20 ... 17 16 ... 4321 О ... О О ... 0010, который является первым информационным проверочным и адресным стимулом, направляющимся в испытуемый блок с числовых выходов 20 и адресных выходов 23 устройства. , По анапогйи с первым циклом работы блок 8 сумматоров при взаимодействии с коммутатором 9 числа и регистром 10 числа сформирует последовательность кодов, которая будет иметь вид № такта 20...17 16...4321 адреса . 1 0... О 0...0010 2 0... О 0...010С 4 0... О 0...0110 6 п.. , о 0.,.1000 8 0... о 0...1010 10 N-1 0... 1 1..,1110 N-2 Из этой тестовой последовательности видно, что на первый разряд адресных шин поступает постоянный нулевой потенциал, на второй разряд поступает последовательность кодов с максималнной частотой переключения, на третий и последующие разряд подаются сигналы переключения вдвое реже предыдущего разряда, т.е. во втором цикле контроля произошел сдвиг всей кодовой комбинации на один разряд в сторону старших разря дов. Аналогично в третьем цикле кон роля произойдет сдвиг начальной информации в блоке 7 задания начально го кода. Это обусловит соответствен ный сдвиг всей кодовой комбинации на один разряд. Следовательно, в третьем цикле на третий разряд ад ресных шин будет поступать кодовая последовательность с максимальной частотой переключения, а на каждый последующий разряд поступят сигналы переключения вдвое реже, чем на пре дыдущей . Таким образом, в каждом новом цикле контроля будут смещаться сигнапы с максимальней частотой переключения в очередной разряд адреса Через К циклов контроля в первый разряд адреса будут снова поступать сигналы с максимальной частотой переключения (где К - разрядность бло ка 7 задания начального кода). В опытном образце К 20. Таким обр зом, в отличие от известного устройства, за двадцать полных циклов контроля каждый разряд адреса будет проверен на максимальную частоту смены входных сигналов, что позволит достоверно дать заключение о со ответствии динамических параметров техническим характеристикам радиоэлектронных блоков с памятью. Введение коммутатора 14 адреса поэБолило кроме основной задачи по Формировлнию дополнительной прогрям I пмПгчжи .ч.иресоя решить и япд.ччу фиксации выходов счетчикя 7. импуль сов в положения 1 или ft при диагностике неисправностей, когда адреса в проверяемом блоке выбираются по упорядоченному закону, В 5том случае часто возникает необходимость установить тот или иной разряд счетчика в положение 1 или О, но все другие разряды счетчика 2 импульсов должны работать в счетном режиме. Для формирования упорядоченных кодов адреса необходимо отключить переключатель 36 в коммутаторе 14 адреса. При этом разрешается прохождение сигналов с выхода 21 счетчика 2 импульсов на адресные выходы 23 устройства. Если при этом оператор, проводя диагностику обнаруженной в проверяемом блоке неисправности, установит какой-либо тумблер в блоке 1 установки адреса в положение 1 или О, то на выходе 23 соотвзетствующего разряда коммутатора 14 адреса также будет потенциал 1 или О. I Рассмотрим это подробнее на примере первого разряда. Если первый тумб лер в блоке 1, установки адреса установлен в положение О, то установочный S-вход счетчика 2 импульсов будет подключен с помощью тумблера к шине Логический О, что вызовет установку в 1 вьпсода 2 счетчика 2 импульсов, это обеспечит прохождение счетного импульса по цепи переноса в следующие разряды. Следовательно, все другие старшие разряды (в нашем случае 2 ... 16) будут работать в счетном режиме. С соответствующего первого 22 выхода блока 1 установки адреса нулевой потенциал поступит на второй вход первого элемента группы элементов И-НЕ 34 в коммутаторе 14 адреса. В результате на выходе этого элемента И-НЕ будет 1, на обоих входах первого элемента И-НЕ группы элементов И-НЕ 35 будут единичные потенциалы, а на выходе - О При установке этого же (первого) тумблера в блоке 1 установки адреса в положение 1 на выходе 2 счетчика 2 импульсов, как в случяе установки в О, будет., но ма соответствующем выходе 22 погеш.и .ч;. п отличие ot устатюпкп и (1, ,-i /urНИЧНыГг, Сл(,(-1Ьн.1 . 1 ,

дах первого элемента И-НЕ группы элементов И-НЕ 34 будут единичные потенциалы, а на выходе - нулевой. В этом случае на выходе 23 первого разряда будет 1, а другие разряда будут переключаться соответствен ю переключению разрядов счетчика 2 импульсов.

Таким образом, введенный коммутатор 14 адреса выполняет две функции - основную, для обеспечения дополнительной программы выборки адресов и вспомогательную - для фиксации разрядов адресных выходов в положении О или 1 при диагностике неисправностей проверяемого блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1982 |

|

SU1096612A2 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

УСТРОЙСТВО ДЛЯ ЗАДАНИЯ ТЕСТОВ по авт. ев, № 1038926, отличающееся тем, что, с целью повышения достоверности контроля и расвтрения области применения устройства, в него введены переключатель режимов и коммутатор адреса, содержащий группы вторых, третьих и четвертых элементов И-НЕ, элемент НЕ, подключенный входом к первым входам вторых элементов И-НЕ, а выходом - к первым входам третьих элементов И-НЕ, соединенных вторыми входами с соответствующими вторыми выходами блока установки адреса, третьими.входами - с соответствутощими разрядными выходами счетчика импульсов, а выходами - с первыми вхо-. дами четвертых элементов И-НЕ, подключенных вторыми входами к выходам вторых элементов И-НЕ, связанных вторыми входами с соответствующими выходами регистра числа, апервыми входами через переключатель режимов - с шинами Логический О и Логическая 1, причем выходы четСЛ вертых элементов И-НЕ являются адресС ными выходами устройства.

У

гЫ 26

1$

25

тл&е.1

Ч .

S

2

Q1 в2

IS

17j

д20

т

JJ

ilf

Л

01/8 S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для задания тестов | 1981 |

|

SU1038926A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-02-23—Публикация

1983-10-28—Подача