(54) ЗАПОМИНАЮЕЩЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Ассоциативное запоминающее устройство | 1981 |

|

SU978196A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Запоминающее устройство с одновременным считыванием нескольких слов | 1986 |

|

SU1310899A1 |

Изобретение относится к вычиспитёпь ной технике, к устройствам, где необходимо накаппи ние некоторого массива двоичной информации с последующим непрерывным считыванием в последовательном коде, например в растровых графичесних индикаторах с дискретным методом формирования изображения. При опросе ЗУ синхронно с движением луча ЭЛТ на выходе ЗУ формируется последовательный код, соответствующий видеосигналу графического изображения.

Известнь ЗУ, позволяющие осуществлять непрерывное считывание накопленного массива двоичной информации в после- ,5 довательном коде и состоящие из матрицы памяти и двух сдвиговых регистров. Каждая ячейка матрицы памяти имеет информационный выход, адресный и считыва1ощий входы, причем инфору ационные выхо- 20 ды каждого столбца матрицы объединены и через селектор соединены с соответст- вуюнгами входами сдвиговых регистров. Выходы регистров объединены по ИЛИ и

образуют выход ЗУ. Адресные входы так же объединевы в грухшы и образуют адресные шишл, а считывающие входы o&i единены и образуют шину считывания мат рицы.

Работают сдвиговые регистры в противофазе, т.е. пока с одного информация считывается в последовательном коде, во второй через селектор в параллельном коде перезаписывается информация одной строки матрицы, и наоборот, чем и достигается непрерывное считывание инфо умадии. Частота сдвига информации в регистрах определяется частотой фору ирования последовательного кода, тогда как частота обращения к матрице ниже чаототы формирования последнего в п раз, где п - разрядность регистра tilНедостаток данного ЗУ - наличие сдвиговых регистров.

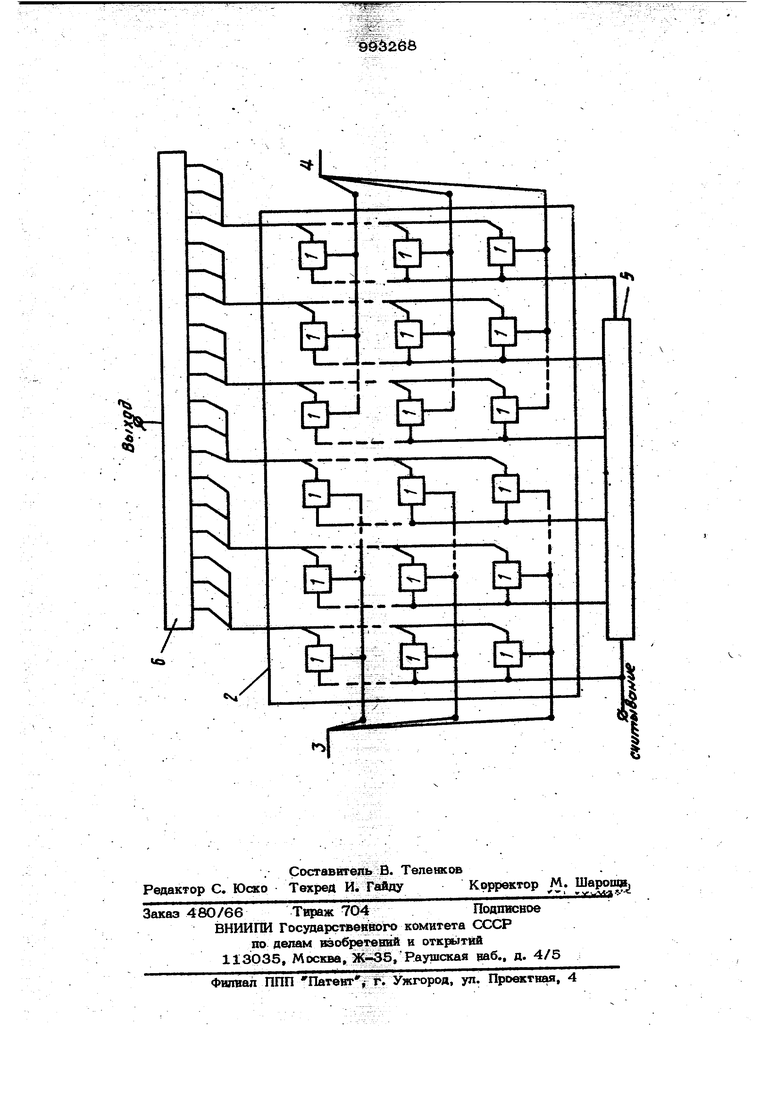

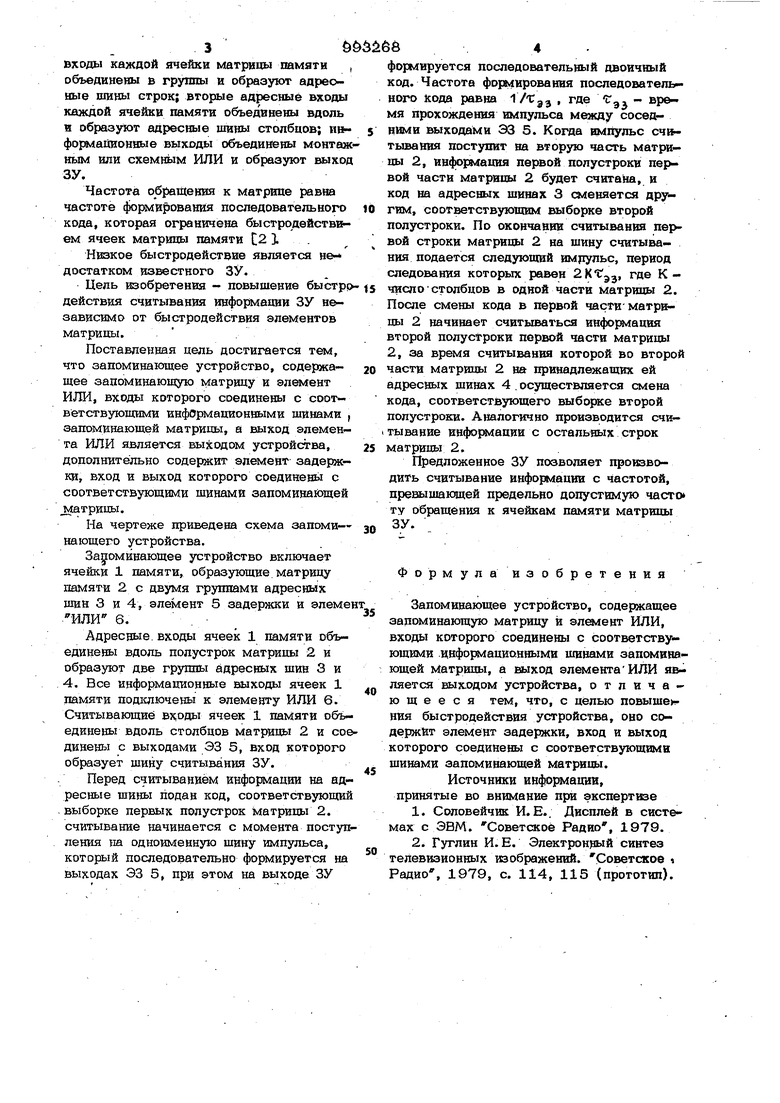

Наиболее близким к предлагаемому по технической сущности является ЗУ, содержащее матрицу памяти, элементы И и элемент ИЛИ, причем первые адресные входы каждой ячейки матрицы памяти объединены в гругашт и образуют адресные шины строк; вторые адресные входы каждой ячейки памяти объединены вдоль и образуют адресные шины столбцов; ив формайионные выходы объединены монтаж ным или схемным ИЛИ и образуют выход ЗУ. Частота обращения к матрице равна частоте формирования последовательного кода, которая ограничена быстродействием ячеек матрицы памяти С2 3. . Низкое быстродействие является недостатком известного ЗУ. Цель изобретения - повышение быстрр действия считывания информации ЗУ независимо от быстродействия элементов матрицы.. Поставленная цель достигается тем, что запоминающее устройство, содержащее запоминаюшую матрицу и элемент ИЛИ, входы которого соединены с соответствующими информационными шинами запоминающей матрицы, а Шз1ход элемента ИЛИ является выходом устройства, дополнительно содержит элемент задержки, вход и выход которого соединены с соответствующими шинами запоминающей матрицы. На чертеже приведена схема запоми- нающего устройства. Запоминающее устройство включает ячейки 1 памяти, образующие. матрицу памяти 2 с двумя группами адресных шин 3 и 4, элемент 5 задержки и элеме ИЛИ 6. Адрес вые. входы ячеек 1 памяти объединены вдоль полустрок матрицы 2 и образуют две группы адресных шин 3 и 4. Все информационные выходы ячеек 1 памяти подютючены к элементу ИЛИ 6. Считывающие входы ячеек 1 памяти объединены вдоль столбцов матрицы 2 и со динены с выходами ЭЗ 5, вход которого образует шину считывания ЗУ. Перед считыванием информации на ад ресные шины подан код, соответствующи .выборке первых полустрок матрицы 2. считывание начинается с момента поступ ления на одноименную шину импульса, который последовательно формируется на выходах ЭЗ 5, при этом на выходе ЗУ формируется последовательный двоичный код. Частота формирования последователь ного кода равна l/Cgj , где врвмя прохождения импульса соседними выходами ЭЗ 5. Когда №4пульс считывания постулит на вторую часть матрицы 2, информация первой полустроки части матрицы 2 будет считана, и код на адресных шинах 3 сменяется другим, соответствуютао выборке второй полустроки. По окончании считывания перовой строки матрицы 2 на шину считывания подается следующий имрульс, период следования которых равен 2Kt, где К числостолбцов в одной части Матрицы 2. После смены кода в первой части матрицы 2 начинает считываться информация второй полустроки первой части матрицы 2, за время считывания которой во второй части матрицы 2 не принадлежащих ей адресных шинах 4 , осуществляется смена кода, соответствующего выборке второй полустроки. Аналогично производится считывание информации с остальных строк матрицы 2. Предложенное ЗУ позволяет производить считывание информации с частотой, превышающей предельно допустимую часто ту обращения к ячейкам памяти матрицы ЗУ. Формула изобретения Запоминающее устройство, содержащее запоминающую матрицу и ИЛИ, входы которого соединены с соответствующими информационными шинами запоминающей Матрицы, а выход элементаИЛИ является выходом устройства, отличающееся тем, что, с цепью повышенния быстродействия устройства, оно содержит элемент задержки, вход и выход которого соединены с соответствующими шинами запоминающей матрицы. Источники информации, принятые во внимание при экспертнезе 1.Соловейчик И. Е.; Дисплей в системах с ЭВМ. Советское Радио, 1979. 2.Гуглин И. Е. Электронный синтез телевизионных изображений. Советское Радио, 1979, с. 114, 115 (прототип).

ti.

Й

1

«

чдЖйз

H-

-

-t

:.

/

/

Авторы

Даты

1983-01-30—Публикация

1981-01-29—Подача