Изобретение относится к электронной и вычислительной технике и предназначено для использования в интегральных полупостоянных запоминающих устройствах (ЗУ) в качестве изолированного накопителя запоминающих элементов,

; Известны накопители, матрицы которых содержат запоминающие МНОПтранзисторы с электрически изменяемым пороговым напряжением, позволяющие записывать, считывать информацию и сохранять ее при отключенном питании.

Известен также накопитель, содержащий пстрок И m столбцов, образованных запоминающими ячейками, каждая из которых содержит двухзатворный МНОП-транзистор, адресный затвор которого подключен к шине выборки столбца, объединяющей адресные затворы всех ячеек столбца. Программирующий затвор расположен над запоминающей областью канала МНОП-транзИстора и подключен к шине управления, объединяющей программирующие затворы всех ячеек строки. Истоковые электроды каждых двух смежных транзисторов строки соединены между собой и подключены к сооветствующей шине считывания, которая объединяет все истоковые электроды транзисторов в двух смежных .столбцах. С токовые., электроды этих транзисторов соединены последовательно в строке со стоковыми элект.родами транзисторов других смежных столбцов и подключены к соответствующей разрядной шине, объединяющей все стоковые электроды транзисторов в двух смежных столбцах tl..

Недостатком данного накопителя является увеличение сопротивления в истоке запоминающего МНОП-транзистора, выполненного в виде диффузионной шИнЬг считывания, в результате чего снижается быстродействие МНОП ППЗУ на осМойе данного накопителя.

Наиболее близок к предлагаемому по технической сущности накопитель, который содержит п строк и m столбцов , образованных запоминающими ячейками, каждая из которых содержит адресный и запоминающий МНОПтранзисторы, причем затвор адресного транзистора подключен к соответствующей адресной шине выборки, исток последовательно соединен со стоком запоминающего МНОП-транзистора, затвор которого подключен к шине управления. В каждой строке адресная шина- выборки объединяет затворы адресных транзисторов, шина управления - затворы запоминающих транзисторов. В каждом столбце отдельная разрядная шина объединяе стоковые электроды адресных транзисторов, а отдельная коммутирующая шина - истоковые электроды запоминающих транзисторов Г2.

Недостатком известного накопителя является увеличение числа.коммутирующих шин и соответственно количества контактов в каждой запоминающей ячейке, вследствие чего уменьшается надежность и плотность компановки схемы. изобретения - повышение надежности накопителя.

Поставленная цель достигается тем, что в матричном накопителе, содержащем матрицу элементов памяти, каждый из которых содержит адресный и запоминающий МНОП-транзисторы, причем затворы адресных транзисторов соединены с соответствующими адресными шинами, истоки соединены со стоками запоминающих транзисторов, истоки запоминающих транзисторов в каждой строке матрицы попарно объединены и соединены с соответствующей коммутирующей шиной,.затворызапоминающих транзисторов Каждого столбца Матрицы соединены d.соответствующей управляющей шиной, стоки адресных транзисторов смежных столбцов матрицы объединены и соединены с соответствующей резрядной шиной.

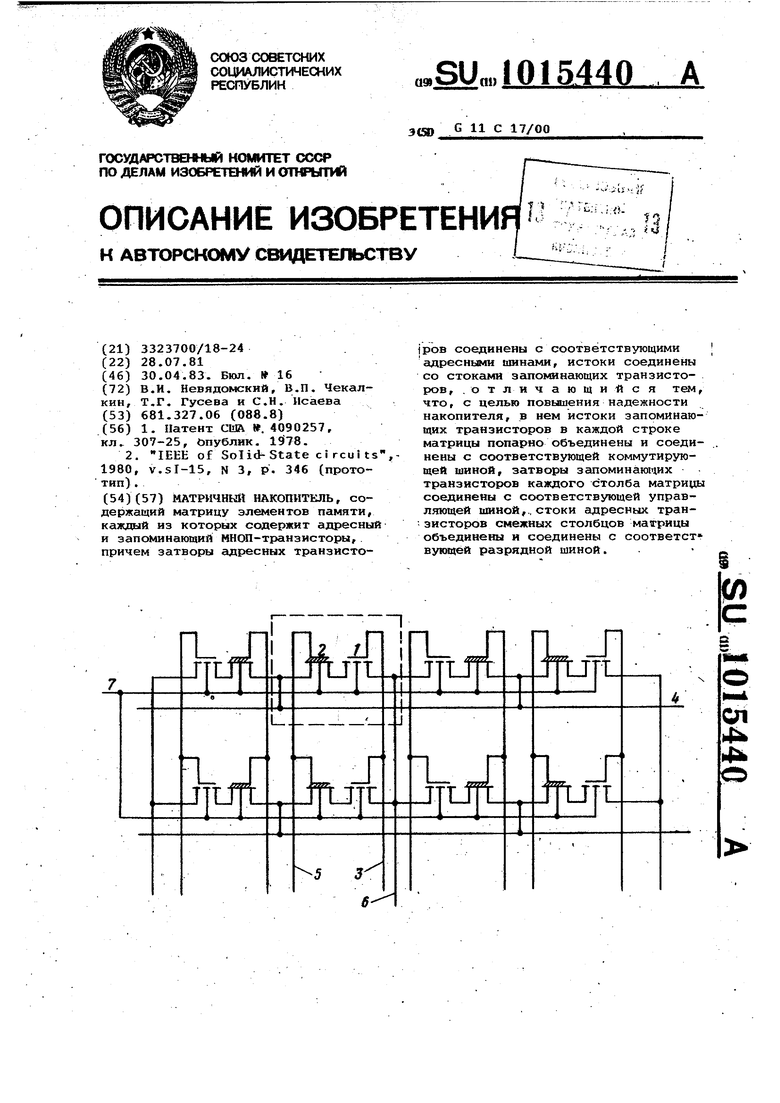

На чертеже представлен матричный накопитель.

Матричный накопитель содержит Матрицу элементов памяти, каждый из Которых содержит адресный 1 и запоминающий 2 МНОП-транзисторы, причем затворы адресных Транзисторов соединены с соответствующими адресными шинами 3, истоки соединены со стоками запоминающих транзисторов 2,.истоки запоминающих транзисторов 2 в каждой строке матрицы попарно объединены и соединены с соответствующе.й коммутирующей шиной 4 затборы запоминающих транзисторов каждого стопбца матрицы соединены с соответствующей управляющей шиной 5 стоки адресных транзисторов смежных столбцов матрицы объединены и соединены с соответствующей разрядной шиной б. На чертеже показан также вывод 7 подложки.

Данный накопитель работает в четырех режимах: запись информации, общее стирание, избирательное стирание и считывание информации.

В режиме записи выборка столбца осуществляется шинами 5 управления, все адресные 3 и разрядные 6 шины заземлены. На выбранную шину управления подается напряжение программирования Vpp, равное 25 В, а-выбранная коммутирующая шина заземляется.

В затворном диэлектрике выбранного запоминающего МНОП-транзистоpa 2 под действием напряжения программирования VPP 25 В накапливается отрицательный заряду.сдвигающий его пороговое напряжение в состояние 1, т.е. Л 6 В. В невыбранных запоминающих ячейкак столбцов, смежных с выбранным, запись 1 исключается заземлением соответствующих шин управления. В невыбраннах ячейках возбужденного столбца запись 1 запрещена напряжением запрета записи Vj 15 поступающим в каналы МНОП-транзисторов по невыбранным коммутирующим шинам. Таким образом, напряжение запрета экранирует в затворном диэлектрике МНОП-транзистора 2 nporpa мирующее напряжение 25 В, поданное на шину 5 управления и обеспечивает сохранение ранее записанной информации. В режиме общего стирания шины уп равления заземляются, коммутируюи№1е и разрядные шины подключаются к высокоомному сопротивлению, а на изолированную подложку накопителя подается напряжение стирания 25 В, что обеспечивает уменьшение отрицательного заряда в затворном диэлектрике всех запоминающих транзисторов до состояния . О , т.е. Updp 2 В. В режиме избирательного стирания все адресные шины и выбранная шина управления заземляются, коммутирующие и разрядные шины подключа ются к высокоомном| сопротивлению. Одновременно на изолированную подложку накопителя подается напряжение стирания, 25 В. По невыбранным шинам управления на затворы соответствующих запоминающих МНОП-транзисторов поступает напряжение программирования Vpp 25,0 В. Подача напряжения Ул на затворы нe ,выбранных МНОП-транзисторов предотвра щает информации в невыбранных.столбцах. Таким образом, режим обеспечивает стирание информации только в ячейках выбранного столбца, затворы запоминающих транзисторов которого заземлены. В режиме считывания на выбранную шину управления подается напряжение считывания .Vj которое выбирается из условия Vo D, пор RE ПОР На выбранную адресную шину посту- пает отпирающее напряжение l а все разрядные и невыбранные .адресные шины заземляются. Выбранная коммутирующая шина заряжена до напряжения 1. Если выбранный запоминающий МНОП-транзистор находится в состоянии низкого порогового напряжений, то при поступлении на его затвор напряжения считывания Vjj , происходит разр;1Д емкости выбранной коммутирукмдей шины через открытые адресный и запоминающий .МНОП-транзиСторы до напряжения О. Если выбранный запоминающий МНОП-транзистор находится S состоянии высокого порогового напряжения, то напряжение считывания недостаточно для его отпирания и происходит заряд емкости выбранной KC Iмутирующей шины до напряжения 1. Изменение потенциала на емкости выбранной коммутирующей шины передается на вход усиЛителя считывания как выходная информация иэ ячейки; Применение ППЗУ с таким накопителем в блоках программируемой памяти увеличивает надежность и улуч1уает быстродействие всего устройства в .

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Матричный накопитель | 1980 |

|

SU974412A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Способ записи и считывания информации в МНОП-элементе памяти,МНОП-элемент памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405088A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

МАТРИЧНЫЙ НАКОПИТЕЛЬ, содержащий матрицу элементов памяти, каждый из которых содержит адресный и запоминающий МНОП-транзисторы,. причем затворы адресных транзисто1ров соединены с соответствующими адресными шинами, истоки соединены со стоками зсшоминающих транзисторов, .отличающийся тем, что, с целью поньоления надежности накопителя, в нем истоки запоминающих транзисторов в каждой строке матрицы попарно объединены и соединены с соответствующей коммутирующей шиной, затворы зг поминающих транзисторов каждого столба матрицы соединены с соответствующей управляющей шиной,., стоки адресных транзисторов смежных столбцов матрицы объединены и соединены с соответст вующей разрядной шиной. 01 4: 4 О

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США | |||

| 4090257, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Терморегулятор для термостата с электрическим нагревателем | 1929 |

|

SU15178A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IEEE of Solid-State circuits, 1980, v.sI-15, N 3, p, 346 (прототип) . | |||

Авторы

Даты

1983-04-30—Публикация

1981-07-28—Подача