(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1978 |

|

SU729849A2 |

| Устройство для исправления ошибок | 1978 |

|

SU681556A2 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК | 1972 |

|

SU432677A1 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1984 |

|

SU1202057A1 |

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

Изобретение относится к технике связи и вычислительной технике и . может использоваться в системах передачи ихранения информации, подверженных воздействию помех. i - .

По основному ав-1. св. № 729849 известно устройство для исправления ошибок, содержащее счетчик повторений, выход которого соединен с входом коммутатора, а вход.с входами первого и второго сумматоров и управляющего ключа, другие входы которого соединены с. выходами первого и второго KiySKK opoSf регистра сдвига и коммутатора, а выход - с входом регистра сдвига, сумматора декодера, входы которого соединены с выходами регистра сдвига, а выходы - с входами мажоритарного элемента, выход которого соединен с входом ключа, другой вход которого соединен с выходом коммутатора, дополнительного регистра сдвига, включенного входе второго ключа и выходом мажоритарного элемента, -очетчик ошибок иэлемент сравнения, первый вход KQторого подключен к входной 11шне,второй вход. - к выходу мажоритарного элемента, а выход через счетчик ошибок - к одному из входов i коммуматорд

Декодирование кодовой комбинации в устройстве происходит следукидим образом: если кратность ошибок в принимаемых посылках более . максимальная кратность ошибок, исп- ; равляемой корректирующим кодом), то для .декодирования кодовой комбинации необходимо три посылки, ,если-{Х ма1со/ то для декодирования и исправления

10 ошибок необходимо не менее двух посылок ин формации 1 Д.

Недостатком известного устройства является его низкое быстродействие.

15

Цель изобретения - повьЕиение быстродействия устройства.

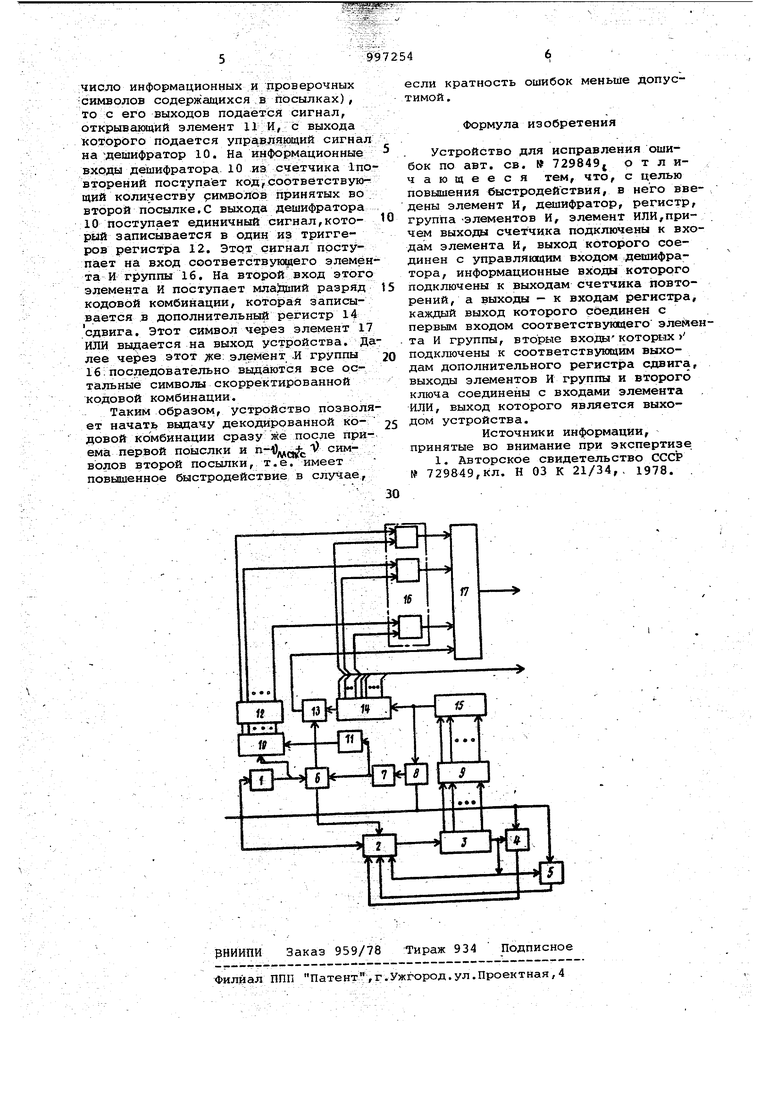

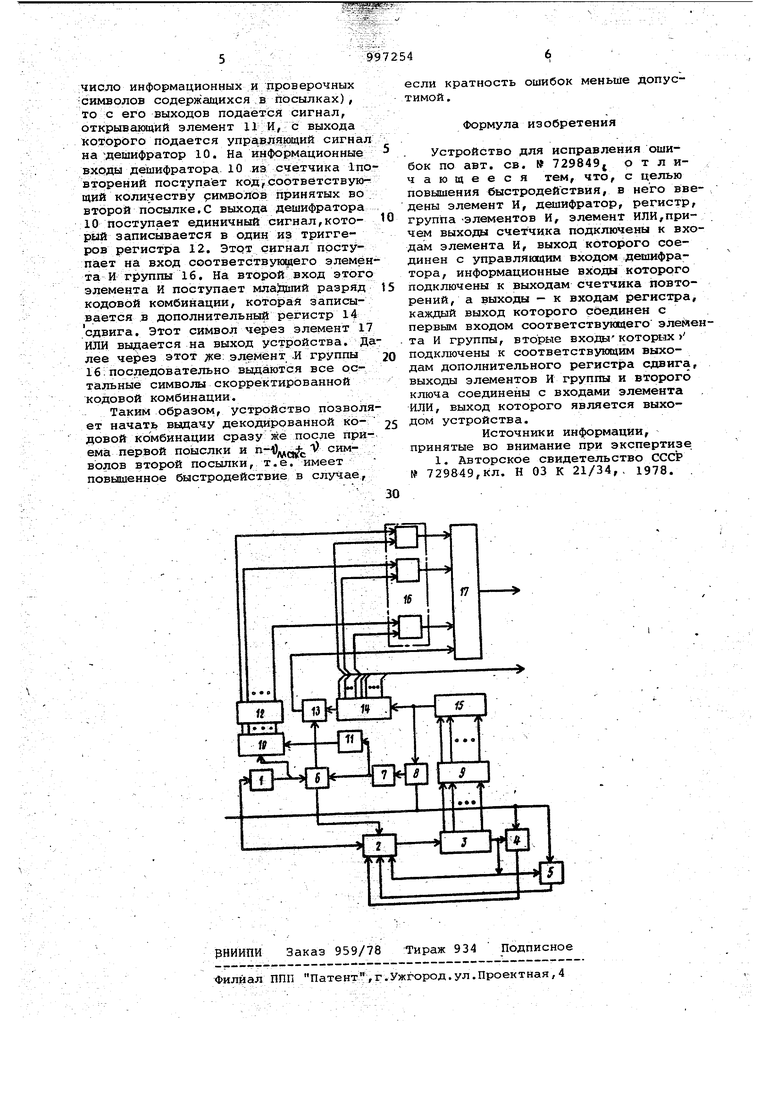

Цель достигается тем, что в устройство для исправления ошибок, со держащее счетчик повторений, коммутатор, ключ, регистр сдвига, счетчик и элемент сравнения, введены элементы И, дешйфр.атЬр, регистр, пруппа элементов И и элемент ИЛИ If причем выходы счетчика подключены ко входам 25 элемента И, выход которого соединён с управляющим входом дешифратора, информационные входы которого подключены к выходам счетчика.повторений, а выходы;-ко входам регистра, каждый

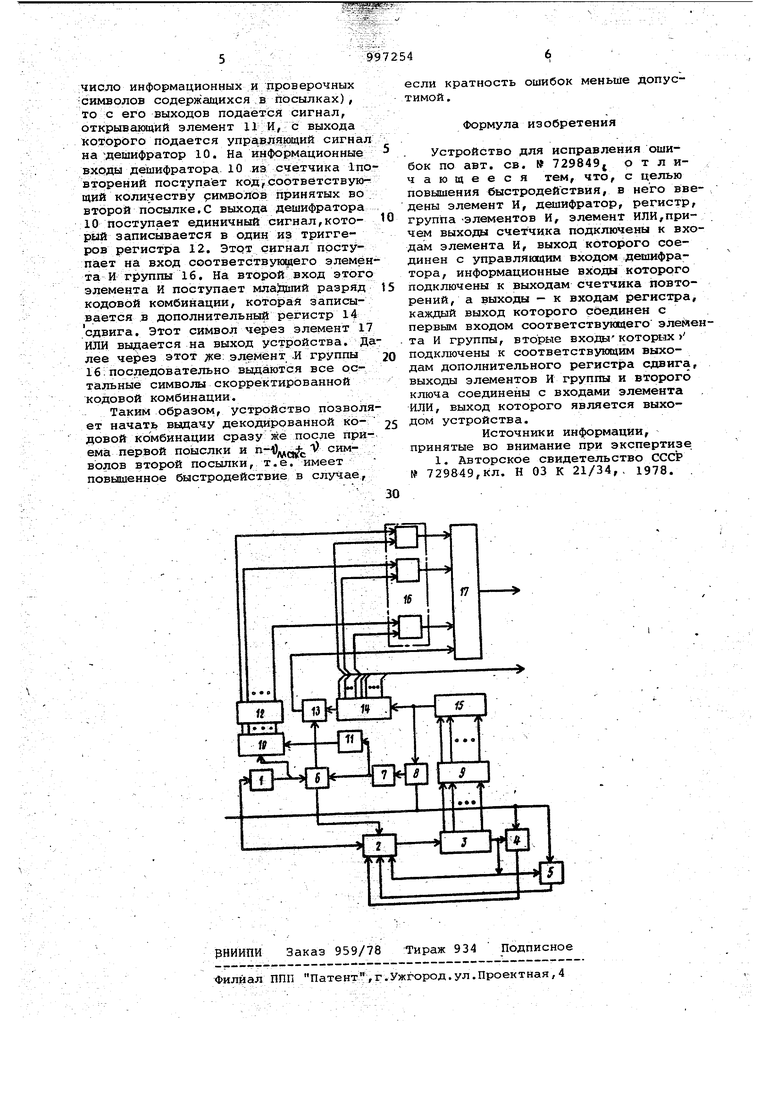

30 выход которого соединен с первым входом, соответствующего элемента И группы, вторые входы крторых подключены к соответствующим выходам допол нительного регистра сдвига, выходы элементов И группы и второго ключа соединены со -входами элемента ИЛИ, выход кЬторого является выходом устройства для исправления ошибок. На чертеже представлена структурная схема устройства для исправлений ошибок. Устройство содержит счетчик 1 повторений, вход которого соединен со входом-ус тройства, первый ключ .2, регистр 3 сдвига, сумматоры 4 и 5, коммутатор 6, счетчик 7, элемент 8 сравнения, сумматоры 9 декодера, дешифратор 10, элемент 11 И, регистр 12, второй ключ 13, дополнительный регистр 14 сдвига, мажоритарный элемент 15, группа элементов 16 И, элемент 17 ИЛИ. Выходы счетчика 1 повторений соед нень. с входами коммутатора бис информационными входами дешифратора 10 Входы первого ключа 2 соединены с входами устройства, выходами суммато ров 4 и 5 и выходами коммутатора 6. Вйкод первого ключа соединен с входо регистра 3 сдвига, выходы которого подключены ко входам сумматора 9 декодера и сумматоров 4 и 5, входы которых соединены с входом устройства Другой, вход коммутатора 6 соединен с выходом счетчика 7, который подключе ко входу элемента 11 И, Другой выход коммутатора 6 соединен -со входом вто рого ключа 13. Вход счетчика 7 соеди нен с элементом 8 сравнения,один вход которого соединен с входом устройств а другой, с выходом мажоритарногоэле мента 15, входы которого, подключены к выходам сумматора-декодера 9. Выход мажоритарного элемента 15 соединен со -входом дополнительного регистра 14сдвига. Управляющий вход дешифратора 10 соединен с выходом элемента 11 И, вы ходы дешифратора соединены с входами регистра 12, выходы которого соедин вы с первыми входами соответствующи элементов И группы 16. Выход второг ключа 13 соединен с входом элемента 17 ИЛИ, а вход второго ключа 13 под ключен к выходу дополнительного регистра 14 сдвига, младшие1,,разрядных выходов которого соединены со вторыми входами элементов И группы 16,Выходы элементов И группы 16 под /ключены ко входам элемента 17 ИЛИ, выходы которого являются выходами устройства для исправления ошибок. Устройство работает следующим об разом. При приеме (Первой посылки сигнал с коммутатора 6 ставит первый ключ 2 в положение, при котором на вход регистра 3 сдвига проходят принимаемые символы.По окончании приема первой посылки (кодовой комбинации)сигнал со счетчика I повторений поступает на коммутатор. 6,выходной сигнал с которого ставит первый ключ 2 в положение , при котором на вход регистра 3 сдвига проходят сигналы с первого сумматораг4, работающего по правилу 1-Ц 1; 1 + 0,,. Счетчик 7 устанавливается в нулевое состояние. При при.еме. второй посылки одновременно производится исправление ошибок в. первой посылке с помощью сумматоров 9 декодера и мажоритарного элеента 15. . Каждый символ второй посылки сравнивается в элементе 8 сравнения с соответствующим символом скорректированной первой посылки, которая записывается в дополнительный регистр 14 сдвига. При совпадении символов первый и второй посылок эле- мент 8 сравнения выдает единичный сигнал, по которому счетчик 7 увеличивает свое состояние на еди,ницу при этом целесообразно рассмотреть два характерных случая: в первой или второй посылках кратность ошибок . первой или второй посылках кратность ошибокOi P/wG ccВ первом cjry4ae вторая и скорректированная первая посылки- отличаются больше, чем на0ддр,символов. О наличии ошибок, кратность больше1 д| свидетельствует состояние счетчика 7. По окончании приема второй посылки сигналы со счетчика 1 повторений и счетчика 7 поступают на коммутатор 6, сигнал с которого ставит первый ключ 2 в положение, при котором на вход регистра 3 сдвига проходят сигналы с выхода второго сумматора, 5, ра ботающего по правилу: 1 + 1 17 0+0-0; 0+1 0;2+1 1; , где первыми записаны символы/ поступающие из регистра 3 сдвига. Одновременно с приемом третьей посылки производится исправление ошибок с помощью сумматоров 9 декодера и мажоритарного, элемента 15 и запись исправленной кодовой комбинации в дополнительный регистр 14. По окончании приема третьей посылки сигнал со счетчи1са 1 повторений поступает на коммутатор 6, который открывает второй ключ 13 и исправленная кодовая комбинация последовательным кодом выдается через элемент 17 ИЛИ на выход устройства для исправления ошибок. Кроме того, возможна вьщача исправленной кодовой комбинации параллельным кодом. В другом случае вторая и скорректированная первая посылки отличаются не больше, чем нал),,,, символов, либо совпадают. Когда в счетчике 7 будет записано .число, равное п- д п-максимальное

Авторы

Даты

1983-02-15—Публикация

1981-07-15—Подача