1

Изобретение относится к автоматическому контролю и может быть ис- , пользовано, например, для исследований скважин спускаемыми глубинными приборами, а также для других работ, связанных с совмещением данных, поступающих от линейно смещенных датчиков.

Известно электронное устройство совмещения данных, использующее запоминающие устройства, в частности, устройство совмещения глубин цифровой регистрирующей аппаратуры каротажа Н055.. В нем используется запоминающее устройство (блок памяти).разделенное на секции по числу каналов, причем каждая секция снабжена индивидyaJvьным счетчиком адреса, коэффициент пересчета (оторого равен максимально возможной задержке в каждом канале, причем в каждом конкретном случае величина задержки по каналу устанавливается с панели управления (датчик величины задержек) 1 .

Недостатком этого устройства является большой расход управляющего оборудования, ввиду индивидуальнопо управления каждым каналом.и его объ- ем растет пропорционально увеличению числа каналов. Некоторое снижение объема управляющего оборудования достигается в устройстве тем, что максимальные величины задержек в каналах устанавливаются различными, в первом канале - ноль, тье. он проходит без задержки, во втором не более 2 м (20 шагов квантования), в третьем - А м и т.д,, за счет этого уменьшается емкость адресных счетчиков в Каналах с небольшими задержками, но одновременно ограничиваются функциональные возможности.Наиболее близким к изобретению является устройство для управляемой

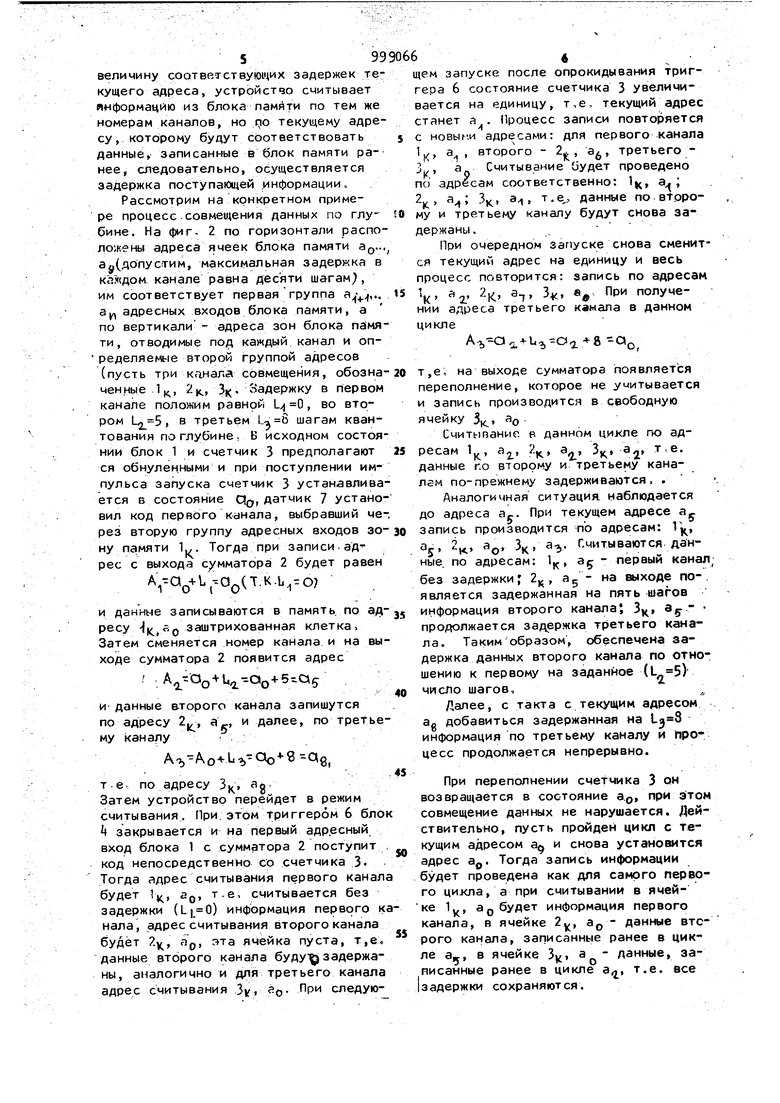

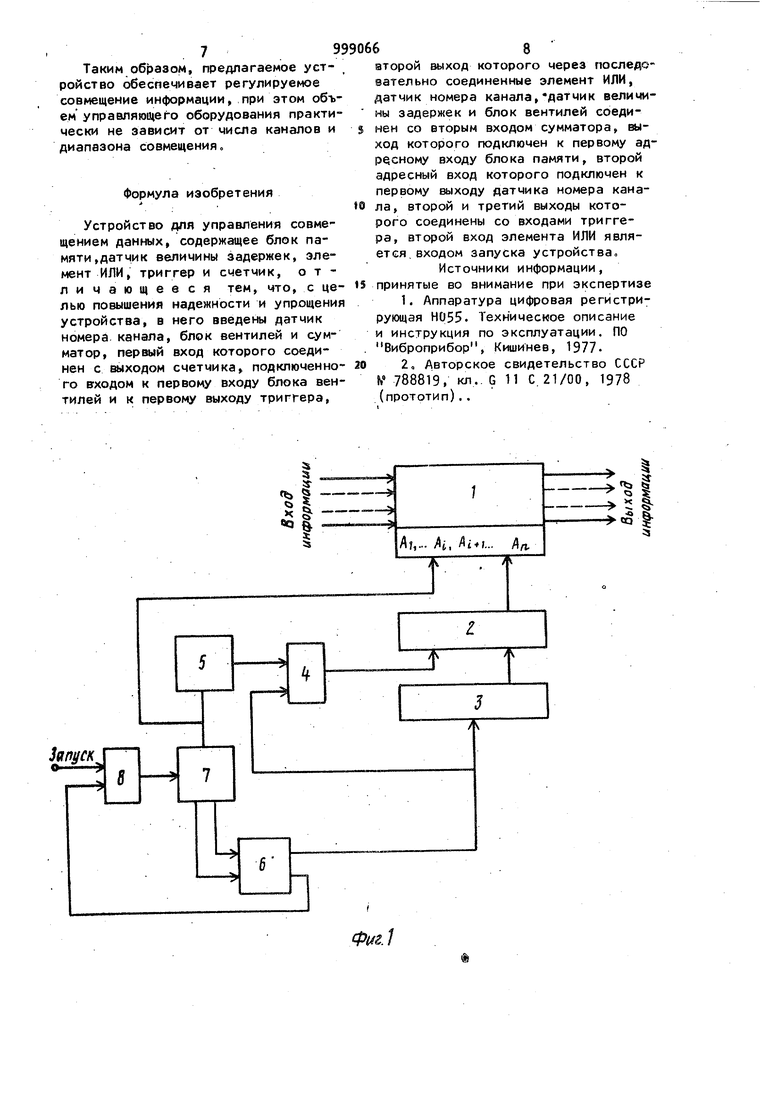

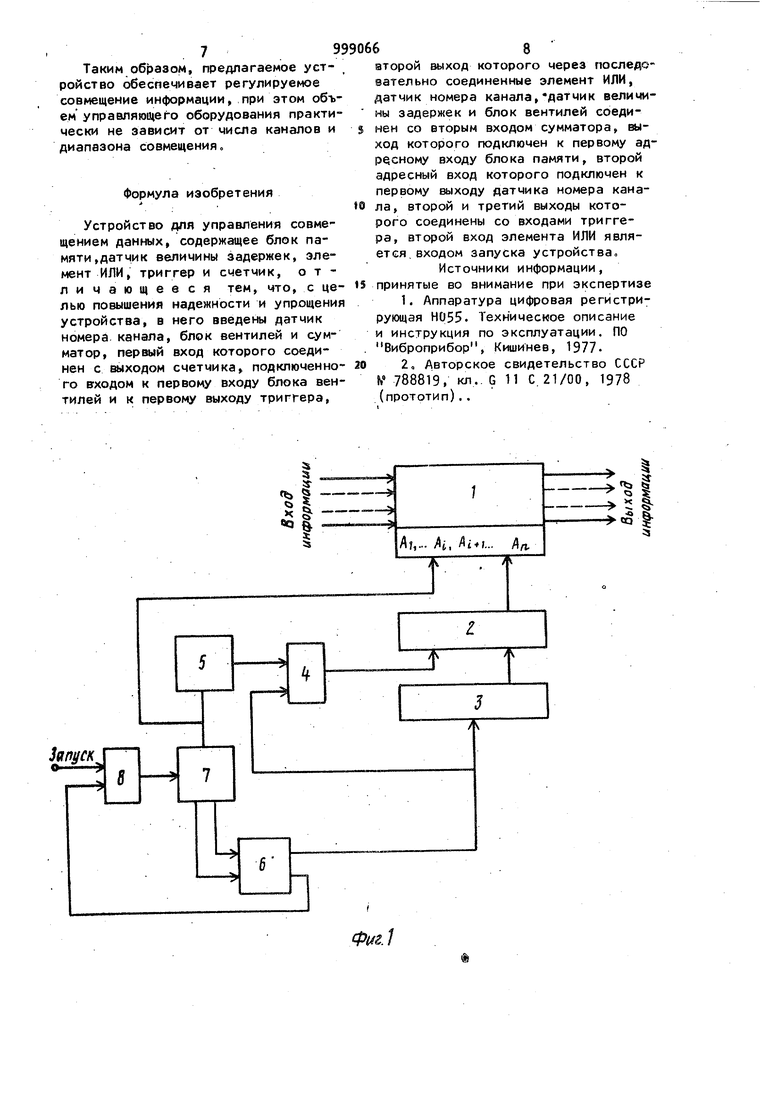

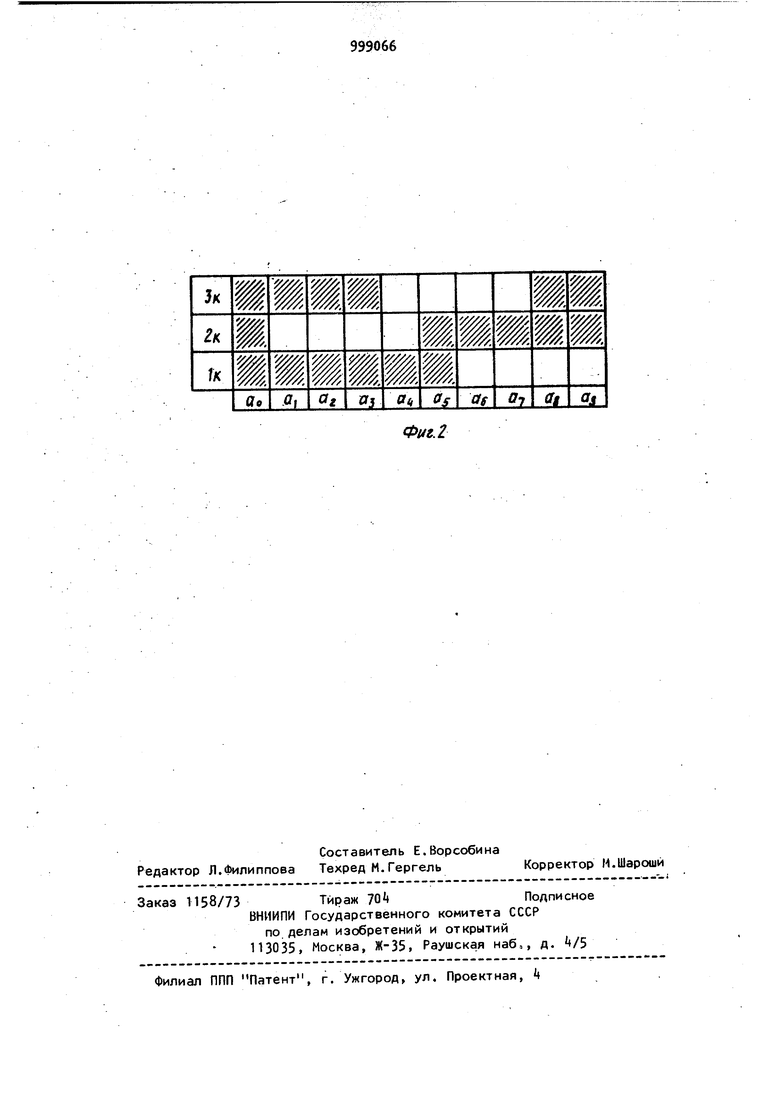

20 задержки цифровой информации , содержащее блок сдвигающих регистров (блок памяти), число которых равно разрядности записываемого кода параметра, адлина - максимально возможному числу шагов задержки- Инфор.мация синфазно с тактовыми импульсами, например импульсами глубины, последовательно накапливается в блоке регистров, .а число, тактовых импульсов суммируется в счетчике до тех пор, пока не станет равным коду, определяющему величину необходимой задержки. После этого с помощью высокочастотного генератора производится сдвиг информации на выход блока регистров и выдача ее потребителю.. Недостатком известного устройства является большой расход оборудования в частности, управляющего. Действительно, для задержки по N каналам с различными величинами задержек ходимо наличие К накопителей, каждый из которых имеет индивидуальную схему управления (счетчик,- схему равнозначности и ТоД-,),, Наличие большого числа одновременно работающих пересчетных схем снижает общую надежность устройства.. Целью изобретения является повышение надежности и упрощение устройстПоставленная цель достигается тем, что в устройство для управления совмещением данных, содержащее блок памяти, датчик величины задержек, элемент ИЛИ, триггер и счетчик, введ ны датчик номера канала, блок вентилей и сумматор, первый вход которого соединен с выходом счетчика, подкпю; ченного входом к первому входу блока вентилей и к первому выходу триггера, второй выход которого через последовательно соединенные элемент ИЛИ, датчик номера канала, датчик величины задержек и блок вентилей соединен со вторым входом сумматора, выход которого подключен к первому адресному входу блока памяти, второй адресный вход которого подключен к первому вы ходу датчика номера канала, второй и третий выходы которого соединены со входами триггера, второй вход элемента ИЛИ является входом запуска устройства На фиг 1 приведена функциональная схема устройства; на фиг. 2 - диаграм ма заполнения блока памяти. Устройство содержит блок 1 памяти. имеющий информационные входы и выходь число которых равно разрядности совмеи1аемых данных, и адресные входы .. сумматор 2, счетчик 3, бло 4 вентилей, датчик 5 величины задержек, триггер 6, датчик 7 номера канала и элемент ИЛИ 8. Устройство работает следующим образомЗапуск производится каждым импульсом квантования по глубине, иницирующим работу датчика 7 номера канала и источника информации При этом на первом выходе датчика 7 устанавливается код номера канала, поступающий одновременно на вход датчика 5 и второй адресный вход блока К Сигнал с выхода датчика 7 устанавливает триггер 6 в положение Запись, дающее разрешение на блок k и сменяющее адрее в счетчике 3 Код величины задержки, соответствующей номеру канала, через блок k поступает на сумматор 2, где складывается с текущим адресом из сметчика 3- Полученный новыи адрес подается на первый адресный вход блока 1, Таким образом, полный адрес, поданный на блок 1,определяется номером канала и результатом суммирования кода величины задержки данного канала и текущего адреса и опережает текущий адрес в счетчике 3 на величину требуемой задержки Затем датчик 7 выдает новый номер канала, которому с выхода датчика величин .задержек соответствует код задержки данного канала, суммирующийся с тем же текущим адресом со счетчика 3. Полный новый адрес ячейки блока 1, по которому записывается информационное слово нового канала опережает текущий -адрес на величину задержки этого канала. Этот цикл повторяется при постоянном текущем адресе счетчика 3, пока не будут исчерпаны все каналы, подлежащие совмещению После записи всех каналов сигнал с третьего выхода датчика 7 устанавливает триггер 6 в положение Считывание, при котором через элемент ИЛИ 8 снова иницируется работа датчика 7, блок k запирается и на соответствующие входы сумматора 2 поступают нули и считывание данных из блока 1 производится по текущему адресу счетчика 3 а в полном адресе, подаваемом уа блок 1, изменяется только номер канала с. Считав информацию по всем каналам, датчик 7 прекращает работу до поступления следующего импульса запуска Таким образом, записав информацию по всем каналам с опережением ил величину соответствующих задержек те кущего адреса , устройство считывает информац11ю из блока памяти по тем же номерам каналов, но rjo текущему адре су, которому будут соответствовать данные, записанные в блок памяти ранее, следовательно, осуществляется задержка поступающей информации. Рассмотрим на конкретном примере процесс совмещения данных по глубине. На фиг- 2 по горизонтали распо ложены адреса ячеек блока памяти а.. ао(допустим, максимальная задержка в кйждом канале равна десяти шагам), им соответствует первая группа ал,.. а адресных входов блока памяти, а по вертикали - адреса зон блока памя ти, отводимые под каждый,канал и оп ределяемые второй группой адресов (пусть три колала совмещения, обозна ченныеЛц, 2((,,3к Издержку в первом канале положим равной Ц 0, во втором , в третьем шагам квантования по глубине, Б исходном состоя нии блок 1 и счетчик 3 предполагают ся обнуленными и при поступлении импульса запуска счетчик 3 устанавлива ется в состояние сц, датчик 7 устано вил код первЬго канала, выбравший че рез вторую группу адресных входов зо ну памяти 1.,. Тогда при записи-адрес с выхода сумматора 2 будет равен А а 41--а(т.к.ь,го и данные записываются в память, по ад ресу заштрихованная клетка. Затем сменяется номер канала и на вы ходе сумматора 2 появится адрес .A,--Oo4U -. + 5x05 и данные второго канала запишутся по адресу 2j, а , и далее, по третье му каналу -. ,,, те по адресу Зк, ag Затем устройство перейдет в режим считывания. При. этом триггером 6 бло k закрывается и на первый адресный вход блока 1 с сумматора 2 поступит код непосредственно со счетчика 3Тогда адрес считывания первого канал будет 1 т-е, считывается без К .0 задержки () информация первого к нала, адрес считывания второго канала будет ., Пр, эта ячейка пуста, т,е, данные второго канала буду задержаны, аналогично и для третьего канала адрес считывания .3vf о- следующем запуске после опрокидывания три|- гера 6 состояние счетчика 3 увеличивается на единицу, т,е, текущий адрес станет а . Процесс записи повторяется для первого канала новыми адресами: а.. второго - 2, а, второго третьего Считывание Судет проведено есам соответственно: 1 COOT ве т с т вен но: К. а-. данные по второ)с. М -к. i му и третьему каналу будут снова задержаны . При очередном запуске снова сменится текущий адрес на единицу и весь процесс повторится: запись по адресам а При получе2. канала третьего в данном адреса цикле А -а ,.. U ,,-0,2. «-8 - GO т,е, на выходе сумматора появляется переполнение, которое не учитывается и запись производится в свободную ячейку 3 Считипание в данном цикле гю адресам 1, aj. -к г к. 1 данные г.о второму и третьему каналам по-прежнему задерживаются. . Аналогичная ситуация наблюдается адреса а. При текущем адресе а. до производится по адресам: Vy запись а. 3, Считываются дан3j, 2, OQ, j , а первый канал; ные. по адресам: без задержки j 2 а - на выходе по-. является задержанная на пять шагов информация второго канала 3ц, продолжается задержка третьего канала. Таким образом, обеспечена задержка данных второго канала по отношению к первому на заданное ()число шагов. Далее, с такта с текущим адресом ag добавиться задержанная на информация по третьему каналу и процесс продолжается непрерывно. При переполнении счетчика 3 он возвращается в состояние а.,, при этом совмещение данных не нарушается. Действительно, пусть пройден цикл с текущим адресом а и снова установится Тогда запись информации адрес а. будет проведена как для самого первого цихла, а при считывании в ячейке 1.., выбудет информация первого канала, в ячейке 2 а., - данные второго канала, записанные в цикле а, в ячейке 3 заа - данные, 5 писанные ранее т. е. все в цикле сохраняются. задержки

Таким образом, предлагаемое устройство обеспечивает регулируемое совмещение информации, при этом объем управляющего оборудования практически не зависит от числа каналов и диапазона совмещения.

Формула изобретения

Устройство для управления совмещением данных, содержащее блок памяти, датчик величины задержек, элемент ИЛИ, триггер и счетчик, отличающееся тем, что, с целью повышения надежности и упрощения устройства, в него введены датчик номера канала, блок вентилей и сумматор, первый вход которого соединен с выходом счетчика, подключенного входом к первому входу блока вентилей и к первому выходу триггера.

второй выход которого через последовательно соединенные элемент ИЛИ, датчик номера канала,датчик величины задержек и блок вентилей соединей со вторым входом сумматора, выход которого подключен к первому адресному входу блока памяти, второй адресный вход которого подключен к первому выходу датчика номера канала, второй и третий выходы которого соединены со входами триггера, второй вход элемента ИЛИ является, входом запуска устройства Источники информации,

принятые во внимание при экспертизе 1. Аппаратура цифровая регистрирующая Н055. Техническое описание и инструкция по эксплуатации. ПО Виброприбор, Кишинев, 1977.

2, Авторское свидетельство СССР « 788819, кл.. G 11 021/00, 1978 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Устройство для предварительной обработки информации | 1991 |

|

SU1837274A1 |

| Устройство для управления технологическим процессом | 1988 |

|

SU1522238A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Многопрограммный регулятор температуры | 1983 |

|

SU1136123A1 |

:&

:з

5Г

fb I

S| -

I

А,-.. AI, .. An,

IJ

Ф14г. /

Зх

гк

IX

т

014г. 2

Авторы

Даты

1983-02-23—Публикация

1981-07-23—Подача