Изобретение относится к вычислительной технике и может найти применение в специализированных вычислительных устройствах, используемых в системах автоматического управления.

Целью изобретения является повышение точности.

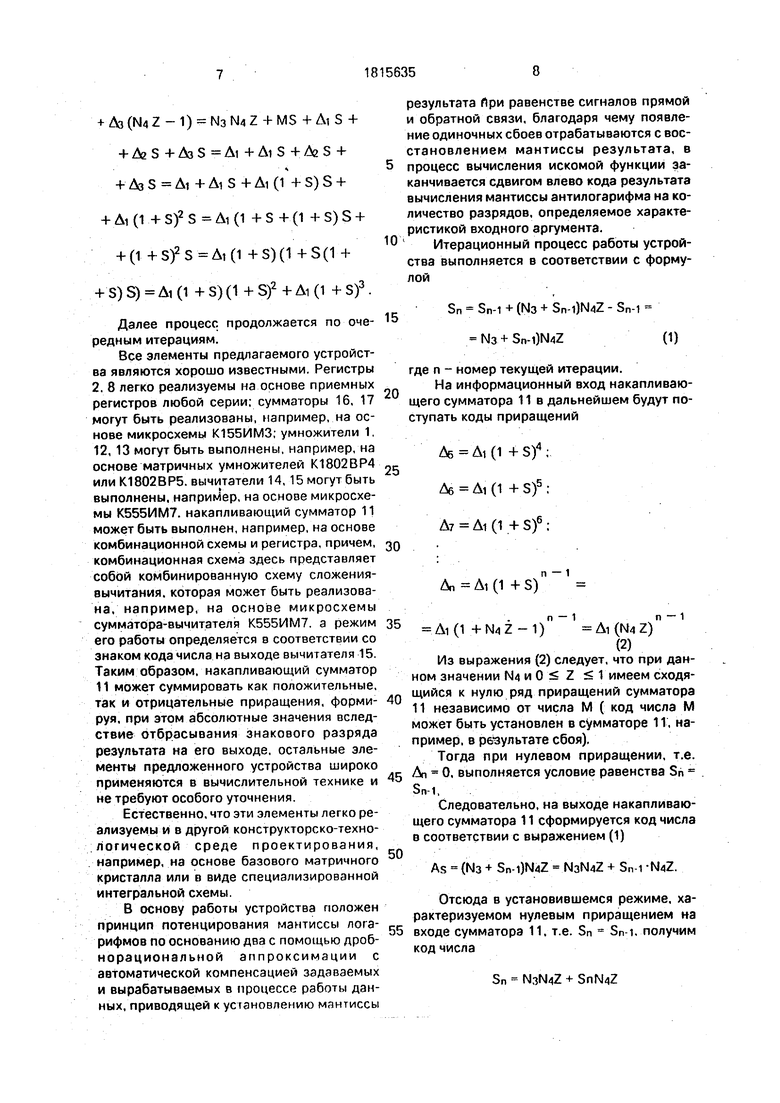

Предлагаемое устройство (см.фиг.1) содержит умножитель 1. регистр 2, выход характеристики которого подключен к первому входу счетчика 3, инверсные выходы которого соединены со входами элемента И 4, выход которого подключен к единичному входу триггера 5, выход которого соединен с первым входом дешифратора 6 окончания процесса вычисления, второй вход которого соединен с выходом генератора 7 импульсов, а первый выход - соединен со входом вычитания счетчика 3 и входом сдвига регистра 8, выход которого является выходом 9 устройства, выход цепочки последовательно соединенных элементов 10 задержки соединен с входом первого слагаемого сумматора 11. Устройство также содержит умножители 12, 13. вычита- теля 14,15, сумматоры 16,17, причем информационный вход регистра 2 соединен с входом 18 аргумента устройства, выход вы- читателя 15 через цепочку последовательно соединенных элементов 10 задержки подключен к третьему входу дешифратора 6 окончания процесса вычисления, четвертый и пятый входы которого соединены соответственное выходом элемента И 4 и входом 19 запуска устройства, который подключен к входу сброса триггера 5 и входу записи регистра 2. выход мантиссы которого соединен с входами первых сомножителей умножителей 12,13. входы вторых сомножителей которых подключены соответственно к входу 20 первой константы устройства и выходу сумматора 16, вход второй 21,

00

ел о

W

ел

третьей 22 и четвертой 23 констант устройства соединены соответственно с входом уменьшаемого вычитателя 14, входом первого слагаемого сумматора 16 и входом первого сомножителя умножителя 1, вход второго сомножителя и выход которого подключены соответственно к выходу умножителя 13 и входу уменьшаемого вычитателя 15, вход вычитаемого которого объединен с входом второго слагаемого сумматора 16, входом первого слагаемого сумматора 17 и подключен к выходу сумматора 11, второй вход которого соединен с выходом генератора 7 импульсов, второй выход дешифратора 6 окончания процесса вычисления соединен с входами записи счетчика 3 и регистра 8, информационный вход которого подключен к выходу сумматора 17, вход второго слагаемого которого соединен с выходом вычитателя 14, вход вычитаемого которого подключен к выходу умножителя 12.

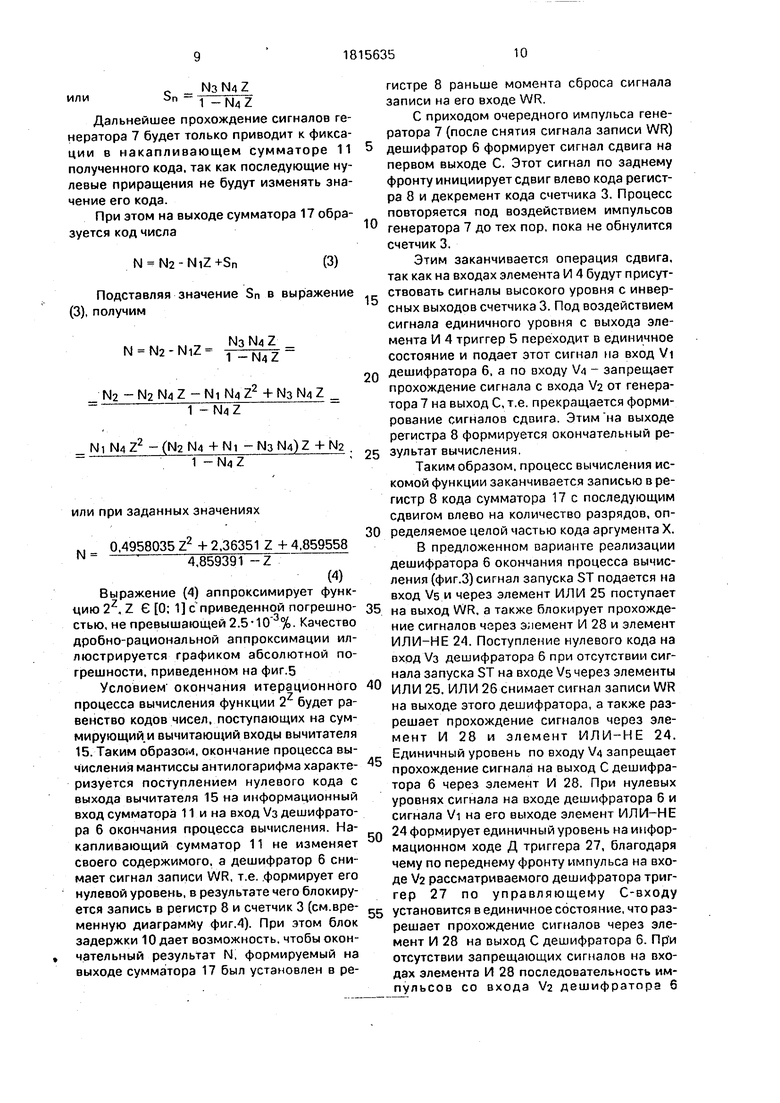

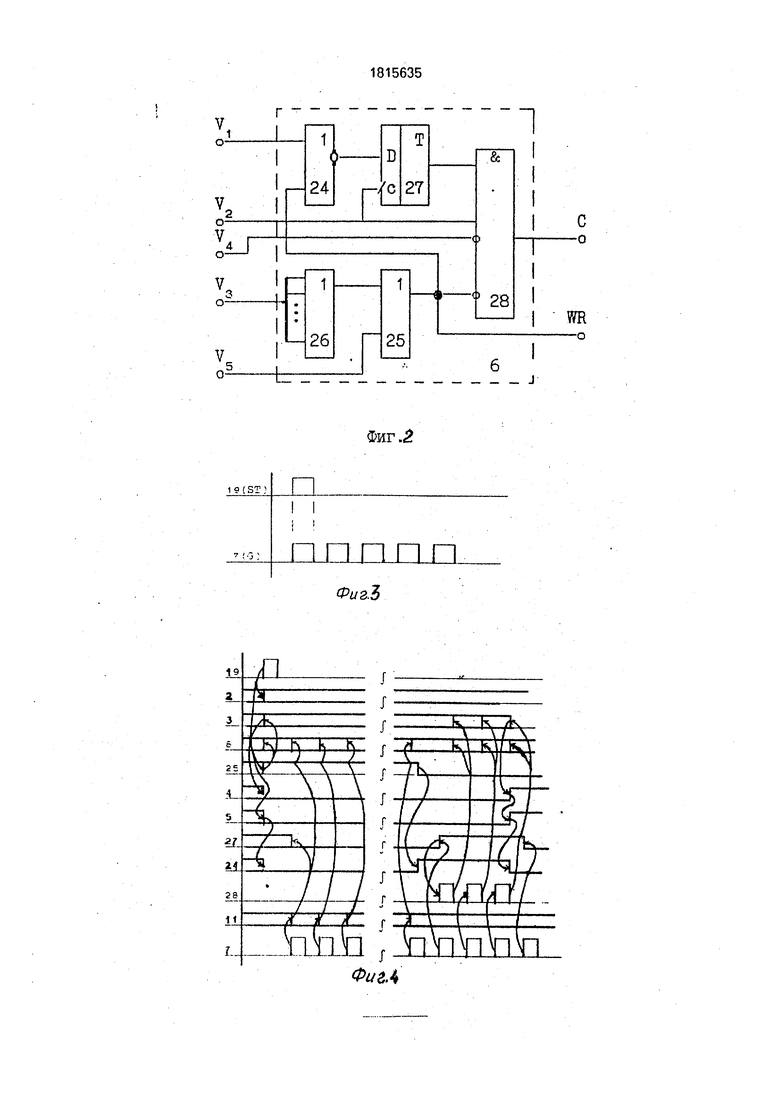

Дешифратор 6 окончания процесса вычисления (фиг.2) содержит элемент ИЛИ- НЕ 24, два элемента ИЛИ 25, 26, триггер 27 и элемент И 28, причем первый вход элемента ИЛИ-НЕ 24 является первым входом Vi дешифратора 6, а второй вход - соединен с первым инверсным входом элемента И 28, выходом элемента ИЛИ 25 и является вторым выходом WR дешифратора 6, первый выход С которого подключен к выходу элемента И 28, второй прямой вход которого соединен с входом синхронизации триггера 27 и является вторым входом MI дешифратора 6, третий Va, четвертый и пятый Vs входы которого подключены соответственно к входам элемента ИЛИ 26, третьему инверсному входу элемента И 28 и первому входу элемента ИЛИ 25, второй вход которого соединен с выходом элемента ИЛИ 26,. выход элемента ИЛИ-НЕ 24 соединен с информационным входом триггера 27, выход которого подключен к четвертому прямому входу элемента И 28.

Устройство работает следующим обра- зом.

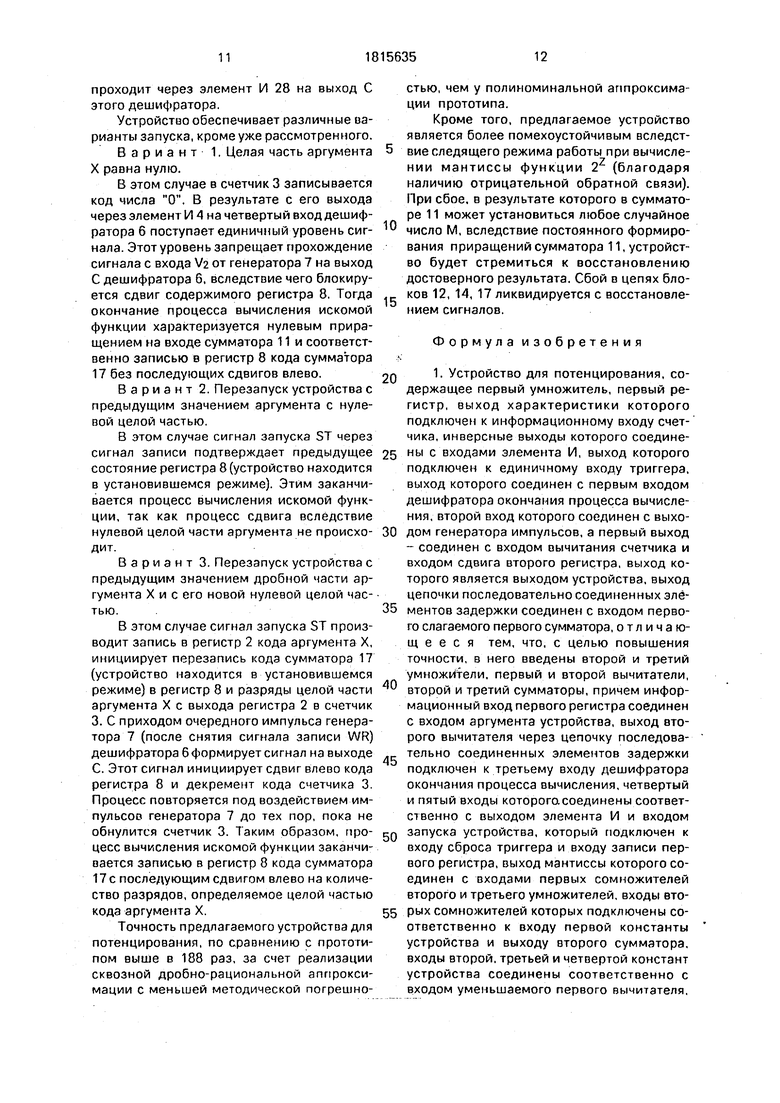

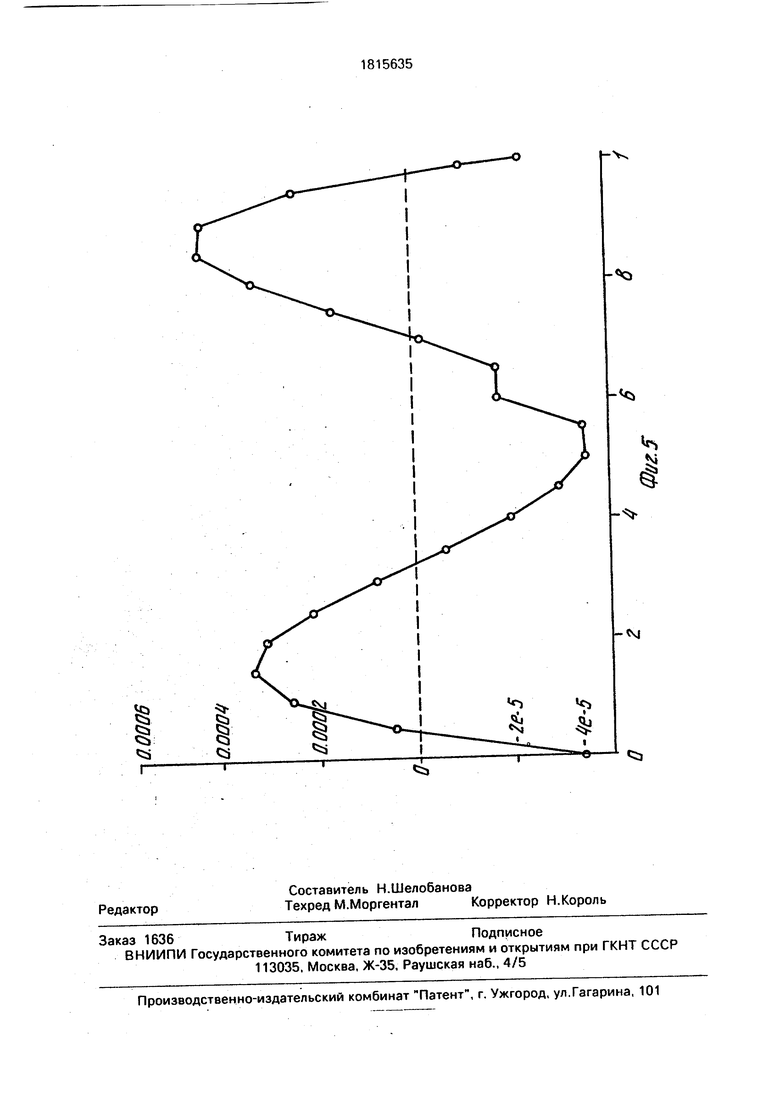

На вход 18 поступает код аргумента X, на вход 19 - сигнал запуска ST, а на остальных входах присутствуют коды Ni+N чисел 0.4958035,1.000034,5.772847,0.2057871 соответственно. Синхронизация поступления сигналов запуска ST с сигналами генератора 7 тактовых импульсов показана на фиг.З и обеспечивается внешними цепями синхронизации. Длительность сигналов генератора 7 должна быть .не менее времени задержки записи в накапливающем сумматоре 11, а период их следования - не менее суммарной задержки блоков 11,16,13,1,15, 10.

Пусть в момент запуска устройства на

5 выходе накапливающего сумматора 11 присутствует код числа So М. Поступает сигнал запуска ST, длительность которого не менее суммарного времени задержки регистра 2, п счетчика 3, триггера 5 и дешифратора 6 окончания процесса вычисления по пятому входу Vs. Передним фронтом этого сигнала производится запись в регистр 2 кода аргумента X, инициируется сброс триггера 5 и

с при нулевом состоянии выходных сигналов цепочки последовательно соединенных элементов 10 задержки устанавливается сигнал WR на выходе дешифратора б в единичное состояние. Сигнал записи пере0 пишет разряды целой части аргумента X с выхода регистра 2 в счетчик 3 и запишет в регистр 8, код с выхода сумматора 17. При других состояниях выходных сигналов цепочки последовательно соединенных эле5 ментов 10 задержки на выходе WR дешифратора 6 будет присутствовать уро- веньлогической единицы. В результате этого счетчик 3 и регистр 8 будут находиться в состоянии записи кодов регистра 2 и сумма0 тора 17 соответственно, что обусловлено статическим управлением записью.

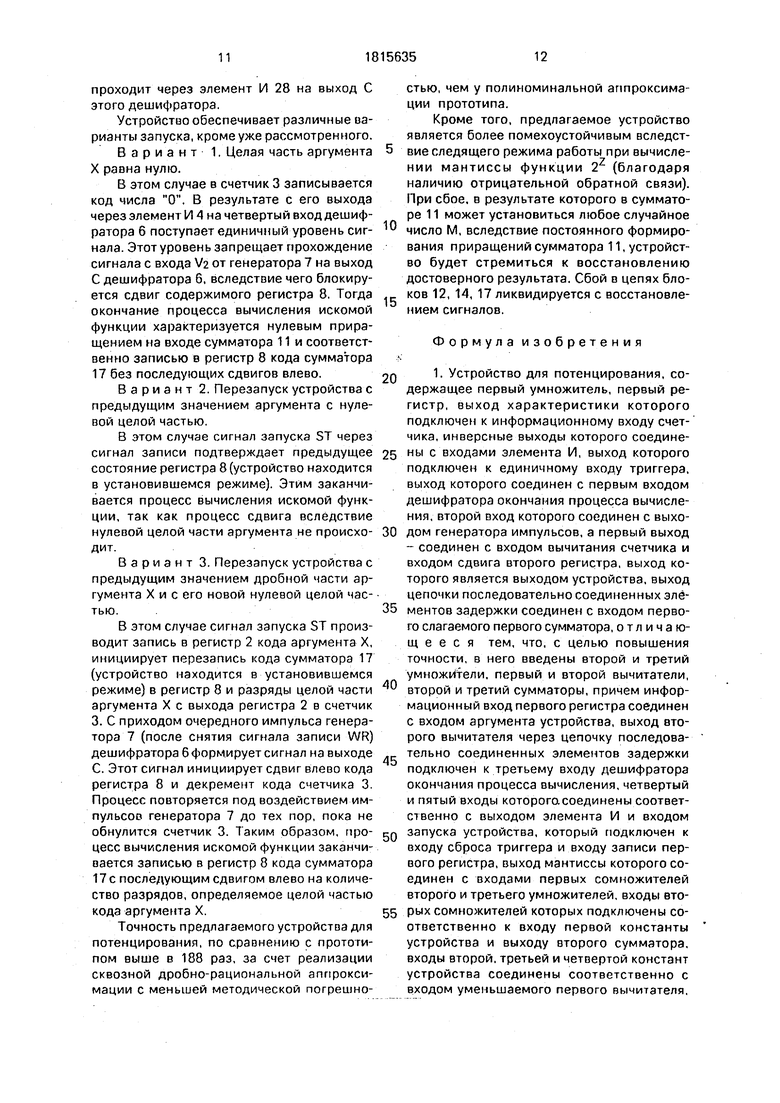

Состояние регистров 2, 8, накапливающего сумматора 11, счетчика 3, элемента И 4, триггера 5, сигналов записи WR и сдвига

5 с на выходах-дешифратора 6 до момента подачи сигнала запуска ST могут быть не определены, что и иллюстрируется временной диаграммой, приведенной на фиг.5, где

п изображаемые сигналы показаны как единичным, так и нулевым уровнем.

После запуска устройства на выходе сумматора 6 будет присутствовать код суммы кода М с выхода сумматора 11 и входного

5 кода N3, т.е. Na+M. Этот код поступает на первый вход умножителя 13, на второй вход которого подаются разряды дробной части Z аргумента X. В результате с выхода умножителя 13 на первый вход умножителя 1

0 передается код произведения (N3+M)Z, где умножается на входной код N4, т.е. на выходе умножителя 1 получим код следующего произведения (Na+MJZN/j. При этом с выходов умножителей 1, 12, 13, выполненных,

5 например, на базе матричных БИС 1802ВР4 или 1802ВР5, снимается старшая половина разрядов результата умножения.

Таким образом, в результате первой итерации с выхода вычитателя 15 через цепочку последовательно соединенных эле5 1815635 6

ментов 10 задержки на первый информаци-Sa Si + Дг М AI + До. онный вход накапливающего сумматора 11

поступит код числаЭтот код суммируется сумматором 16 с

входным кодом числа Мз. Тогда на выходе

AT (Na + S0)N4Z - So (N3 + M)N4Z - М 5 сумматора 16 сформируется код числа Мз +

М + AI + Л. а на выходах умножителей 13 NsN4Z + MN4Z - М NsN4Z + M(N/iZ 1 соответственно NsN4Z + MS,(N3 + М + Ai + Ae )Z

10 и

rfleS N4Z-1.(Мз + М+ Ai+A )ZN4

Цепочка последовательно соединенных

элементов 10 задержки служит для задерж-В процессе выполнения третьей итера- ки выходного кода вычитателя 15 на время, ции с выхода вычитателя 15 в сумматор 11 не менее суммарного времени задержки поступает код приращения сумматора 17 и регистра 8, что позволяет

при получении всех нулей осуществить за-Аз (N3 + S2)N4Z - 82 - (N3+ М + держку сброса сигнала записи WR с выхода

элемента ИЛИ 25 до окончания формирова- 2Q + Ai + Дг )N4Z - (М + Ai + Да ) МзМд2+ ния кода суммы сумматора 17.

В результате в накапливающем сумма-+ MN4Z + Ai N4Z + Д N4Z -М- Ai - А2 торе 11с приходом на его второй управляющий вход переднего фронта сигнала NsN4Z + M(N4Z - 1) + Ai(N4Z - 1) +Aj генератора 7 установится код числа 9R

(N4Z -1) N3N4Z + MS + Ai S + Дг S Ai +

Si S0+ Ai M +Ai

+ Ai S + Ao S Ai + Ai S + Ai (1 + S) S

Затем этот код суммируется сумматором 16 с кодом числа и вырабатывается еле- 30 Ai(1 +S-f(1 -f-S) S) AI (1 +S)2. дующий результат N3 + M +Ai

Полученная сумма, как и в первом ите-Код приращения Аз аналогично пред- рационном цикле, умножается на произве- ыдущим итерациям будет просуммирован с дение N4Z с помощью умножителей 13 и 1. содержимым сумматора 11 с приходом оче- Очевидно, на выходе последнего будет 35 редного сигнала генератора 7, т.е. в накап- сформирован код ливающем сумматоре 11 получится код

числа 5з S2 + Аз М + Ai + Аг + Аз . (Мз + М + Ai )N4 ZЭтот код суммируется сумматором 16 с

входным кодом числа Мз.

Тогда с выхода вычитателя 15 во втором 40 Тогда на выходе сумматора 16 сформи- цикле итерационного процесса в сумматор руется код числа Мз + М + AI + Аг + Аз , а 11 поступит код приращенияна выходе умножителя 1 - (Мз + М

+ Ai + А2 + Аз )N/iZ.

Да (Мз + Si)N4Z - Si (N3 + М + Ai )N4Z - 45 Четвертый цикл итерационного процесса характеризуется приращением суммато- - (М + Ai) N3N4Z + MN4Z + Ai N4Z - М-рэ 11 на величину

- Ai N3N4Z + M(N4Z - 1) + Ai (N4Z - 1)A« (N3 + S3) N4 Z - S3

- + MS + Ai S (N3 + M -f Ai + Aa + Аз) N4 Z Ai+ AiS Ai(1 + S).-(M+Ai+Az+AB) N3N4Z+MN4Z +

Код приращения А2 будет просуммиро- 55+ Ai N4 Z Ч- Д N4 Z + Аз N4 Z - ван с содержимым сумматора 11 с приходом

очередного сигнала генератора 7, т.е. в на- -М - Ai - Аг - Ач Мз N4 Z -f М (N4Z - 1) + капливающем сумматоре 11 получится код

числа+ Ai (N4 Z - 1) Ч- Аз (N4 Z - 1) +

Ч- Аз (N4 Z - 1) N3 N Z + MS + Ai S + + A2S+A3S Ai+AiS+A2S +

-f Аз S Ai + Ai S + Ai (1 + S) S +

+ Ai (1.+ S)2 S Ai (1 + S -f (1 + S) S +

+ (1 +S)(1 +S)(1+S(1 +

+ S)S)Ai(1 + S)(1 + S)2+Ai(1 +S)3.

Далее процесс продолжается по очередным итерациям.

Все элементы предлагаемого устройства являются хорошо известными. Регистры 2, 8 легко реализуемы на основе приемных регистров любой серии; сумматоры 16, 17 могут быть реализованы, например, на основе микросхемы К155ИМЗ; умножители 1, 12, 13 могут быть выполнены, например, на основе матричных умножителей К1802ВР4 или К1802ВР5. вычитатели 14, 15 могут быть выполнены, например, на основе микросхемы К555ИМ7. накапливающий сумматор 11 может быть выполнен, например, на основе комбинационной схемы и регистра, причем, комбинационная схема здесь представляет собой комбинированную схему сложения- вычитания, которая может быть реализована, например, на основе микросхемы сумматбра-вычитателя К555ИМ7. а режим его работы определяется в соответствии со знаком кода числа на выходе вычитателя 15. Таким образом, накапливающий сумматор 11 может суммировать как положительные, так и отрицательные приращения, формируя, при этом абсолютные значения вследствие отбрасывания знакового разряда результата на его выходе, остальные элементы предложенного устройства широко применяются в вычислительной технике и не требуют особого уточнения.

Естественно, что эти элементы легко реализуемы и в другой конструкторско-техно- ;логической среде проектирования, например, на основе базового матричного кристалла или в виде специализированной интегральной схемы.

В основу работы устройства положен принцип потенцирования мантиссы логарифмов по основанию два с помощью дроб- норациональной аппроксимации с автоматической компенсацией задаваемых и вырабатываемых в процессе работы данных, приводящей к установлению мантиссы

0

5

0

результата при равенстве сигналов прямой и обратной связи, благодаря чему появление одиночных сбоев отрабатываются с восстановлением мантиссы результата, в процесс вычисления искомой функции заканчивается сдвигом влево кода результата вычисления мантиссы антилогарифма на количество разрядов, определяемое характеристикой входного аргумента.

Итерационный процесс работы устройства выполняется в соответствии с формулой

Sn Sn-1 + (N3 + Sn-l)N4Z - Sn-1 - N3 + Sn-l)N4Z(1)

где п - номер текущей итерации.

На информационный вход накапливающего сумматора 11 в дальнейшем будут поступать коды приращений

25

As Ai (1 + S)4 ;. Дб At (1 + S)5 ; (1 +S)6;

30

5

0

5

0

(1+S)

Ai(1 + N4Z -1) Ai(N4Z)

(2)

Из выражения (2) следует, что при данном значении N4 и 0 Z 1 имеем сходящийся к нулю ряд приращений сумматора 11 независимо от числа М ( код числа М может быть установлен в сумматоре 11, например, в результате сбоя),

Тогда при нулевом приращении, т.е. An 0, выполняется условие равенства Sh

Sn1,

Следовательно, на выходе накапливающего сумматора 11 сформируется код числа в соответствии с выражением (1)

As (Мз + Sn-i)N4Z NaN4Z + Sn i-N4Z.

Отсюда в установившемся режиме, характеризуемом нулевым приращением на входе сумматора 11. т.е. Sn Sni, получим код числа

Sn N.3N4Z +

или

Sn

1 -N4Z

Дальнейшее прохождение сигналов генератора 7 будет только приводит к фиксации в накапливающем сумматоре 11 полученного кода, так как последующие нулевые приращения не будут изменять значение его кода.

При этом на выходе сумматора 17 образуется код числа

N №-NiZ+Sn

(3)

Подставляя значение Sn в выражение (3), получим

м м м -7 NaNUZ N N2-NiZ

N2 -N2N4Z -N1 N4Z2 + N3N4Z 1 -NoZ

N1 N4Z2 -(N2 N4 +Ni -N3N4)Z +N2 . 1 -N4Z;

или при заданных значениях

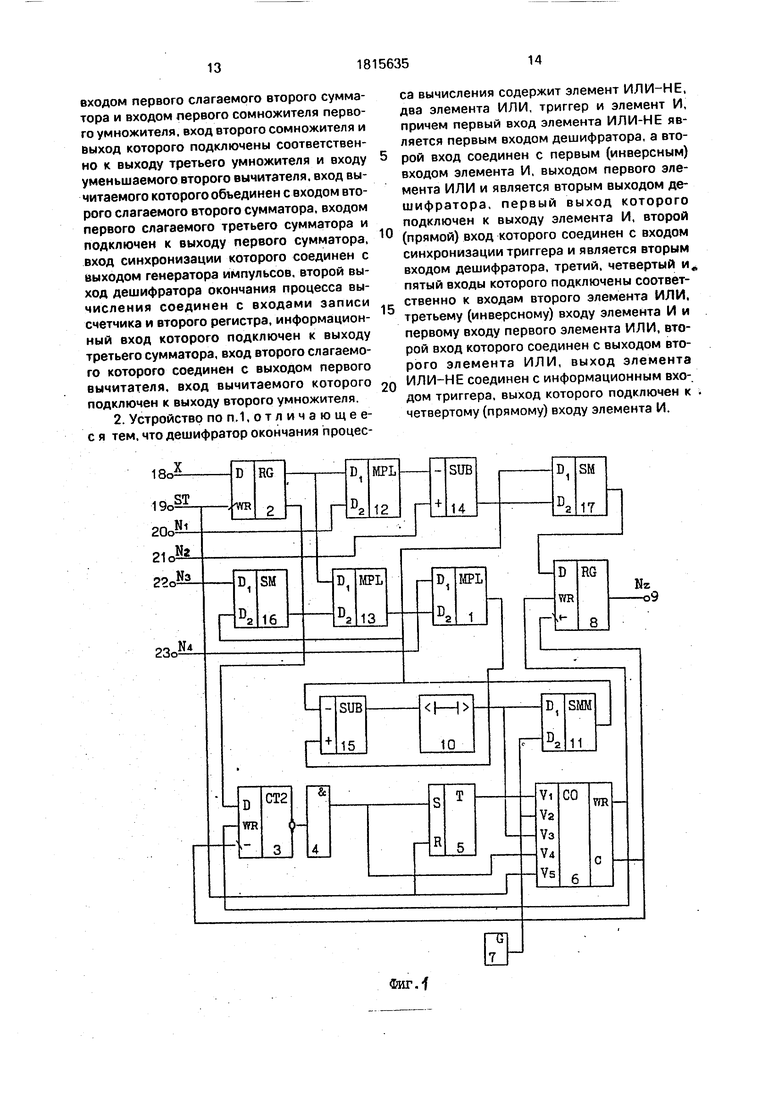

w 0.4958035 Z2 +2.36351 Z +4.859558 N4,859391 -Z

(4)

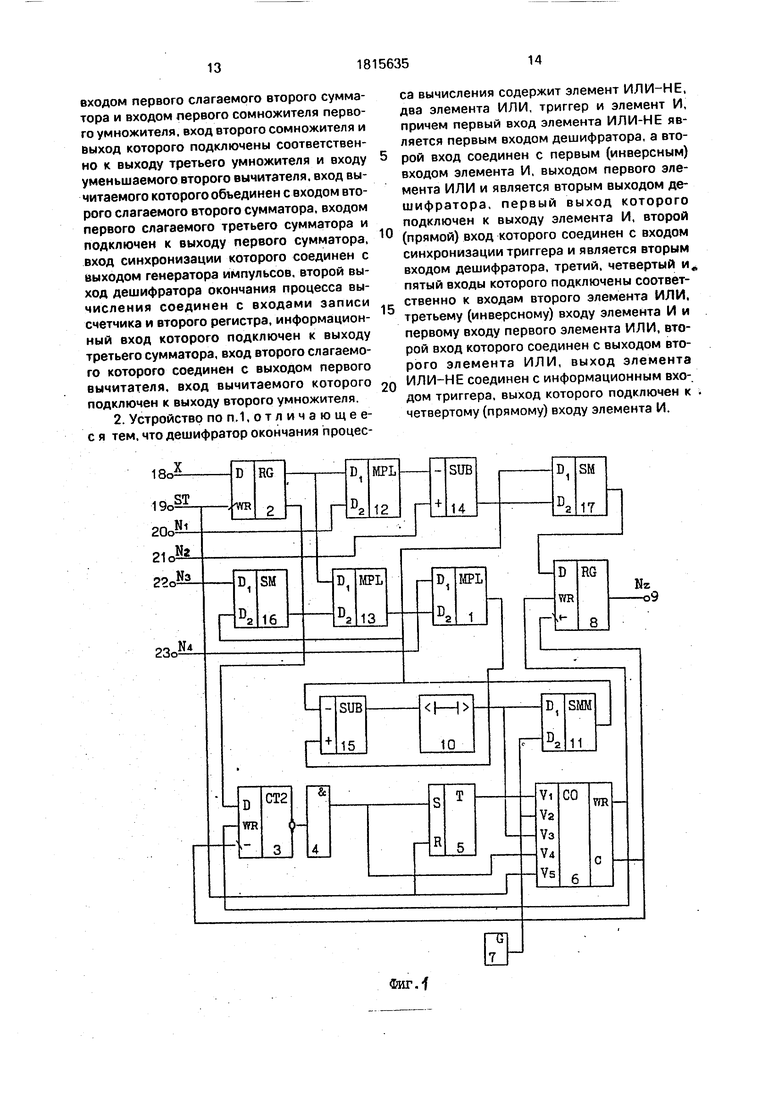

Выражение (4) аппроксимирует функцию 2Z, Z 6 0; 1 с приведенной погрешностью, не превышающей 2.. Качество дробно-рациональной аппроксимации иллюстрируется графиком абсолютной погрешности, приведенном на фиг.5

Условием окончания итерационного процесса вычисления функции 2Z будет равенство кодов чисел, поступающих на суммирующий и вычитающий входы вычитателя 15. Таким образом, окончание процесса вычисления мантиссы антилогарифма характеризуется поступлением нулевого кода с выхода вычитателя 15 на информационный вход сумматора 11 и на вход Va дешифратора 6 окончания процесса вычисления. Накапливающий сумматор 11 не изменяет своего содержимого, а дешифратор 6 снимает сигнал записи WR, т.е. .формирует его нулевой уровень, в результате чего блокируется запись в регистр 8 и счетчик 3 (см.временную диаграмму фиг.4). При этом блок задержки 10 дает возможность, чтобы окон- нательный результат N, формируемый на выходе сумматора 17 был установлен в ре

гистре 8 раньше момента сброса сигнала записи на его входе WR.

С приходом очередного импульса генератора 7 (после снятия сигнала записи WR) дешифратор 6 формирует сигнал сдвига на первом выходе С. Этот сигнал по заднему фронту инициирует сдвиг влево кода регистра 8 и декремент кода счетчика 3. Процесс повторяется под воздействием импульсов генератора 7 до тех пор, пока не обнулится счетчик 3.

Этим заканчивается операция сдвига, так как на входах элемента И 4 будут присутствовать сигналы высокого уровня с инверсных выходов счетчика 3. Под воздействием сигнала единичного уровня с выхода элемента И 4 триггер 5 переходит в единичное состояние и подает этот сигнал на вход Vi

дешифратора 6, а по входу - запрещает прохождение сигнала с входа V2 от генератора 7 на выход С, т.е. прекращается формирование сигналов сдвига. Этим на выходе регистра 8 формируется окончательный результат вычисления.

Таким образом, процесс вычисления искомой функции заканчивается записью в регистр 8 кода сумматора 17 с последующим сдвигом влево на количество разрядов, определяемое целой частью кода аргумента X. В предложенном варианте реализации дешифратора 6 окончания процесса вычисления (фиг.З) сигнал запуска ST подается на вход Vs и через элемент ИЛИ 25 поступает

на выход WR, а также блокирует прохождение сигналов чзрез элемент И 28 и элемент ИЛИ-НЕ 24. Поступление нулевого кода на вход Va дешифратора 6 при отсутствии сигнала запуска ST на входе VB через элементы

ИЛИ 25. ИЛИ 26 снимает сигнал записи WR на выходе этого дешифратора, а также разрешает прохождение сигналов через элемент И 28 и элемент ИЛИ-НЕ 24.

Единичный уровень по входу V4 запрещает прохождение сигнала на выход С дешифратора 6 через элемент И 28. При нулевых уровнях сигнала на входе дешифратора 6 и сигнала Vi на его выходе элемент ИЛИ-НЕ

24 формирует единичный уровень на информационном ходе Д триггера 27, благодаря чему по переднему фронту импульса на входе V2 рассматриваемого дешифратора триггер 27 по управляющему С-входу

установится в единичное состояние, что разрешает прохождение сигналов через элемент И 28 на выход С дешифратора 6. При отсутствии запрещающих сигналов на входах элемента И 28 последовательность импульсов со входа V2 дешифратора б

проходит через элемент И 28 на выход С этого дешифратора.

Устройство обеспечивает различные варианты запуска, кроме уже рассмотренного.

Вариант 1. Целая часть аргумента X равна нулю.

В этом случае в счетчик 3 записывается код числа О. В результате с его выхода через элемент И 4 на четвертый вход дешифратора 6 поступает единичный уровень сигнала. Этот уровень запрещает прохождение сигнала с входа V2 от генератора 7 на выход С дешифратора 6, вследствие чего блокируется сдвиг содержимого регистра 8, Тогда окончание процесса вычисления искомой функции характеризуется нулевым приращением на входе сумматора 11 и соответственно записью в регистр 8 кода сумматора 17 без последукж1их сдвигов влево.

Вариант 2. Перезапуск устройства с предыдущим значением аргумента с нулевой целой частью.

В этом случае сигнал запуска ST через сигнал записи подтверждает предыдущее состояние регистра 8 (устройство находится в установившемся режиме). Этим заканчивается процесс вычисления искомой функции, так как процесс сдвига вследствие нулевой целой части аргумента не происходит.

Вариант 3. Перезапуск устройства с предыдущим значением дробной части аргумента X и с его новой нулевой целой частью.

В этом случае сигнал запуска ST производит запись в регистр 2 кода аргумента X, инициирует перезапись кода сумматора 17 (устройство находится в установившемся режиме) в регистр 8 и разряды целой части аргумента X с выхода регистра 2 в счетчик 3. С приходом очередного импульса генератора 7 (после снятия сигнала записи WR) дешифратора 6 формирует сигнал на выходе С. Этот сигнал инициирует сдвиг влево кода регистра 8 и декремент кода счетчика 3. Процесс повторяется под воздействием им- пульсоо генератора 7 до тех пор, пока не обнулится счетчик 3. Таким образом, процесс вычисления искомой функции заканчивается записью в регистр 8 кода сумматора 17с последующим сдвигом влево на количество разрядов, определяемое целой частью кода аргумента X.

Точность предлагаемого устройства для потенцирования, по сравнению с прототипом выше в 188 раз, за счет реализации сквозной дробно-рациональной аппроксимации с меньшей методической погрешно:

15

стью, чем у полиноминальной аппроксимации прототипа.

Кроме того, предлагаемое устройство является более помехоустойчивым вследст5 вне следящего режима работы при вычислении мантиссы функции 2Z (благодаря наличию отрицательной обратной связи). При сбое, в результате которого в сумматоре 11 может установиться любое случайное

число М, вследствие постоянного формирования приращений сумматора 11, устройство будет стремиться к восстановлению достоверного результата. Сбой в цепях блоков 12, 14, 17 ликвидируется с восстановлением сигналов.

Ф о р м у л а и з о б р е т е н и я

1. Устройство для потенцирования, содержащее первый умножитель, первый регистр, выход характеристики которого подключен к информационному входу счет- чика, инверсные выходы которого соединены с входами элемента И, выход которого подключен к единичному входу триггера, выход которого соединен с первым входом дешифратора окончания процесса вычисления, второй вход которого соединен с выходом генератора импульсов, а первый выход - соединен с входом вычитания счетчика и входом сдвига второго регистра, выход которого является выходом устройства, выход цепочки последовательно соединенных элементов задержки соединен с входом первого слагаемого первого сумматора, отличающееся тем, что, с целью повышения точности, в него введены второй и третий умножители, первый и второй вычитатели, второй и третий сумматоры, причем информационный вход первого регистра соединен с входом аргумента устройства, выход второго вычитателя через цепочку последовательно соединенных элементов задержки подключен к третьему входу дешифратора окончания процесса вычисления, четвертый и пятый входы которого.соединены соответственно с выходом элемента И и входом

запуска устройства, который подключен к входу сброса триггера и.входу записи первого регистра, выход мантиссы которого соединен с входами первых сомножителей второго и третьего умножителей, входы вторых сомножителей которых подключены соответственно к входу первой константы устройства и выходу второго сумматора, входы второй, третьей и четвертой констант устройства соединены соответственно с входом уменьшаемого первого вычитателя,

входом первого слагаемого второго сумматора и входом первого сомножителя первого умножителя, вход второго сомножителя и выход которого подключены соответственно к выходу третьего умножителя и входу уменьшаемого второго вычитателя. вход вычитаемого которого объединен с входом второго слагаемого второго сумматора, входом первого слагаемого третьего сумматора и подключен к выходу первого сумматора, вход синхронизации которого соединен с выходом генератора импульсов, второй выход дешифратора окончания процесса вычисления соединен с входами записи счетчика и второго регистра, информационный вход которого подключен к выходу третьего сумматора, вход второго слагаемого которого соединен с выходом первого вычитателя, вход вычитаемого которого подключен к выходу второго умножителя.

2. Устройство по п..1, о т л и ч а ю щ е е- с я тем. что дешифратор окончания процесса вычисления содержит элемент ИЛИ-НЕ, два элемента ИЛИ, триггер и элемент И, причем первый вход элемента ИЛИ-НЕ является первым входом дешифратора, а второй вход соединен с первым (инверсным) входом элемента И, выходом первого элемента ИЛИ и является вторым выходом дешифратора, первый выход которого подключен к выходу элемента И, второй

0 (прямой) вход которого соединен с входом синхронизации триггера и является вторым входом дешифратора, третий, четвертый и« пятый входы которого подключены соответственно к входам второго элемента ИЛИ, третьему (инверсному) входу элемента И и первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ, выход элемента

0 ИЛИ-НЕ соединен с информационным вхо-. дом триггера, выход которого подключен к четвертому (прямому) входу элемента И.

Фи&4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления тригонометрического тангенса | 1986 |

|

SU1334144A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления обратных тригонометрических функций | 1981 |

|

SU964633A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Вычислительное устройство | 1981 |

|

SU1022166A1 |

Изобретение относится к вычислительной технике и может найти применение в специализированных вычислительных устройствах, используемых в системах автоматического управления. Цель: повышение точности. Сущность: создание устройства для потенцирования с использованием итерационного метода вычисления посредством организации структуры с отрицательной обратной связью для выработки компенсирующих воздействий при получении дробно-рационального аппроксимирующего выражения и с повышением, благодаря этому, точности. 1 з.п.ф-лы, 6 ил. (Л С

| УСТРОЙСТВО для ПОТЕНЦИРОВАНИЯ ЛОГАРИФМОВ ПО ОСНОВАНИЮ ДВА | 0 |

|

SU304574A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| Устройство для потенцирования логарифмов по основанию два | 1982 |

|

SU1020819A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для потенцирования | 1976 |

|

SU633017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1993-05-15—Публикация

1990-11-11—Подача