Изобретение относится к цифровым вычислительным машинам и может быть использовано в устройствах мультипрограммирования, например, с помощью прерываний.

Известен блок приоритетных прерываний, содержащий регистр запросов прерываний, регистр текущего приоритета, схему анализа приоритета, триггер прерывания, усилители считывания.

Недостатком этого блока является большое время реакции на прерывание.

Наиболее близким по технической сущности к предложенному устройству является выбранное в качестве прототипа устройство прерываний последовательного опроса, содержащее дешифратор, триггер прерывания, регистр запросов прерываний, состоящий из триггеров запросов внешних устройств, последовательно соединенные генератор, счетчик и усилители считывания (схема И), вход которых дополнительно соединен с входом дешифратора, при этом выходы усилителей считывания являются первым выходом устройства, а выход триггера прерывания - вторым выходом устройства, вход разрешения усилителей считывания является первым входом устройства, а N входов S регистра запросов - вторым входом устройства.

Устройство производит последовательный опрос запросов прерываний, что позволяет значительно уменьшить время реакции на прерывание.

Недостатком известного устройства является отсутствие распределения прерываний по приоритету.

Если поступил запрос от внешнего устройства на выполнение более срочной задачи в момент обработки задачи с меньшей степенью срочности, то известное устройство приступит к обработке этой задачи только после завершения обработки текущего запроса. Таким образом может увеличиться время реакции на прерывание.

Целью изобретения является уменьшение времени реакции на прерывание.

Указанная цель достигается тем, что устройство приоритетных прерываний, содержащее первый дешифратор, триггер прерывания, регистр запросов прерываний, последовательно соединенные генератор, счетчик и усилители считывания, вход которых дополнительно соединен с входом первого дешифратора, при этом М выходов усилителей считывания является первым выходом устройства, а выход триггера прерывания - вторым выходом устройства, вход разрешения усилителей считывания является первым входом устройства, а N входов S регистра запросов прерывания является вторым входом устройства, дополнительно снабжено первым мультиплексором, распределителем импульсов, последовательно соединенными вторым распределителем импульсов, схемой И, схемой ИЛИ, а также последовательно соединенными вторым дешифратором, регистром текущего прерывания, вторым мультиплексором и схемой анализа приоритета, выход которой соединен с входом D триггера прерываний, инверсный выход которого соединен с вторым входом схемы И, а синхровход - с вторым выходом второго распределителя импульсов, запускающий вход которого соединен с вторым выходом счетчика, первый вход которого дополнительно соединен с синхровходами второго и первого распределителей импульсов, запускающий вход которого соединен с управляющим входом усилителей считывания, а первый выход соединен со стробирующим входом первого дешифратора, второй выход - с входом R триггера прерываний и третий выход - с вторым входом схемы ИЛИ, выход которой соединен с вторым входом счетчика, первый выход которого дополнительно соединен с адресными входами второго и первого мультиплексоров, выход которого соединен с третьим входом счетчика и с вторым входом схемы анализа приоритета. Выходы первого дешифратора соединены с входами S регистра текущего прерывания, а выходы второго дешифратора соединены с входами R регистра запросов прерываний, выходы которого соединены с входами первого мультиплексора, при этом М входов второго дешифратора является третьим входом устройства.

Сопоставительный анализ с прототипом показывает, что предложенное устройство отличается наличием новых блоков: дополнительного дешифратора, регистра текущего прерывания, схемы анализа прерывания, мультиплексора, распределителя импульсов и их связями с остальными элементами схемы.

Таким образом, заявляемое устройство соответствует критерию изобретения "новизна".

Сравнение предложенного решения с другими техническими решениями показывает, что дешифратор, регистр текущего прерывания, схема анализа прерывания, мультиплексор, распределитель импульсов, схемы И и ИЛИ широко известны.

Однако при их введении в указанной связи с остальными элементами схемы в предложенное устройство приоритетных прерываний указанные блоки проявляют новые свойства, что уменьшает время реакции на прерывание. Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

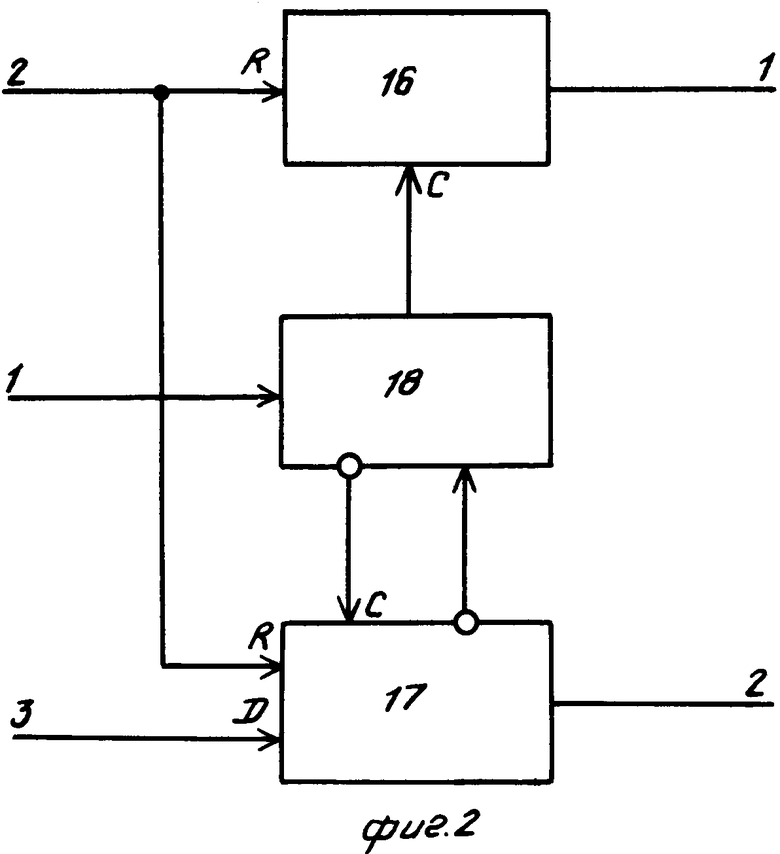

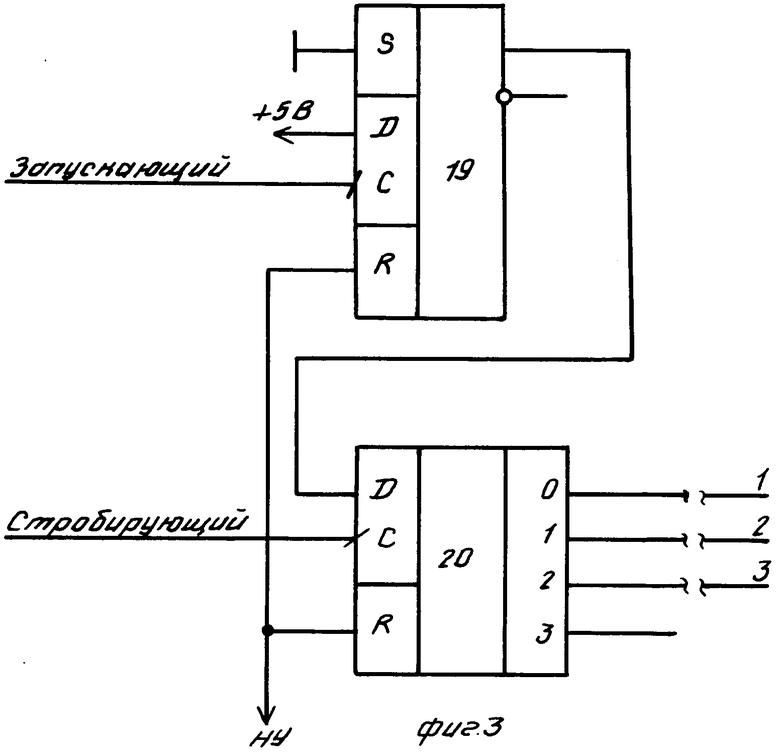

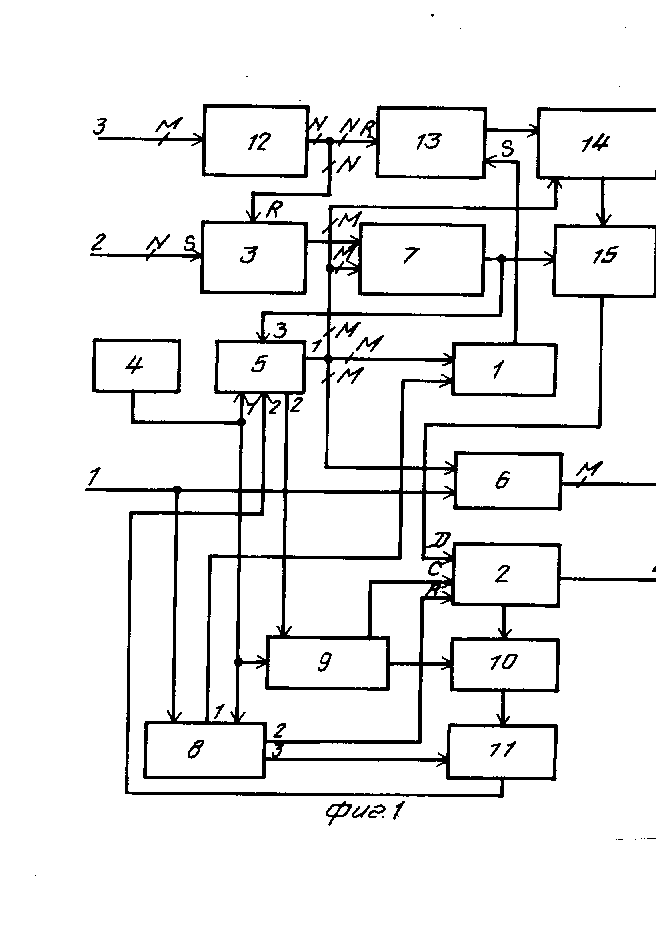

На фиг. 1 представлена блок-схема устройства приоритетных прерываний; на фиг. 2 - блок-схема счетчика; на фиг. 3 - пример распределителя импульсов.

Устройство приоритетных прерываний содержит первый дешифратор 1, триггер 2 прерываний, регистр 3 запросов прерываний, последовательно соединенные генератор 4, счетчик 5 и усилители 6 считывания, вход которых дополнительно соединен с входом дешифратора 1, при этом М выходов усилителей 6 является первым выходом устройства, а выход триггера 2 - вторым выходом устройства, вход разрешения усилителей 6 является первым входом устройства, а N входов регистра 3 является вторым входом устройства.

Кроме того, устройство содержит первый мультиплексор 7, первый распределитель 8 импульсов, последовательно соединенные второй распределитель 9 импульсов, схему И 10, схему ИЛИ 11, а также последовательно соединенные второй дешифратор 12, регистр 13 текущего прерывания, второй мультиплексор 14 и схему 15 анализа приоритета, выход которой соединен с входом D триггера 2, инверсный выход которого соединен с вторым входом схемы И 10, а синхровход - с выходом распределителя 9, запускающий вход которого соединен с вторым выходом счетчика 5, первый вход которого дополнительно соединен с синхровходами распределителей 9 и 8, запускающий вход которого соединен с управляющим входом усилителей 6, а первый, второй и третий выходы соответственно соединены со стробирующим входом дешифратора 1, с входом R триггера 2 и с вторым входом схемы ИЛИ 11, выход которой соединен с вторым входом счетчика 5, первый выход которого дополнительно соединен с адресными входами мультиплексоров 14 и 7, выход которого соединен с третьим входом счетчика 5 и с вторым входом схемы 15. Выходы дешифратора 1 соединены с входами S регистра 13, а выходы дешифратора 12 соединены с входами R регистра 3, выходы которого соединены с входами мультиплексора 7, при этом М входов дешифратора 12 является третьим входом устройства.

Счетчик 5 (см. фиг. 2) содержит двоичный счетчик 16, триггер 17 и схему И 18, прямой выход которой соединен с счетным входом счетчика 16, а инверсный выход - с синхровходом триггера 17, инверсный выход которого соединен с первым входом схемы И 18, второй вход которой является первым входом счетчика 5. Вход R счетчика 16, соединенный с входом R триггера 17, является вторым входом счетчика 5, а вход D триггера 17 - третьим входом счетчика 5. Выход счетчика 16 является первым выходом счетчика 5, а прямой выход триггера 17 - вторым выходом счетчика 5.

Устройство работает следующим образом. В зависимости от моментов времени поступления запросов на прерывание на второй вход устройства возможны 4 режима работы:

1 - отсутствие запросов;

2 - наличие одного запроса;

3 - наличие двух и более запросов, поступающих одновременно;

4 - наличие двух и более запросов, поступающих в разное время.

При отсутствии запросов на прерывание устройство работает следующим образом.

Регистры 3 и 13 (см. фиг. 1) находятся в исходном состоянии, т. е. на их выходах присутствует нулевой потенциал. Импульсы с генератора 4 изменяют состояние счетчика 5, чем достигается последовательный просмотр с помощью мультиплексоров 7 и 14 разрядов регистров 3 и 13 и их анализ схемой 15. Так как сигналы на ее входе равны, на выходе устанавливается сигнал логического нуля и триггер 2 находится в нулевом состоянии и на выходе 2 устройства сигнал отсутствует.

Допустим, что поступил запрос на прерывание RST5, т. е. сигнал логической единицы поступает на вход регистра 3 и записывается в пятый его разряд. Следовательно, на информационном входе мультиплексора 7 устанавливается положительный потенциал. Как только счетчик 5 досчитает до значения, равного номеру поступившего запроса (в рассматриваемом случае 101), открывается пятый канал мультиплексора 7. В этом случае сигнал на 2 входе схемы 15 будет превышать сигнал на 1 входе и, следовательно, на ее выходе появится логическая единица. Кроме того, сигнал с выхода мультиплексора поступает на третий вход счетчика 5, устанавливая триггер 17 (см. фиг. 2) в единичное состояние и тем самым запрещая прохождение через схему 18 счетных импульсов на счетчик 16. При этом в счетчике 16 находится значение, соответствующее уровню поступившего запроса (в рассматриваемом случае 101). Сигнал логической единицы с триггера 17 запускает распределитель 9 (см. фиг. 1). Импульс с второго его выхода устанавливает триггер 2 в состояние логической единицы, так как на входе D присутствует единичное значение, тем самым формируется сигнал запроса прерывания на втором выходе устройства. При этом сигнал с инверсного выхода триггера 2 запрещает прохождение импульса с первого выхода распределителя 9 через схему И 10. Устройство находится в режиме ожидания до поступления на первый вход его сигнала подтверждения прерывания. При этом на время наличия этого сигнала открываются усилители считывания и на первый выход устройства выдается информация о значении уровня поступившего запроса на прерывание.

Кроме того, сигнал подтверждения прерывания запускает распределитель 8. Импульс с первого его выхода с помощью дешифратора 1 записывает в регистр 13 значение текущего прерывания. Импульс с второго выхода распределителя 8 возвращает триггер 2 в исходное состояние, а импульс с третьего выхода через схему ИЛИ 11 устанавливает в исходное состояние триггер 17 и счетчик 16 (см. фиг. 2) счетчика 5 (см. фиг. 1), который начинает последовательно опрашивать каналы мультиплексоров 7 и 14. При достижении счетчиком 5 значения, равного номеру обрабатываемого прерывания (в нашем случае 101) на выходах мультиплексоров 7 и 14 сигналы будут равны и иметь значение логической единицы, поэтому на выходе схемы 15 сигнал не изменится, т. е. будет равен логическому нулю. Сигнал логической единицы с выхода мультиплексора 7 обеспечит установку триггера 17 (см. фиг. 2) в единичное состояние. При этом счетчик 5 (см. фиг. 1) прекратит изменение своего состояния и запустится распределитель 9.

Импульс с второго его выхода не изменит состояние триггера 2, так как на его входе D находится нулевой потенциал. При этом импульс с первого выхода распределителя 9 пройдет через схему И 10, а также схему ИЛИ 11 и установит счетчик 5 в исходное состояние. Таким образом, обеспечивается просмотр запросов прерывания, уровень которых превышает уровень находящегося на обработке.

Описанный цикл повторяется до тех пор, пока не завершится обработка поступившего прерывания. В этом случае номер прерывания, обработка которого завершена, поступит на третий вход устройства и сигнал с выхода дешифратора 12 установит в нулевое состояние необходимые разряды регистров 3 и 13 и при отсутствии запросов на прерывание устройство переходит в первый режим работы.

Рассмотрим работу устройства, когда до завершения обработки прерывания RST5 поступил новый с более высоким уровнем запрос на прерывание, например RST1. При этом дополнительно к пятому разряду регистра 3 устанавливается в единицу первый разряд. Счетчик 5, последовательно изменяя свое состояние, достигает значение 001. При этом на выходе схемы 15 появляется сигнал логической единицы и производится формирование сигнала "INT".

Аналогично происходит при поступлении сигнала подтверждения прерывания выдача значения уровня прерывания, занесение его в регистр 13 и приведение в исходное состояние триггера 2 и счетчика 5.

После завершения обработки прерывания RST1 сигнал с третьего входа устройства с помощью дешифратора 12 устанавливает первые разряды регистров 3 и 13 в нулевое состояние, после чего устройство продолжает следить за поступлением запросов прерывания уровнем не ниже RST5. После завершения обработки этого прерывания устройство возвращается в первоначальный режим.

В случае одновременного поступления двух и более запросов прерывания устройство обрабатывает как последовательно поступившие, поскольку просмотр регистра 3 счетчиком 5 осуществляется последовательно.

Дешифратор 1 выполнен на микросхеме 564ИД1, триггер 2 прерывания - на микросхеме 564ТМ2, регистр 3 запросов прерывания - на микросхемах 564ТР2, усилители 6 считывания - на микросхеме 564ЛН1, мультиплексор 7 - на микросхеме 564КП2, распределитель 8 импульсов (см. фиг. 3) может быть выполнен на микросхемах 19 типа 564ТМ2 и 20 типа 564ИР2, распределитель 9 аналогичен распределителю 8, схема И 10 выполнена на микросхеме 564ЛА7, схема ИЛИ 11 - на микросхеме 564ЛЕ5, дешифратор 12 аналогичен дешифратору 1, регистр 13 текущего прерывания выполнен на микросхеме 564ТР2, мультиплексор 14 аналогичен мультиплексору 7, схема 15 анализа приоритета выполнена на микросхеме 564ИП2, счетчик 16 - на микросхеме 564ИЕ10, триггер 17 - на микросхеме 564ТМ2, схема И 18 - на микросхеме 564ЛА7. (56) А. И. Березенко и др. Микропроцессорные комплекты повышенного быстродействия. М. : Радио и связь, 1981.

Б. В. Шевкопляс. Микропроцессорные структуры. Инженерные решения. Справочник - М. : Радио и связь, 1990.

Отраслевой стандарт. Микросхемы интегральные, серия 564. Руководство по применению ОСТ 11.340.907-80.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ СИСТЕМОЙ ПОСТАНОВКИ ОПТИЧЕСКИХ ПОМЕХ | 1991 |

|

RU2072087C1 |

| СПОСОБ НАВЕДЕНИЯ ЛИНИИ ВИЗИРОВАНИЯ ПРИБОРА НАБЛЮДЕНИЯ НА ИСТОЧНИК ЛАЗЕРНОГО ИЗЛУЧЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2082069C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Устройство для обработки запросов | 1984 |

|

SU1213478A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ УПРАВЛЯЮЩИХ СИГНАЛОВ С ГАЛЬВАНИЧЕСКОЙ РАЗВЯЗКОЙ | 1992 |

|

RU2097932C1 |

| Многоканальное устройство для сопряжения ЭВМ с последовательными линиями связи | 1990 |

|

SU1839259A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к области цифровых вычислительных машин и может быть использовано в устройствах мультипрограммирования. Цель - уменьшение времени реакции на прерывание. В устройство приоритетных прерываний введены второй дешифратор 12, регистр 3 запросов прерываний, два мультиплексора 7, 14, два распределителя 8, 9 импульсов, элементы И 10, ИЛИ 11, регистр 13 текущего прерывания и блок 15 анализа приоритета. 1 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-01-30—Публикация

1991-06-06—Подача