Изобретение относится к электросвязи и может использоваться в системах последовательной передачи информации по волоконно-оптическим линиям.

Целью изобретения является повышение быстродействия декодирования.

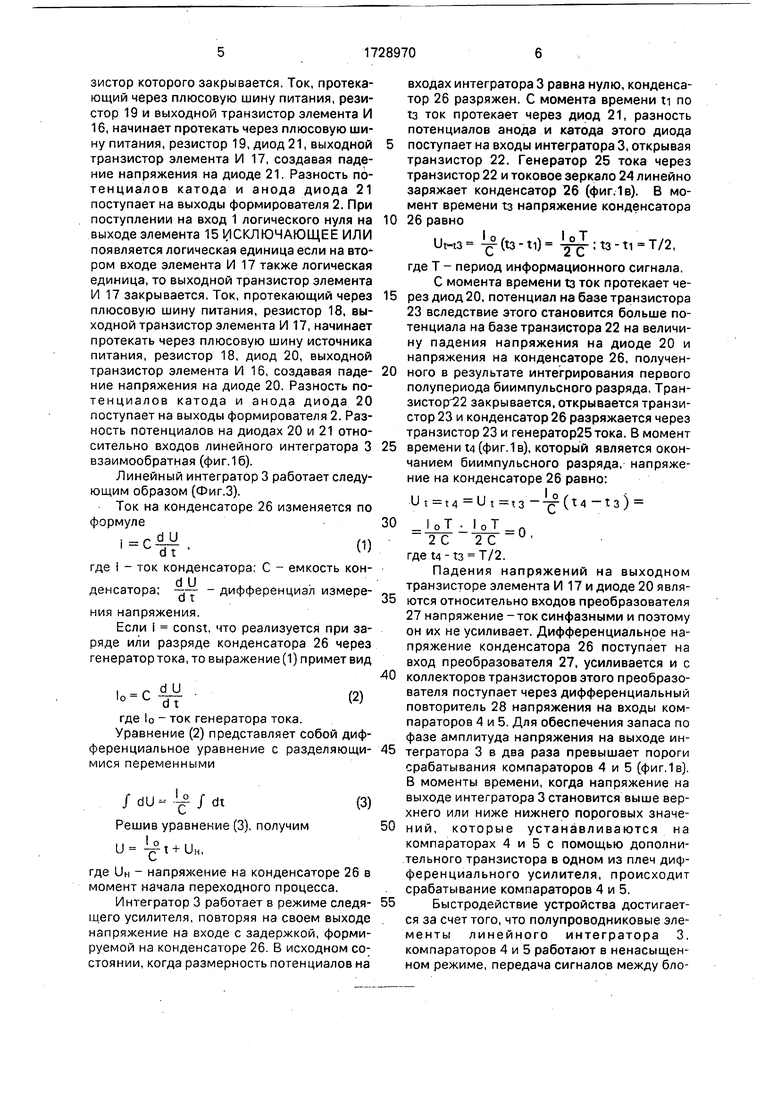

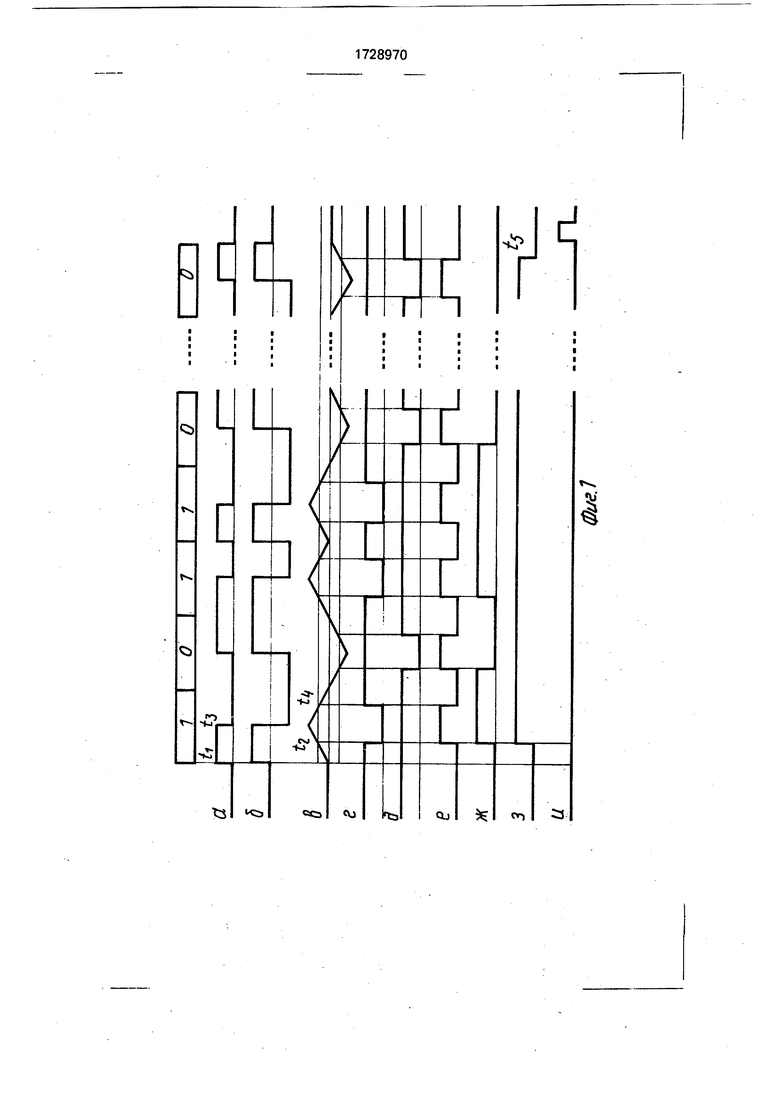

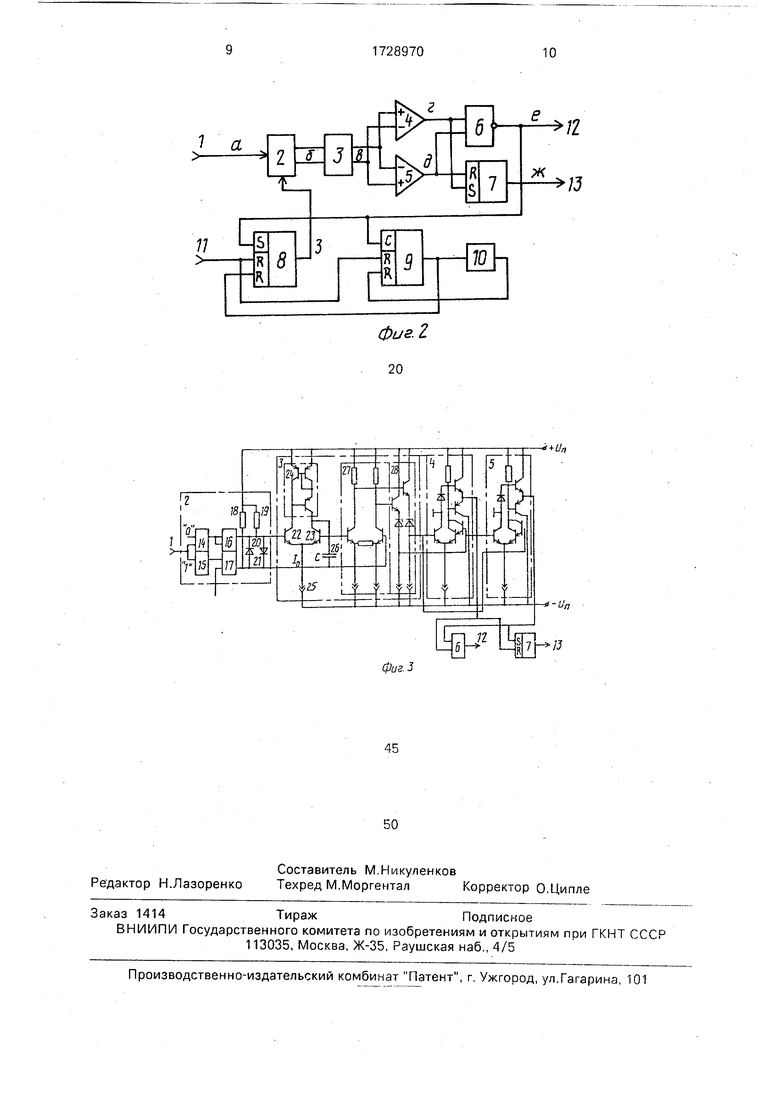

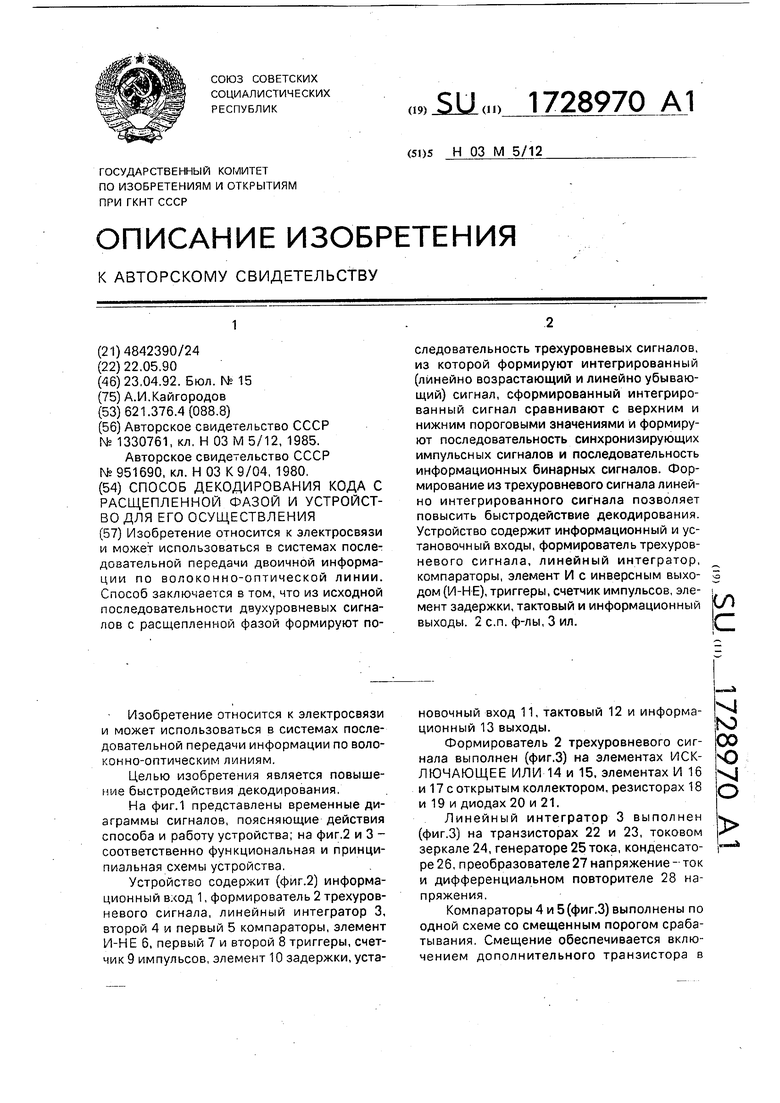

На фиг.1 представлены временные диаграммы сигналов, поясняющие действия способа и работу устройства; на фиг.2 и 3 - соответственно функциональная и принципиальная схемы устройства.

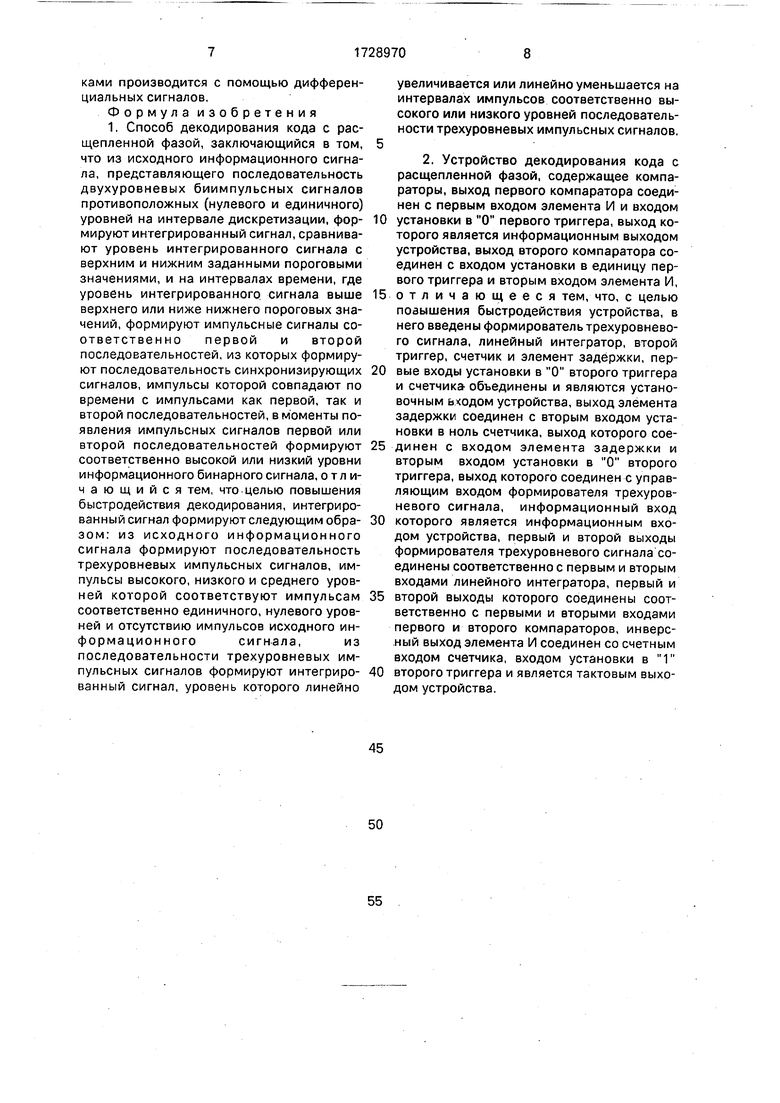

Устройство содержит (фиг.2) информационный вход 1, формирователь 2 трехуровневого сигнала, линейный интегратор 3, второй 4 и первый 5 компараторы, элемент И-НЕ 6, первый 7 и второй 8 триггеры, счетчик 9 импульсов, элемент 10 задержки, установочный вход 11, тактовый 12 и информационный 13 выходы.

Формирователь 2 трехуровневого сигнала выполнен (фиг.З) на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 15, элементах И 16 и 17 с открытым коллектором, резисторах 18 и 19 и диодах 20 и 21.

Линейный интегратор 3 выполнен (фиг.З) на транзисторах 22 и 23, токовом зеркале 24, генераторе 25 тока, конденсаторе 26, преобразователе 27 напряжение - ток и дифференциальном повторителе 28 напряжения.

Компараторы 4 и 5(фиг.З) выполнены по одной схеме со смещенным порогом срабатывания. Смещение обеспечивается включением дополнительного транзистора в

-Ч

ГО 00

о

о

одно из плеч дифференциального усилителя.

Способ декодирования кода с расщепленной фазой заключается в том, что из исходного информационного сигнала, пред- ставляющего последовательность двухуровневых биимпульсных на интервале дискретизации сигналов противоположных (нулевого и единичного) уровней (фиг. 1а) формируют интегрированный сигнал следующим образом. Из исходного информационного сигнала формируют последовательность трехуровневых импульсных сигналов (фиг. 16), импульсы высокого, низкого и среднего уровней которой соответствуют импульсам соответственно единичного, нулевого уровней и отсутствию импульсов исходного информационного сигнала. Из последовательности трехуровневых импульсных сигналов формируют интегрированный сигнал (фиг,1в), уровень которого линейно увеличивается или линейно уменьшается на интервалах импульсов соответственно высокого или низкого уровней последовательности трехуровневых импульсных сигналов, сравнивают уровень сформированного интегрированного сигнала с верхним и нижним пороговыми значениями (фиг. 1 в) и на интервалах времени, где уровень интегрированного сигнала выше верхнего или ниже нижнего пороговых значений, формируют импульсные сигналы соответственно первой или второй последовательности (фиг.1г, д), из которых формируют последовательность синхронизирующих сигналов (фиг.1е), импульсы которой совпадают с импульсами как первой, так и второй последовательностей. В моменты появления импульсных сигналов первой или второй последовательностей формируют соответственно высокий и низкий уровень информационного бинарного сигнала (фиг.1ж).

Устройство работает следующим образом.

В волоконно-оптических линиях связи для передачи информации используется двухуровневые сигналы Свет и Тьма, при этом в начале каждого кодового слова передается синхроимпульс Единица

(фиг.1а).

После включения питания на вход 11 устройства поступает импульс, который устанавливает в исходное состояние триггер 8 и счетчик 9. В исходном состоянии с входа 1 через формирователь 2 трехуровневого сигнала на линейный интегратор 3 может поступать сигнал только положительного уровня.

Биимпульсный сигнал с входа 1 поступает через формирователь 2 на интегратор 3. В момент времени t2 (фиг.1в) линейно проинтегрированный сигнал вызывает срабатывание компаратора 4, триггер 8 по переднему фронту первого импульса синхропоследовательности (фиг.1е) устанавливается в единичное состояние (фиг.1з). Сигнал логической единицы с его

0 выхода переводит формирователь 2 в состояние формирования выходного сигнала низ- кого уровня относительно входа интегратора 3 при поступлении логического нуля на вход 1 (фиг. 16). Линейный интегра5 тор 3 формирует напряжение треугольной фермы (фиг.1в). В моменты времени, когда сигналы на выходе интегратора 3 выше верхнего или ниже нижнего пороговых значений,формируютсяимпульсы

0 соответственно первой (фиг.1г) или второй (фиг.1д) последовательности, которые на элементе И-НЕ 6 складывается по ИЛИ и образуют выходную последовательность синхронизирующих сигналов (фиг.1е), по5 ступающих на выход 12 устройства, а также на вход счетчика 9, который считает импульсы этой последовательности и в момент времени ts по заднему фронту последнего импульса устанавливает триггер 8 в исход0 ное нулевое состояние (фиг.1з). С этого момента формирователь 2 перестает формировать нижний уровень информационного сигнала относительно входов линейного интегратора 3. В моменты появления

5 импульсных сигналов первой последовательности (фиг.1г) триггер 7 формирует высокий логический уровень, а в моменты появления сигналов второй последовательности (фиг,1д) - низкий логический уровень

0 выходного информационного бинарного сигнала, который поступает на выход 13 устройства. Элемент 10 задержки служит для того, чтобы установить счетчик 9 в исходное нулевое состояние после установки в исход5 ное состояние триггера 8 (фиг.1и).

Формирователь 2 трехуровневого сигнала работает следующим образом (фиг.З). В исходном состоянии на входе 1 и втором входе элемента И17 установлен логиче0 ский ноль, на выходах элементов И 16 и 17 сформирован низкий уровень. Так как резисторы 18,19 равны по номиналу, а элементы И 16 и 17 изготовлены в одном кристалле полупроводника, то падения напряжений на

5 выходных транзисторах элементов И 16 и 17 равны и разность потенциалов между выходами формирователя 2 также равна нулю. Сигнал логической единицы с входа 1 поступает через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 на входы элемента 1/116, выходной транзистор которого закрывается. Ток, протекающий через плюсовую шину питания, резистор 19 и выходной транзистор элемента И 16, начинает протекать через плюсовую шину питания, резистор 19, диод 21, выходной транзистор элемента И 17, создавая падение напряжения на диоде 21. Разность потенциалов катода и анода диода 21 поступает на выходы формирователя 2. При поступлении на вход 1 логического нуля на выходе элемента 15 ИСКЛЮЧАЮЩЕЕ ИЛИ появляется логическая единица если на втором входе элемента И 17 также логическая единица, то выходной транзистор элемента И 17 закрывается. Ток, протекающий через плюсовую шину питания, резистор 18, выходной транзистор элемента И 17, начинает протекать через плюсовую шину источника питания, резистор 18, диод 20, выходной транзистор элемента И 16, создавая падение напряжения на диоде 20. Разность потенциалов катода и анода диода 20 поступает на выходы формирователя 2. Разность потенциалов на диодах 20 и 21 относительно входов линейного интегратора 3 взаимообратная (фиг. 16).

Линейный интегратор 3 работает следующим образом (Фиг.З).

Ток на конденсаторе 26 изменяется по формуле

С Тгде i - ток конденсатора; С - емкость конденсатора; -г-- - дифференциал измерения напряжения.

Если i const, что реализуется при заряде или разряде конденсатора 26 через генератор тока, то выражение (1) примет вид

С

d U

d t

где lo - ток генератора тока. Уравнение (2) представляет собой дифференциальное уравнение с разделяющимися переменными

/dU-- /dt Решив уравнение (3), получим U + UH,

где DH - напряжение на конденсаторе 26 в момент начала переходного процесса.

Интегратор 3 работает в режиме следящего усилителя, повторяя на своем выходе напряжение на входе с задержкой, формируемой на конденсаторе 26. В исходном со стоянии,когда размерность потенциалов на

входах интегратора 3 равна нулю, конденсатор 26 разряжен. С момента времени ti по 1з ток протекает через диод 21, разность потенциалов анода и катода этого диода

поступает на входы интегратора 3, открывая транзистор 22. Генератор 25 тока через транзистор 22 и токовое зеркало 24 линейно заряжает конденсатор 26 (фиг.1в). В момент времени гз напряжение конденсатора

26 равно

Ut-t3- (t3-ti) b l;t3-ti T/2,

где Т - период информационного сигнала. С момента времени t3 ток протекает через диод 20, потенциал на базе транзистора 23 вследствие этого становится больше потенциала на базе транзистора 22 на величину падения напряжения на диоде 20 и напряжения на конденсаторе 26, полученного в результате интегрирования первого полупериода биимпульсного разряда. Транзистор закрывается, открывается транзистор 23 и конденсатор 26 разряжается через транзистор 23 и генератор25тока. В момент

времени t4 (фиг.1в), который является окончанием биимпульсного разряда, напряжение на конденсаторе 26 равно:

40

45

50

55

U

30

35

t t4 Ut t3--7(t4-l3)

о

I о Т . I о Т

0

2С 2 С где t4-ta T/2.

Падения напряжений на выходном транзисторе элемента И 17 и диоде 20 являются относительно входов преобразователя 27 напряжение -ток синфазными и поэтому он их не усиливает. Дифференциальное напряжение конденсатора 26 поступает на вход преобразователя 27, усиливается и с коллекторов транзисторов этого преобразователя поступает через дифференциальный повторитель 28 напряжения на входы компараторов 4 и 5. Для обеспечения запаса по фазе амплитуда напряжения на выходе интегратора 3 в два раза превышает пороги срабатывания компараторов 4 и 5 (фиг.1в). В моменты времени, когда напряжение на выходе интегратора 3 становится выше верхнего или ниже нижнего пороговых значений, которые устанавливаются на компараторах 4 и 5 с помощью дополнительного транзистора в одном из плеч дифференциального усилителя, происходит срабатывание компараторов 4 и 5.

Быстродействие устройства достигается за счет того, что полупроводниковые эле- менты линейного интегратора 3. компараторов 4 и 5 работают в ненасыщенном режиме, передача сигналов между блоками производится с помощью дифференциальных сигналов,

Формула изобретения 1. Способ декодирования кода с расщепленной фазой, заключающийся в том, что из исходного информационного сигнала, представляющего последовательность двухуровневых биимпульсных сигналов противоположных (нулевого и единичного) уровней на интервале дискретизации, фор- мируют интегрированный сигнал, сравнивают уровень интегрированного сигнала с верхним и нижним заданными пороговыми значениями, и на интервалах времени, где уровень интегрированного, сигнала выше верхнего или ниже нижнего пороговых значений, формируют импульсные сигналы соответственно первой и второй последовательностей, из которых формируют последовательность синхронизирующих сигналов, импульсы которой совпадают по времени с импульсами как первой, так и второй последовательностей, в моменты появления импульсных сигналов первой или второй последовательностей формируют соответственно высокой или низкий уровни информационного бинарного сигнала, отличающийся тем, что целью повышения быстродействия декодирования, интегрированный сигнал формируют следующим обра- зом: из исходного информационного сигнала формируют последовательность трехуровневых импульсных сигналов, импульсы высокого, низкого и среднего уровней которой соответствуют импульсам соответственно единичного, нулевого уровней и отсутствию импульсов исходного информационногосигнала,из последовательности трехуровневых импульсных сигналов формируют интегриро- ванный сигнал, уровень которого линейно

увеличивается или линейно уменьшается на интервалах импульсов соответственно высокого или низкого уровней последовательности трехуровневых импульсных сигналов,

2. Устройство декодирования кода с расщепленной фазой, содержащее компараторы, выход первого компаратора соединен с первым входом элемента И и входом установки в О первого триггера, выход которого является информационным выходом устройства, выход второго компаратора соединен с входом установки в единицу первого триггера и вторым входом элемента И, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены формирователь трехуровневого сигнала, линейный интегратор, второй триггер, счетчик и элемент задержки, первые входы установки в О второго триггера и счетчика объединены и являются установочным входом устройства, выход элемента задержки соединен с вторым входом установки в ноль счетчика, выход которого соединен с входом элемента задержки и вторым входом установки в О второго триггера, выход которого соединен с управляющим входом формирователя трехуровневого сигнала, информационный вход которого является информационным входом устройства, первый и второй выходы формирователя трехуровневого сигнала соединены соответственно с первым и вторым входами линейного интегратора, первый и второй выходы которого соединены соответственно с первыми и вторыми входами первого и второго компараторов, инверс- .ный выход элемента И соединен со счетным входом счетчика, входом установки в 1 второго триггера и является тактовым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Генератор синусоидальных колебаний | 1989 |

|

SU1786634A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1431074A1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| Устройство для ввода информации | 1988 |

|

SU1529210A1 |

| Устройство для проведения телеигр | 1982 |

|

SU1052247A1 |

| Стабилизирующий преобразователь напряжения постоянного тока | 1988 |

|

SU1646027A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Устройство для приема информации | 1987 |

|

SU1444955A1 |

| Импульсно-фазовый детектор | 1987 |

|

SU1552369A1 |

Изобретение относится к электросвязи и может использоваться в системах последовательной передачи двоичной информации по волоконно-оптической линии. Способ заключается в том, что из исходной последовательности двухуровневых сигналов с расщепленной фазой формируют последовательность трехуровневых сигналов, из которой формируют интегрированный (линейно возрастающий и линейно убывающий) сигнал, сформированный интегрированный сигнал сравнивают с верхним и нижним пороговыми значениями и формируют последовательность синхронизирующих импульсных сигналов и последовательность информационных бинарных сигналов. Формирование из трехуровневого сигнала линейно интегрированного сигнала позволяет повысить быстродействие декодирования. Устройство содержит информационный и установочный входы, формирователь трехуровневого сигнала, линейный интегратор, компараторы, элемент И с инверсным выходом (И-НЕ), триггеры, счетчик импульсов, элемент задержки, тактовый и информационный выходы. 2 с.п. ф-лы, 3 ил.

| Способ демодуляции биполярного фазоманипулированного сигнала | 1985 |

|

SU1330761A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Демодулятор импульсного сигнала,модулированного методом расщепленной фазы | 1980 |

|

SU951690A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-23—Публикация

1990-05-22—Подача