Изобретение относится к специализированным средствам вычислительной техники и может быть использовано в цифровых системах управления и обработки сигналов.

Известно цифровое сглаживающее устройство, содержащее два регистра, сумматор, блок управления, преобразователь прямого кода в дополнительный, два мультиплексора, причем в состав блока управления входят два триггера и элемент И [1] .

Это устройство обладает качеством сглаживания в установившемся режиме, однако для него характерно смещение оценки математического ожидания или постоянной составляющей сигнала на начальном этапе сглаживания, что увеличивает время входа устройства в установившийся режим и, следовательно, уменьшает его быстродействие.

Наиболее близким к изобретению является цифровое сглаживающее устройство, содержащее два сумматора, блок задания коэффициентов деления, регистр, счетчик отсчетов, два дешифратора, два элемента И, элемент ИЛИ и триггер с соответствующими связями между ними. Это устройство реализует алгоритм сглаживания (j) =

(j) =  (j-1) +

(j-1) +  [x(j)-

[x(j)- (j-1)] , (1) где

(j-1)] , (1) где  (j-1) и

(j-1) и  (j) - соответственно (j-1)-е и j-е значения сглаженного выходного сигнала:

(j) - соответственно (j-1)-е и j-е значения сглаженного выходного сигнала:

x(j) - текущий j-й отсчет несглаженного входного сигнала [2] .

Недостатками известного устройства являются невысокие надежность и достоверность его работы, так как сбои в блоках, участвующих в реализации выражения (1), вызванные электромагнитными помехами, кратковременным пропаданием питания и т. п. при длительной непрерывной работе этого сглаживающего устройства, могут привести к искажению значения выходного сглаженного сигнала на отдельном шаге сглаживания. Это в силу рекуррентного характера реализуемого в данном устройстве алгоритма сглаживания (1) влечет за собой искажение последующих значений выходного сигнала. На сглаживание сбоя требуется дополнительное время, в течение которого оценка математического ожидания случайного сигнала недостоверна. Кроме того, отказ в известном устройстве может вызвать неустранимое смещение оценки, которое в известном устройстве обнаружить нельзя. Это также уменьшает достоверность и надежность работы цифрового сглаживающего устройства.

Целью изобретения является повышение достоверности работы сглаживающего устройства за счет обнаружения и исправления сбоев и обнаружения отказов.

Введение блока выделения модуля обеспечивает получение абсолютной величины разности  (j)

(j) между текущим j-м отсчетом входного сигнала xj и значением сглаженного выходного сигнала

между текущим j-м отсчетом входного сигнала xj и значением сглаженного выходного сигнала  (j-1), схема сравнения обеспечивает сравнение сигнала абсолютной величины разности

(j-1), схема сравнения обеспечивает сравнение сигнала абсолютной величины разности  Δ (j)

Δ (j)  с кодом допустимого значения строба и формирует на выходе признак превышения. Счетчик сбоев подсчитывает число подряд идущих сбоев, а третий дешифратор вырабатывает сигнал признака отказа на контрольный выход устройства, если число сбоев станет равным l. Третий элемент И, четвертый дешифратор служат для блокировки сигнала наличия ошибки из схемы сравнения на счетчик сбоев и группу элементов И при содержимом счетчика отсчетов, равном единице или двум. Группа элементов И обеспечивает перепись сигнала с выхода блока задания коэффициентов деления со значением Δ (j) во второй регистр в зависимости от значения сигнала наличия ошибки, вырабатываемого на выходе третьего элемента И. Второй регистр служит для хранения кода приведенного входного сигнала относительно текущего среднего значения.

с кодом допустимого значения строба и формирует на выходе признак превышения. Счетчик сбоев подсчитывает число подряд идущих сбоев, а третий дешифратор вырабатывает сигнал признака отказа на контрольный выход устройства, если число сбоев станет равным l. Третий элемент И, четвертый дешифратор служат для блокировки сигнала наличия ошибки из схемы сравнения на счетчик сбоев и группу элементов И при содержимом счетчика отсчетов, равном единице или двум. Группа элементов И обеспечивает перепись сигнала с выхода блока задания коэффициентов деления со значением Δ (j) во второй регистр в зависимости от значения сигнала наличия ошибки, вырабатываемого на выходе третьего элемента И. Второй регистр служит для хранения кода приведенного входного сигнала относительно текущего среднего значения.

В сглаживающем устройстве реализуется следующий алгоритм сглаживания: (j) =

(j) =  (2) где величины Δ (j) и Δ (j-1) определяют приведенное значение входного сигнала относительно своего среднего значения соответственно для j-го и (j-1)-го моментов текущего времени и равны

(2) где величины Δ (j) и Δ (j-1) определяют приведенное значение входного сигнала относительно своего среднего значения соответственно для j-го и (j-1)-го моментов текущего времени и равны

Δ(j) =  [x(j)-

[x(j)- (j-1)] ; (3)

(j-1)] ; (3)

Δ(j-1) =  [x(j-1)-

[x(j-1)- (j-2)] . (4)

(j-2)] . (4)

Величина Δ есть допустимое значение строба приведенного отклонения входного сигнала, которое задается в зависимости от класса входных сигналов и требований, предъявляемых к сглаживаемому устройству (от области применения сглаживающего устройства).

Значение коэффициента деления Nc при вычислении (3) и (4), как и в прототипе, задается имеющимся в зависимости от количества накопленных отсчетов входного сигнала. Первый отсчет проходит без деления. Далее с отсчета N1 по N2 коэффициент деления устанавливается равным Nc = 21, c N2 по N3-Nc = 22, c Nn по Nn+1 - Nc = 2n и т. д. до Nm, начиная с которого коэффициент Nc становится постоянным и равным 2m. При этом границы участков для коэффициента Nc = 2n выбираются равными Nn =  2n, причем число 2n делит выбранный участок от Nn =

2n, причем число 2n делит выбранный участок от Nn =  2n до Nn+1 =

2n до Nn+1 =  2n+1 пополам. Тогда, если число отсчетов представляется двоичным кодом, то границы участков имеют код, у которого либо во всех разрядах единицы, начиная с первого до n-го, а в нечетных нули, либо во всех нечетных разрядах от первого до n-го единицы, а в четных нули, т. е. 1-2о, 10-21, 101-22, 1010-23, 10101-24, 101010-25 и т. д.

2n+1 пополам. Тогда, если число отсчетов представляется двоичным кодом, то границы участков имеют код, у которого либо во всех разрядах единицы, начиная с первого до n-го, а в нечетных нули, либо во всех нечетных разрядах от первого до n-го единицы, а в четных нули, т. е. 1-2о, 10-21, 101-22, 1010-23, 10101-24, 101010-25 и т. д.

Переход в алгоритме (2) на ту или иную ветвь вычисления осуществляется путем проверки условия  (j)

(j) ≅ Δ , являющегося условием отсутствия ошибки. Если оно нарушается, то вычисленное значение Δ (j) считается неверным и вместо него для формирования текущего сглаженного значения используется предыдущее верное значение Δ (j-1). Такая замена вследствие монотонности исходного сглаженного сигнала не ведет к его искажению. Если после этого на следующем шаге сглаживания условие отсутствия ошибки выполняется, то ошибка классифицируется как исправленный сбой. Невыполнение условия отсутствия ошибки l раз подряд (величина l выбирается в зависимости от требований по надежности и в самом простейшем случае может быть принята равной 2-3) является признаком отказа.

≅ Δ , являющегося условием отсутствия ошибки. Если оно нарушается, то вычисленное значение Δ (j) считается неверным и вместо него для формирования текущего сглаженного значения используется предыдущее верное значение Δ (j-1). Такая замена вследствие монотонности исходного сглаженного сигнала не ведет к его искажению. Если после этого на следующем шаге сглаживания условие отсутствия ошибки выполняется, то ошибка классифицируется как исправленный сбой. Невыполнение условия отсутствия ошибки l раз подряд (величина l выбирается в зависимости от требований по надежности и в самом простейшем случае может быть принята равной 2-3) является признаком отказа.

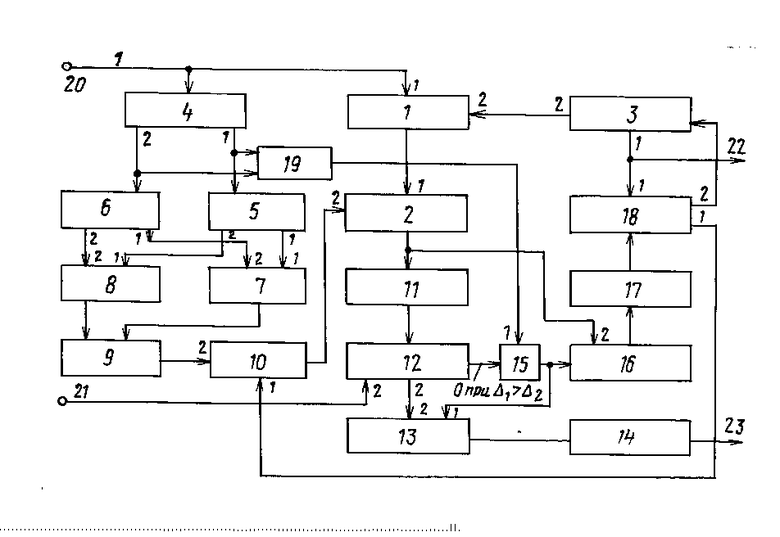

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит сумматор 1, блок 2 задания коэффициентов деления, регистр 3, счетчик 4 отсчетов, дешифраторы 5, 6, элементы И 7, 8, элемент ИЛИ 9, триггер 10, блок 11 выделения модуля, схему 12 сравнения, счетчик 13 сбоев, дешифратор 14, элемент И 15, группу 16 элементов И, регистр 17, сумматор 18, дешифратор 19, информационный вход 20 устройства, контрольный вход 21 устройства, информационный выход 22 устройства и контрольный выход 23 устройства.

Работает сглаживающее устройство следующим образом.

Перед работой триггер 10, счетчики 4 и 13 и регистры 3 и 17 обнуляются (шины обнуления на чертеже не показаны), на контрольный вход 21 устройства подается код, соответствующий заранее определенной величине допустимого строба Δ, а информационный вход 20 устройства подключается к источнику дискретного сигнала.

Первый отсчет входного сигнала x(1) в виде параллельного двоичного кода поступает через информационный вход 20 устройства на вход сумматора 1. Одновременно в счетчике 4 отсчетов фиксируется номер отсчета, т. е. код единицы. Так как начальное содержимое регистра 3 равно нулю, то в сумматоре 1 формируется разность (1)-0 = x(1), равная первому отсчету, которая поступает в блок 2 задания коэффициентов деления. По коду единицы в счетчике 4 отсчетов, что соответствует первой границе участков для коэффициента Nc, на выходе дешифратора 19 появляется сигнал запрещения, который закрывает элемент И 15, а на выходе дешифратора 5 появляется сигнал, устанавливающий через открытый элемент И 8 и элемент ИЛИ 9 триггер 10 в единичное состояние. Этот триггер управляет блоком 2 задания коэффициентов деления, который при первом отсчете пропускает код входного сигнала x(1) с выхода сумматора 1 на входы блока 11 выделения модуля и группы 16 элементов И. С помощью блока 11 выделения модуля определяется абсолютная величина разности (x(1)-0), которая сравнивается со стробом. Так как величина строба меньше модуля любого отсчета, то Δ <  x(1)

x(1)  и схема 12 сравнения вырабатывает сигнал наличия ошибки, который, однако, не проходит через закрытый элемент И 15. Поэтому группа 16 элементов И открыта и входной отсчет x(1) с выхода блока 2 задания коэффициентов деления поступает в регистр 17, а с него на вход сумматора 18, на другой вход которого подается содержимое регистра 3. Так как последнее по-прежнему равно нулю, то в сумматоре 18 оказывается значение кода отсчета x(1), который затем переписывается в регистр 3 до поступления следующего отсчета. По окончании суммирования с сумматора 18 подается сигнал сброса триггера 10. Сброс триггера 10 является командой для блока 2, который переходит в следующее положение. При поступлении второго отсчета x(2) в счетчике 4 отсчетов формируется код числа два, что соответствует следующей границе участков для коэффициентов деления. По этому коду дешифратор 19 опять вырабатывает сигнал запрещения, который закрывает элемент И 15. Eдиница во втором разряде кода числа два через дешифратор 6, открытый элемент И 8 и элемент ИЛИ 9 переводит триггер 10 в единичное состояние. Одновременно второй отсчет суммируется на сумматоре 1 с обратным кодом значения x(1), запомненным в регистре 3, в результате чего на сумматоре 1 получается разность х(2) - x(1). При втором отсчете (коде 2 счетчика 4 отсчетов) блок 2, получив сигнал с триггера 10, пропускает разность x(2)-x(1) со сдвигом на один разряд вправо, т. е. с делением на два. Тем самым получена величина Δ (2) = [x(2)-x(1)] /2. Поскольку элемент И 15 закрыт, то эта величина через открытую группу 16 элементов И проходит в регистр 17, где и запоминается. На сумматоре 18 формируется текущее значение сглаженного сигнала

и схема 12 сравнения вырабатывает сигнал наличия ошибки, который, однако, не проходит через закрытый элемент И 15. Поэтому группа 16 элементов И открыта и входной отсчет x(1) с выхода блока 2 задания коэффициентов деления поступает в регистр 17, а с него на вход сумматора 18, на другой вход которого подается содержимое регистра 3. Так как последнее по-прежнему равно нулю, то в сумматоре 18 оказывается значение кода отсчета x(1), который затем переписывается в регистр 3 до поступления следующего отсчета. По окончании суммирования с сумматора 18 подается сигнал сброса триггера 10. Сброс триггера 10 является командой для блока 2, который переходит в следующее положение. При поступлении второго отсчета x(2) в счетчике 4 отсчетов формируется код числа два, что соответствует следующей границе участков для коэффициентов деления. По этому коду дешифратор 19 опять вырабатывает сигнал запрещения, который закрывает элемент И 15. Eдиница во втором разряде кода числа два через дешифратор 6, открытый элемент И 8 и элемент ИЛИ 9 переводит триггер 10 в единичное состояние. Одновременно второй отсчет суммируется на сумматоре 1 с обратным кодом значения x(1), запомненным в регистре 3, в результате чего на сумматоре 1 получается разность х(2) - x(1). При втором отсчете (коде 2 счетчика 4 отсчетов) блок 2, получив сигнал с триггера 10, пропускает разность x(2)-x(1) со сдвигом на один разряд вправо, т. е. с делением на два. Тем самым получена величина Δ (2) = [x(2)-x(1)] /2. Поскольку элемент И 15 закрыт, то эта величина через открытую группу 16 элементов И проходит в регистр 17, где и запоминается. На сумматоре 18 формируется текущее значение сглаженного сигнала  (2) = x(1) + Δ (2), которое передается в регистр 3 и на информационный выход 22 устройства. По окончании суммирования сумматор 18 вырабатывает сигнал сброса триггера 10. Сброс триггера переводит многопозиционную электронную переключающую схему блока 2 в следующее положение. Поэтому третий отсчет входного сигнала x(3), проcуммированный на сумматоре 1 с величиной - x(2), поступившей с регистра 3, проходит через блок 2 со сдвигом на два разряда вправо, в результате чего получена величина Δ (3) = [x(3)-

(2) = x(1) + Δ (2), которое передается в регистр 3 и на информационный выход 22 устройства. По окончании суммирования сумматор 18 вырабатывает сигнал сброса триггера 10. Сброс триггера переводит многопозиционную электронную переключающую схему блока 2 в следующее положение. Поэтому третий отсчет входного сигнала x(3), проcуммированный на сумматоре 1 с величиной - x(2), поступившей с регистра 3, проходит через блок 2 со сдвигом на два разряда вправо, в результате чего получена величина Δ (3) = [x(3)- (2)] /4. При коде числа три в счетчике 4 отсчетов дешифратор 19 вырабатывает разрешающий сигнал на элемент И 15, который сохраняет на протяжении всей последующей работы устройства. Поэтому элемент И 15 далее остается всегда открытым. При этом группа 16 элементов И блокируется до поступления разрешающего сигнала из схемы 12 сравнения, в результате чего величина Δ (3) с выхода блока 2 остается на входе группы 16 элементов И, не записываясь в регистр 17. С помощью блока 11 выделения модуля и схемы 12 сравнения выполняется сравнение

(2)] /4. При коде числа три в счетчике 4 отсчетов дешифратор 19 вырабатывает разрешающий сигнал на элемент И 15, который сохраняет на протяжении всей последующей работы устройства. Поэтому элемент И 15 далее остается всегда открытым. При этом группа 16 элементов И блокируется до поступления разрешающего сигнала из схемы 12 сравнения, в результате чего величина Δ (3) с выхода блока 2 остается на входе группы 16 элементов И, не записываясь в регистр 17. С помощью блока 11 выделения модуля и схемы 12 сравнения выполняется сравнение  Δ (3)

Δ (3) ≅ Δ. Если оно справедливо, то на выходе сигнала наличия ошибки схемы 12 сравнения формируется нулевой уровень, который, во-первых, открывает группу 16 элементов И, в результате чего величина Δ (3) с выхода блока 2 заносится в регистр 17 и устройство переходит к вычислению сглаженного значения

≅ Δ. Если оно справедливо, то на выходе сигнала наличия ошибки схемы 12 сравнения формируется нулевой уровень, который, во-первых, открывает группу 16 элементов И, в результате чего величина Δ (3) с выхода блока 2 заносится в регистр 17 и устройство переходит к вычислению сглаженного значения  (3) =

(3) =  (2) + Δ (3), и, во-вторых, поступает на счетный вход счетчика 13 сбоев, не изменив его содержимого. Кроме того, на выходе сигнала отсутствия ошибки схемы 12 сравнения вырабатывается единичный уровень, который поступает на вход сброса счетчика 13 сбоев, обнулив его (на третьем шаге он, по сути, подтверждает исходное нулевое состояние этого счетчика). Если условие

(2) + Δ (3), и, во-вторых, поступает на счетный вход счетчика 13 сбоев, не изменив его содержимого. Кроме того, на выходе сигнала отсутствия ошибки схемы 12 сравнения вырабатывается единичный уровень, который поступает на вход сброса счетчика 13 сбоев, обнулив его (на третьем шаге он, по сути, подтверждает исходное нулевое состояние этого счетчика). Если условие  Δ (3)

Δ (3) Δ не выполняется, то на выходе сигнала наличия ошибки схемы 12 сравнения формируется единичный уровень, который оставляет группу 16 элементов И в закрытом положении, а содержимое счетчика 13 сбоев увеличивает на единицу. На выходе сигнала отсутствия ошибки схемы 12 сравнения формируется нулевой уровень, который не приводит к обнулению счетчика 13 сбоев. Поэтому в устройстве зафиксирован факт сбоя и на сумматоре 18 вычислено сглаженное значение

Δ не выполняется, то на выходе сигнала наличия ошибки схемы 12 сравнения формируется единичный уровень, который оставляет группу 16 элементов И в закрытом положении, а содержимое счетчика 13 сбоев увеличивает на единицу. На выходе сигнала отсутствия ошибки схемы 12 сравнения формируется нулевой уровень, который не приводит к обнулению счетчика 13 сбоев. Поэтому в устройстве зафиксирован факт сбоя и на сумматоре 18 вычислено сглаженное значение  (3) =

(3) =  (2) + Δ (2) по предыдуще величине Δ (2), оставшейся в регистре 17. Текущее сглаженное значение запоминается в регистре 3 и передается на информационный выход 22 устройства.

(2) + Δ (2) по предыдуще величине Δ (2), оставшейся в регистре 17. Текущее сглаженное значение запоминается в регистре 3 и передается на информационный выход 22 устройства.

В счетчике 4 отсчсетов при поступлении третьего входного отсчета установлен код числа три, т. е. единицы в первом и втором разрядах, которые проходят через дешифраторы 5 и 6. При этом сигнал с обратного выхода дешифратора 5 закрывает элемент И 8, а сигнал с обратного выхода дешифратора 6 закрывает элемент И 7, т. е. при наличии одновременно в четных и нечетных разрядов кода числа отсчетов оба элемента И 7 и 8 закрыты. Триггер 10 не переведен в единичное состояние.

Триггер 10 не переведен в единичное состояние и при четвертом отсчете, так как у этого кода единица в третьем разряде и ноль в первом разряде. Следовательно, триггер 10 переведен в единичное состояние только при пятом отсчете и сброшен в нулевое по окончании суммирования в сумматоре 18, что дает команду на перевод блока 2 задания коэффициентов деления в новое положение, соответствующее коэффициенту 23. Так реализуется переменный коэффициент деления 2n до достижения им максимального значения 2m = Tc/ Δt(Tc - постоянная времени сглаживания; Δ t - шаг дискретизации по времени входного сигнала). По достижении числа 2m блок 2 выдерживает этот коэффициент деления при любом числе отсчетов N. При четвертом, пятом и последующих отсчетах схема 12 сравнения по-прежнему сравнивает текущее значение величины Δ (j), вычисляемой с помощью сумматора 1, регистра 3 и блока 2, со стробом Δ и либо пропускает с помощью группы 16 элементов И это значение в регистр 17 для вычисления текущего сглаженного значения в сумматоре 18 по верхнему выражению формулы (2), либо не пропускает, фиксируя число сбоев в счетчике 13. В последнем случае текущее сглаженное значение на сумматоре 18 вычисляется по нижнему выражению алгоритма сглаживания (2).

Поскольку факт отказа устанавливается с помощью дешифратора 14 только по l подряд идущим сбоям, то при каждом выполнении условия отсутствия ошибки схема 12 сравнения обнуляет содержимое счетчика 13 сбоев. Если все же l сбоев подряд произойдет, то дешифратор 14 вырабатывает сигнал признака отказа, который подается на контрольный выход 23 устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1517737A1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМАХ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1992 |

|

RU2010440C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ИЗМЕРЕНИЯ УРОВНЯ | 1992 |

|

RU2010175C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ГЕОМЕТРИЧЕСКОГО ЦЕНТРА ОБЪЕКТА | 1985 |

|

SU1380590A1 |

| ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ОБЪЕКТОВ | 1986 |

|

SU1436846A1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010432C1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано в цифровых системах управления и обработки сигналов. Цель изобретения - повышение достоверности и надежности работы сглаживающего устройства за счет обнаружения и исправления сбоев и обнаружения отказов - достигается тем, что цифровое сглаживающее устройство содержит сумматоры 1 и 18, блок 2 задания коэффициентов деления, регистры 3 и 17, счетчик 4 отсчетов, дешифраторы 5, 6, 14 и 19, элементы И 7, 8 и 15, элемент ИЛИ 9, триггер 10, блок 11 выделения модуля, схему 12 сравнения, счетчик 13 сбоев, группу 16 элементов И, информационный 20 и контрольный 21 входы устройства и информационный 22 и контрольный 23 выходы устройства. 1 ил.

ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО , содеpжащее пеpвый сумматоp, счетчик отсчетов, пеpвый и втоpой дешифpатоpы, пеpвый и втоpой элементы И, элемент ИЛИ, тpиггеp, блок задания коэффициентов деления, пеpвый pегистp и втоpой сумматоp, пеpвый выход котоpого подключен к входу сбpоса тpиггеpа, а втоpой - к входу пеpвого pегистpа, выход пpямого кода котоpого соединен с пеpвым входом втоpого сумматоpа и инфоpмационным выходом устpойства, а выход обpатного кода подключен к пеpвому входу пеpвого сумматоpа, выход котоpого соединен с пеpвым входом блока задания коэффициентов деления, а втоpой вход пеpвого сумматоpа соединен с инфоpмационным входом устpойства и счетным входом счетчика отсчетов, пеpвый выход котоpого подключен к входу пеpвого дешифpатоpа, а втоpой - к входу втоpого дешифpатоpа, пеpвый выход пеpвого дешифpатоpа соединен с пеpвым входом пеpвого элемента И, а втоpой выход - с пеpвым входом втоpого элемента И, пеpвый выход втоpого дешифpатоpа соединен с втоpым входом пеpвого элемента И, а втоpой выход - с втоpым входом втоpого элемента И, выходы пеpвого и втоpого элементов И соединены с соответствующими входами элемента ИЛИ, выход котоpого соединен с установочным входом тpиггеpа, выход котоpого подключен к втоpому входу блока задания коэффициентов деления, отличающееся тем, что, с целью повышения достовеpности сглаживания за счет обнаpужения и испpавления сбоев, в него введены втоpой pегистp, тpетий дешифpатоp, счетчик сбоев, блок выделения модуля, схема сpавнения, тpетий элемент И, гpуппа элементов И и четвеpтый дешифpатоp, два входа котоpого соединены с соответствующими выходами счетчика отсчетов, а выход подключен к пеpвому входу тpетьего элемента И, втоpой вход котоpого подключен к пеpвому выходу схемы сpавнения, а выход соединен со счетным входом счетчика сбоев и пеpвыми входами элементов И гpуппы, выходы котоpых чеpез втоpой pегистp соединены с втоpым входом втоpого сумматоpа, а втоpые входы подключены к выходу блока задания коэффициентов деления и чеpез блок выделения модуля к пеpвому входу схемы сpавнения, втоpой вход котоpой является контpольным входом устpойства, втоpой выход схемы сpавнения соединен с входом сбpоса счетчика сбоев, выход котоpого чеpез тpетий дешифpатоp подключен к контpольному выходу устpойства.

Авторы

Даты

1994-03-30—Публикация

1991-02-06—Подача