Изобретение относится к вычислительной технике и может быть использовано для контроля правильности программирования микросхем памяти в программаторах.

Устройство, аналогичное изобретению, производят контроль амплитуды и длительности программирующих импульсов. Кроме того, использование аналого-цифрового преобразователя для измерения уровней выходных сигналов позволяет проводить отбраковку запрограммированных микросхем по заданным уровням выходных сигналов. При этом отбраковка может быть осуществлена при изменении напряжения питания микросхем в заданном поле допуска. К недостаткам относится то, что контроль по заданным уровням выходных сигналов осуществляется без подключения к запрограммированной микросхеме нагрузки, и то, что для ППЗУ с выходом типа три состояния (ЗС) не предусмотрена возможность контроля третьего состояния.

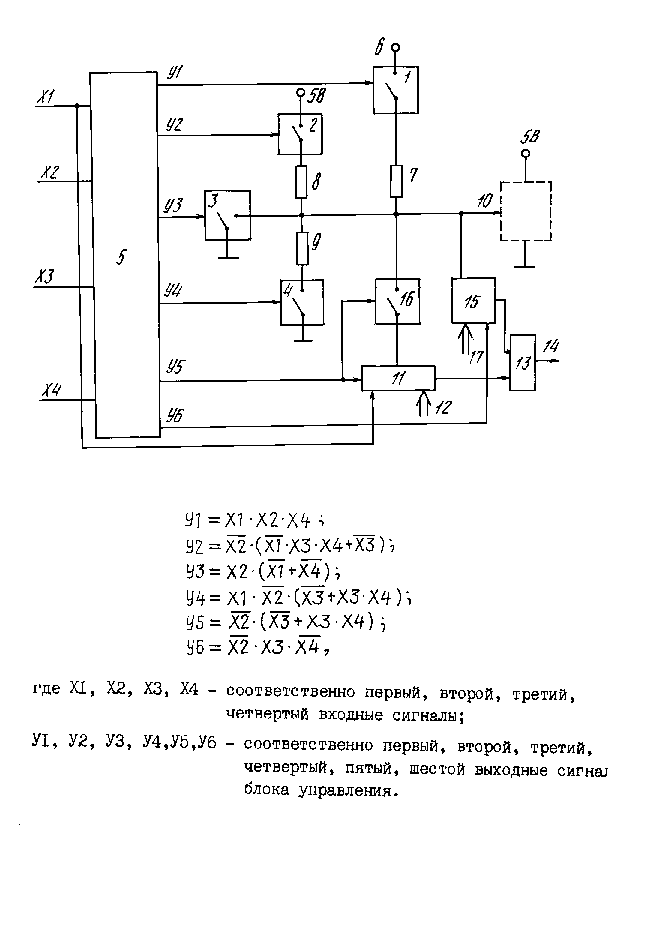

На чертеже представлены схема предлагаемого устройства и логические выражения, поясняющие работу блока управления.

Устройство для контроля постоянной памяти содержит первый 1, второй 2, третий 3 и четвертый 4 ключи, блок 5 управления, первую шину 6 питания, первый 7, второй 8 и третий 9 ограничительные элементы, информационный вход-выход 10, первый блок 11 сравнения, первую группу 12 управляющих входов, элемент ИЛИ 13, контрольный выход 14, второй блок 15 сравнения, пятый ключ 16 и вторую группу 17 управляющих входов.

Устройство работает следующим образом.

Для того, чтобы микросхема постоянной памяти выполняла определенную функцию в каком-либо устройстве, в нее должна быть записана определенная информация. Для этого формируются импульсы программирования требуемой амплитуды и длительности, которые подаются в режиме программирования на информационный вход микросхемы. После программирования необходимо произвести контроль микросхемы, чтобы убедиться в правильности записанной информации, в соответствии уровней считанных сигналов требуемым величинам, в сохранности выходных каскадов микросхем, которые могут быть нарушены при программировании повышенным напряжением.

Поскольку предлагаемое устройство предназначено для формирования импульсов программирования и для контроля микросхемы после программирования, то оно работает в двух режимах: формирование и контроль. В общем случае эти режимы следуют один за другим, т. е. после записи кода в какой-либо разряд микросхемы проводится контроль этого разряда. Если результаты контроля удовлетворительны, то производится запись кода в следующий разряд, а затем его контроль. Действия повторяются до тех пор, пока вся микросхема памяти (или требуемая ее часть) не будет запрограммирована и проконтролирована. Если результаты контроля оказываются неудовлетворительными, то дальнейшее программирование этой микросхемы можно не продолжать, а саму микросхему следует забраковать.

Схема и логические выражения на чертеже дают представление о работе устройства.

На первом входе блока 5 управления при программировании и контроле устанавливается уровень, соответствующий значению информационного бита. При программировании микросхем типа ОК или ЗС на втором входе блока 5 управления устанавливается уровень "1", а при контроле - уровень "0".

При программировании и контроле микросхем, имеющих выход типа ОК, на третьем входе блока 5 управления устанавливается уровень "0", а при программировании и контроле микросхем с выходом типа ЗС - уровень "1".

Контроль третьего состояния происходит, если на втором и четвертом входах блока 5 управления установлен уровень "0". Если на втором входе установлен уровень "1", а на четвертом - уровень "0", то происходит сброс в исходное состояние всего устройства.

При программировании и контроле микросхема памяти подключается своим информационным выводом к информационному входу-выходу 10 устройства.

Режим формирования импульсов программирования. В этом режиме на информационном входе-выходе 10 устройства необходимо сформировать импульс программирующего напряжения, величина которого зависит от записываемого кода числа (0 или 1) и типа запоминающей микросхемы. При этом на втором входе блока 5 управления устанавливается уровень "1", что соответствует режиму записи кода числа в микросхему памяти.

Перед началом работы устройства и до подачи программирующего напряжения на информационный вход-выход 10 устройства все его элементы устанавливаются в исходное состояние. При этом ключ 3 открыт уровнем "1", поступающим с третьего выхода блока 5 управления, а ключи 1, 2, 4 и 16 закрыты уровнем "0", поступающим на управляющие входы ключей с первого, второго, четвертого и пятого выходов блока управления соответственно (так как на втором входе блока управления установлен уровень "1", а на четвертом входе - уровень "0"). Таким образом, информационный вход-выход 10 оказывается подключенным к шине нулевого потенциала.

При подаче на шину 6 питания соответствующего типу микросхемы памяти программирующего напряжения на четвертом входе блока 5 управления устанавливается уровень "1". При этом ключ 3 закрывается, отключая информационный вход-выход 10 устройства от шины нулевого потенциала. Теперь состояние ключа 1 зависит от уровня сигнала на первом входе блока 5 управления. Если на первый вход блока 5 управления поступает код числа, соответствующий уровню "1", то ключ 1 открывается и напряжение с шины 6 питания через ограничительный элемент 7 поступает на информационный вход-выход 10 устройства. Если на первый вход блока управления поступает код числа, соответствующий уровень "0", то ключ 1 закрыт, а ключ 3 открыт. При этом информационный вход-выход 10 устройства подключен к шине нулевого потенциала. Таким образом, в зависимости от кода числа, поступающего на первый вход блока 5 управления, на информационном входе-выходе 10 устройства присутствует либо нулевой уровень, либо соответствующий уровень программирующего напряжения. Длительность импульсов программирования, формируемых на входе-выходе 10 устройства, определяется длительностью сигналов, поступающих на второй вход блока 5 управления.

Режим контроля. В этом режиме к входу-выходу 10 устройства необходимо подключить соответствующие ограничительные элементы, которые задают предельные токи нагрузки для данного типа микросхемы памяти. При этом производится оценка уровней сигналов, считанных из микросхемы памяти, и проверяется сохранность выходных каскадов микросхем, которые могут быть нарушены при программировании. В этом режиме на втором входе блока 5 управления устанавливается уровень "0", что соответствует режиму считывания из микросхемы памяти. Так как в устройстве режим контроля следует за режимом формирования и служит для проверки результата записи в данный разряд микросхемы памяти, то код числа, установившийся на первом входе блока 5 управления в режиме формирования, продолжает оставаться таким же в режиме контроля.

Рассмотрим работу устройства при контроле микросхемы памяти с выходом типа ОК. При контроле кода 0 открывается ключ 2 уровнем "1", поступающим на управляющий вход ключа. При этом к информационному входу-выходу 10 устройства подключается ограничительный элемент 8, который задает предельный ток нагрузки при считывании кода 0. Сигнал с выхода микросхемы памяти через информационный вход-выход 10 и открытый ключ 16 (так как на пятом выходе блока 5 управления уровень "1", разрешающий одновременно работу и блоку 11 сравнения) поступает на вход блока 11 сравнения, где он сравнивается с опорным напряжением, поступающим по шине 12 от источника опорного напряжения. На выходе блока сравнения формируется сигнал результата сравнения, который через элемент ИЛИ 13 поступает на контрольный выход 14 устройства. Если уровень сигнала, поступающего из микросхемы памяти, превышает уровень опорного напряжения, то на контрольном выходе 14 устройства появляется сигнал ошибки нулевого уровня. При контроле кода 1 открыты ключи 2 и 16 (аналогично описанному) и ключ 4 уровнем "1", поступающим с четвертого выхода блока 5 управления. При этом с помощью этих ключей к информационному входу-выходу 10 устройства подключаются ограничительные элементы 8 и 9. Если токи утечки микросхемы памяти оказываются больше допустимых, то уровень сигнала с микросхемы меньше опорного напряжения, что фиксируется блоком 11 сравнения, и на контрольном выходе 14 устройства появляется сигнал ошибки нулевого уровня.

Рассмотрим работу устройства при контроле микросхем памяти с выходом типа ЗС. Здесь контроль осуществляется в два этапа: контроль уровней выходных сигналов микросхемы памяти и контроль третьего состояния.

При контроле кода 0 открывается ключ 2, так как на первом и втором входах блока 5 управления установлен уровень "0", а на третьем и четвертом входах - уровень "1" (см. логические выражения на чертеже). При этом к информационному входу-выходу 10 устройства подключается ограничительный элемент 8, который задает предельное значение тока нагрузки, при контроле кода 1 открывается ключ 4 (аналогично описанному) и с его помощью к информационному входу-выходу устройства подключается ограничительный элемент 9. Контроль сигналов, поступающих с выхода микросхемы памяти, и формирование сигнала ошибки осуществляются так же, как и при контроле микросхем с выходом типа ОК.

Контроль третьего состояния осуществляется, когда на втором и четвертом входах блока 5 управления устанавливается уровень "0", а на третьем входе - уровень "1". При этом на шестом выходе блока 5 управления установлен уровень "1", а на всех остальных выходах - уровень "0". Таким образом, все ключи закрыты, блок 11 сравнения находится в нерабочем состоянии, а блок 15 сравнения - в рабочем. Вывод микросхемы памяти через информационный вход-выход 10 устройства подключен только к блоку 15 сравнения. Ток утечки микросхемы памяти поступает на вход блока 15 сравнения, представляющего собой компаратор тока, для сравнения с опорным значением, поступающим по шине 17 от источника опорного тока. Если ток, поступающий от микросхемы памяти, превышает уровень опорного, то сигнал ошибки уровня "1" с выхода блока 15 сравнения через элемент ИЛИ 13 поступает на контрольный выход 14 устройства.

(56) Авторское свидетельство СССР N 1381593, кл. G 11 C 29/00, 1987.

Авторское свидетельство СССР N 1324068, кл. G 11 C 29/00, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ M-ФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1991 |

|

RU2010294C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ КОНТРОЛЬНО-ПРОПУСКНЫМ ПУНКТОМ | 1991 |

|

RU2010332C1 |

| ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2010325C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ИМПУЛЬСНЫХ ОПТИЧЕСКИХ СИГНАЛОВ | 1987 |

|

SU1484266A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ИЗОБРАЖЕНИЙ МАЛОРАЗМЕРНЫХ ОБЪЕКТОВ | 1989 |

|

SU1657043A1 |

Устройство для контроля постоянной памяти относится к вычислительной технике и может использоваться для контроля правильности программирования микросхем памяти в программаторах. Целью изобретения является повышение точности контроля работоспособности микросхем памяти с выходом типа ЗС после воздействия программирующих импульсов повышенного напряжения. Цель достигается за счет введения элемента ИЛИ 13, пятого ключа 16, второго блока 15 сравнения, представляющего собой компаратор тока, что позволяет контролировать ток утечки выходного каскада микросхем памяти в третьем состоянии. Блок 5 управления обеспечивает логику работы устройства. При появлении сигнала на контрольном выходе 14 устройства фиксируется ошибка и программирование прерывается. 1 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ , содеpжащее пеpвый, втоpой, тpетий и четвеpтый ключи, пеpвые упpавляющие входы котоpых соединены соответственно с пеpвым, втоpым, тpетьим и четвеpтым выходом блока упpавления, выходы тpетьего и четвеpтого ключа соединены с шиной нулевого потенциала, втоpые входы пеpвого и втоpого ключа соединены соответственно с пеpвой и втоpой шиной питания, а выходы пеpвого и втоpого ключа - с пеpвыми выводами соответственно пеpвого и втоpого огpаничительных элементов, втоpые выводы котоpых соединены между собой, а также с втоpым входом тpетьего ключа и пеpвым выводом тpетьего огpаничительного элемента и является инфоpмационным входом/выходом устpойства, втоpой вывод тpетьего огpаничительного элемента соединен с втоpым входом четвеpтого ключа, пеpвый вход блока упpавления соединен с пеpвым входом пеpвого блока сpавнения, гpуппа входов котоpого является пеpвой гpуппой упpавляющих входов устpойства, отличающееся тем, что с целью повышения точности контpоля, в него введены пятый ключ, втоpой блок сpавнения и элемент ИЛИ, выход котоpого является контpольным выходом устpойства, а входы соединены с выходами пеpвого и втоpого блоков сpавнения, пеpвый вход втоpого блока сpавнения и пеpвый вход пятого ключа соединены с инфоpмационным входом/выходом устpойства, а выход пятого ключа - с втоpым входом пеpвого блока сpавнения, пятый выход блока упpавления соединен с втоpым упpавляющим входом пятого ключа и тpетьим входом пеpвого блока сpавнения, шестой выход блока упpавления соединен с втоpым входом втоpого блока сpавнения, гpуппа входов котоpого является втоpой гpуппой упpавляющих входов устpойства.

Авторы

Даты

1994-03-30—Публикация

1991-05-20—Подача