Устройство относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации операции вычисления натурального логарифма комплексного числа в форме с фиксированной точкой.

Известно устройство для вычисления логарифма, содержащее два сумматора-вычитателя, три регистра сдвига, блок управления, блок сравнения, блок хранения константы, накапливающий сумматор, два шифратора, группу элементов И и элемент НЕ [1] .

Недостатком известного устройства являются ограниченные функциональные возможности, позволяющие производить обработку только действительных аргументов.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления логарифма, содержащее четыре регистра, шесть сумматоров, два сдвигателя, два блока памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ [2] .

Недостатком данного устройства является низкое быстродействие.

Цель изобретения - увеличение быстродействия устройства.

Все элементы заявляемого устройства могут быть выполнены на серийно - выпускаемых микросхемах, в силу чего предложенное техническое решение соответствует критерию "техническое решение задачи".

Устройство осуществляет вычисление натурального логарифма комплексного числа в форме с фиксированной точкой.

Предлагаемое устройство производит выполнение операции Z = U + V · i = ln (x + y ·i); x+y ≠ 0;  x

x ]

]  , 1[;

, 1[;  y

y [0,1[. . Операнды x и y представлены (n+1)-разрядными дополнительными кодами в форме с фиксированной точкой. Нулевой разряд каждого кода определяет значение знака соответствующего операнда/ а разряды с первого по n-й - соответствующие числовые разряда операнда.

[0,1[. . Операнды x и y представлены (n+1)-разрядными дополнительными кодами в форме с фиксированной точкой. Нулевой разряд каждого кода определяет значение знака соответствующего операнда/ а разряды с первого по n-й - соответствующие числовые разряда операнда.

Вычисление значения комплексного числа z производится в два этапа. На первом этапе ∀k ∈ { 1,2, . . . , q} ∃ q ∈ { 1,2, . . . , n+1} вычисления выполняются с использованием рекуррентных соотношений

ak : = ak-1 - sk. 2-jk bk-1;

bk: = bk-1 + sk. 2-jk ak-1;

ck: = ck-1 + sk. 2-jk arctg 2-jk; (1)

dk: = dk-1 + sk. 1/2 ln (1 + 2-2jk).

Начальные условия определяются соотношениями

ao: = y . sign x; bo: = x . sign x;

c0: =  _

_  · sign x; do: = 0. (2)

· sign x; do: = 0. (2)

Значение sk определяется на первом этапе вычислений знаком операнда ak-1:

sk = sign ak-1 = 1-2 . ak-1(0). (3)

Значение величины jk на первом этапе вычислений принимается равным разности номеров старшего разряда кода ak-1, имеющего единичное (нулевое) значение при положительном (отрицательном) значении величины ak-1, старшего разряда кода bk-1, имеющего единичное значение в случае, если указанная разность положительна, и нулю в противном случае согласно выражениям

j1k: = min{ j ∈ [ N l ak-1(j) =  } ;

} ;

j2k: = min { j ∈ [ N l bk-1 (j) = 1} ; (4)

jk: = max { 0, j1k - j2k} .

Первый этап вычислений продолжается до тех пор, пока в результате реализации очередной q-й итерации будет выполнено условие

l aql < 2-m, (5) где m - мультипликативная разрядность вычислений, m > n.

Сформированное по окончании выполнения первого этапа значение cq представляет собой мнимую часть v результата выполнения операции.

Второй этап выполнения операции реализует ∀k∈ { q+1, q+2, . . . , t} ∃ t ∈ { 0,1, . . . , 2n} вычисления с использованием рекуррентных соотношений

bk: = bk-1 + sk. 2-jk bk-1;

dk: = dk-1 + sk. ln(1 + 2-jk)-1. (6)

На втором этапе вычислений значение sk определяется значением нулевого разряда кода операнда bk-1 в соответствии с выражением

sk = sign(1-bk-1) = 1-2 . bk-1(0). (7)

Нулевой разряд кода bk-1 определяет значение целой части операнда bk-1.

Значение величины jk на втором этапе вычислений принимается на единицу меньшим номера старшего разряда дробной части кода bk-1, имеющего нулевое (единичное) значения, при bk-1 < 1 (bk-1 ≥1) в соответствии с выражением

jk: = min{ j ∈ No l bk-1(j+1) = bk-1(0)} . (8)

Второй этап вычислений продолжается до тех пор, пока в результате реализации очередной t-й итерации будет выполнено условие

l 1 - bt l < 2-m.

По окончании вычислений значение dt представляет собой действительную часть u результата z.

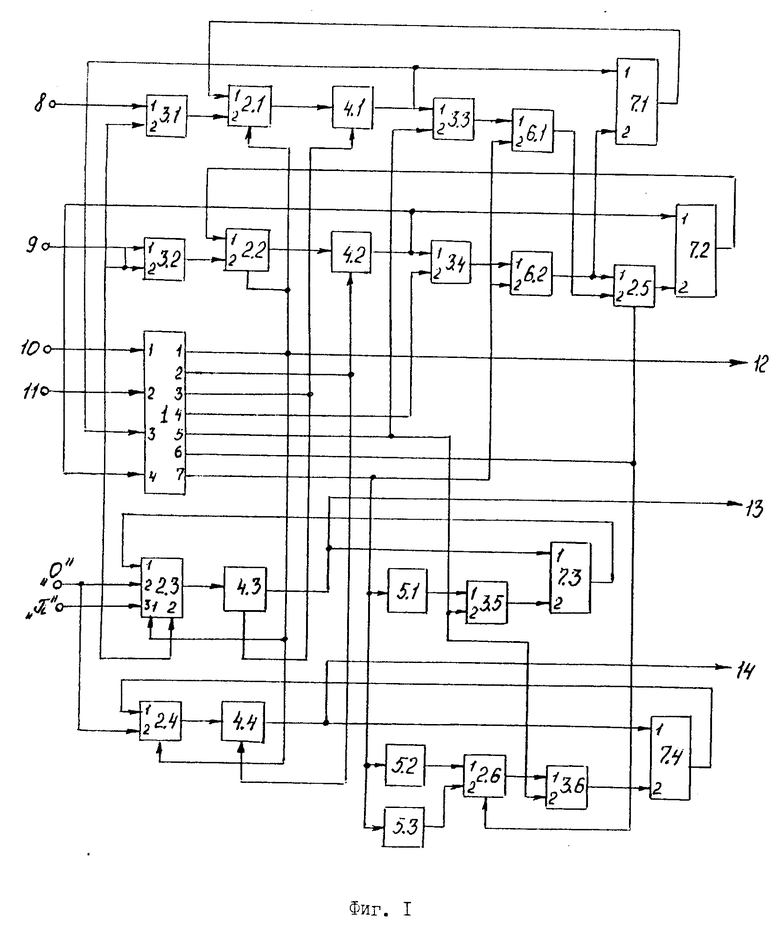

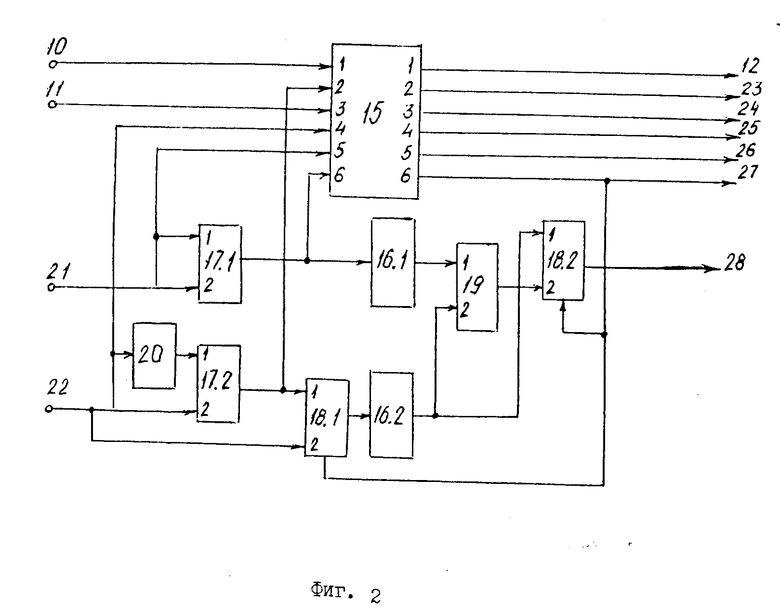

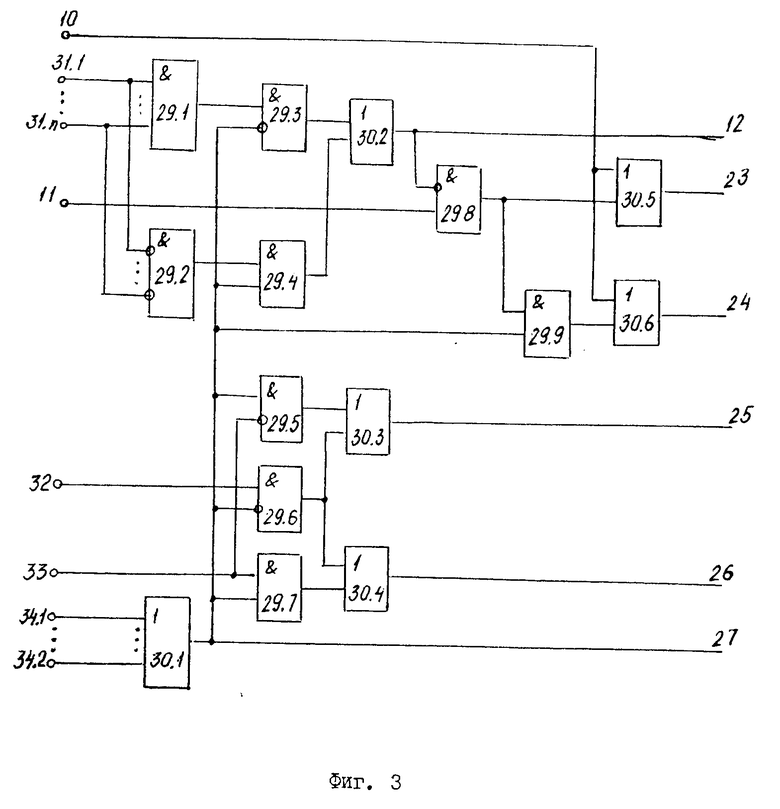

На фиг. 1 представлена структурная схема устройства для вычисления натурального логарифма комплексного числа; на фиг. 2 - структурная схема блока управления; на фиг. 3 - функциональная электрическая схема узла формирования управляющих сигналов.

Устройство содержит блок 1 управления, шесть мультиплексоров 2, шесть сумматоров 3 по модулю два, четыре регистра 4, три блока 5 памяти, два сдвигателя 6, четыре сумматора 7, имеет четыре входа 8-11 и три выхода 12-14.

Блок управления содержит узел 15 формирования управляющих сигналов, два узла 16 выбора старшей единицы, два сумматора 17 по модулю два, два мультиплексора 18, сдвигатель 19, элемент НЕ 20, имеет первый 10, второй 11, третий 21 и четвертый 22 входы и семь выходов 12, 23-28.

Узел 15 формирования управляющих сигналов содержит девять элементов И 29 и шесть элементов ИЛИ 30, имеет первый 10, второй 31, третий 11, четвертый 32, пятый 33 и шестой 34 входы и шесть выходов 12, 23-27.

Устройство работает следующим образом.

В исходном состоянии признак КОНЕЦ ОПЕРАЦИИ, поступающий с первого выхода блока 1 управления на выход 12 устройства, имеет единичное значение. На вход 11 устройства непрерывно поступают тактовые импульсы (ТИ). На вход 8 и вход 9 устройства поступают значения аргументов у и х соответственно. При поступлении в устройство коды аргументов дополняются нулями до v числовых разрядов (v - вычислительная разрядность, обеспечивающая заданную величину погрешности при усечении чисел, сдвигаемых за пределы разрядной сетки, v ≥ m).

Первый 3.1 и второй 3.2 сумматоры по модулю два осуществляют формирование значений ао и bo согласно выражению (2). С выходов сумматоров 3.1 и 3.2 начальные значения ао и bo поступают на вторые входы первого 2.1 и второго 2.2 мультиплексоров соответственно. На вторые входы третьего 2.3 и четвертого 2.4 мультиплексоров поступает нулевой код, на третий вход третьего 2.3 мультиплексора - код числа π . Единичное значение признака КОНЕЦ ОПЕРАЦИИ, поступая на управляющие входы первого 2.1, второго 2.2 и четвертого 2.4 мультиплексоров с первого выхода блока 1 управления, обеспечивает прохождение информации с вторых информационных входов мультиплексоров 2.1, 2.2 и 2.4 на информационные входы регистров 4.1, 4.2 и 4.4 соответственно. Единичный уровень признака КОНЕЦ ОПЕРАЦИИ на первом управляющем входе мультиплексора 2.3 обеспечивает прохождение информации с второго (третьего) информационного входа мультиплексора 2.3 на информационный вход регистра 4.3 при поступлении на второй управляющий вход мультиплексора 2.3 нулевого (единичного) значения знакового разряда аргумента х.

Для начала вычислений синхронно с одним из ТИ на вход 10 устройства подается сигнал ПУСК, поступающий на первый вход блока 1 управления. Блок управления по сигналу ПУСК формирует на своем втором выходе сигнал ЗАНЕСЕНИЕ "1", поступающий на входы занесения регистров 4.2 и 4.4, а на своем третьем выходе сигнал ЗАНЕСЕНИЕ "2", поступающий на входы занесения регистров 4.1 и 4.3, обеспечивая запись в регистры 4 информации, сформированной на их информационных входах. С выходов регистров 4.1 и 4.2 (m+1)-разрядные коды ao* и bo*, содержащие старшие разряды кодов ао и bo, поступают на третий и четвертый входы блока 1 управления соответственно.

При поступлении в блок управления отличного от единицы кода bo* признак КОНЕЦ ОПЕРАЦИИ на первом выходе блока управления принимает нулевое значение. При поступлении на третий вход блока управления нулевого кода ао*, на его шестом выходе формируется нулевой уровень признака НОМЕР ЭТАПА, и устройство начинает выполнение вычислений сразу с второго этапа. При отличном от нуля значении величины ао* признак НОМЕРА ЭТАПА на шестом выходе блока 1 управления принимает единичное значение, и в устройстве начинается первый этап вычислений.

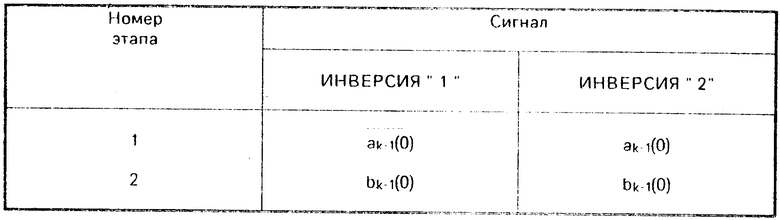

На первом этапе вычислений при выполнении k-й итерации ∀k ∈ { 1,2, . . . , q} единичное значение признака НОМЕР ЭТАПА, поступая на управляющие входы пятого 2.5 и шестого 2.6 мультиплексоров, обеспечивает прохождение информации с вторых информационных входов указанных мультиплексоров на их выходы. На второй вход четвертого 3.4 сумматора по модулю два с четвертого выхода блока 1 управления поступает сигнал ИНВЕРСИЯ "1", на вторые входы третьего 3.3, пятого 3.5 и шестого 3.6 сумматоров по модулю два с пятого выхода блока управления поступает сигнал ИНВЕРСИЯ "2", значения которых определяются таблицей.

На вторые входы первого и второго сдвигателей 6 и на входы первого, второго и третьего блоков 5 памяти с седьмого выхода блока 1 управления поступает m-разрядный унитарный двоичный код Jk, содержащий единицу в jk-м разряде и нули в остальных разрядах. При поступлении на входы блоков 5 памяти кода Jk на выходах первого, второго и третьего блоков памяти формируются коды константы arctg 2-jk, ln(1+2-jk)-1 и 1/2 ln(1+2-2jk) соответственно. Третий 3.3, четвертый 3.4, пятый 3.5 и шестой 3.6 сумматоры по модулю два осуществляют поразрядное суммирование кодов, поступающих на их первые входы с выходов первого 4.1 и второго 4.2 регистров, первого блока 5.1 памяти и шестого 2.6 мультиплексора соответственно с переменными, поступающими на их вторые входы. В результате на первые входы первого 6.1 и второго 6.2 сдвигателей поступают значения sk. ak-1 и -sk. bk-1, сформированные на выходах третьего 3.3 и четвертого 3.4 сумматоров по модулю два соответственно. На первые входы третьего 7.3 и четвертого 7.4 сумматоров поступают значения sk. arctg 2-jk и sk 1/2 ln(1+2-2jk), сформированные на выходах пятого 3.5 и шестого 3.6 сумматоров по модулю два соответственно. Сдвигатели 6 осуществляют сдвиг в сторону младших разрядов кодов, поступивших на их первые входы, на число разрядов, соответствующее номеру единичного разряда в унитарном коде Jk, поступившем на их вторые входы. Информация с выходов сдвигателей 6 непосредственно либо через мультиплексор 2.5, поступает на вторые входы сумматоров 7.1 и 7.2. На первые входы первого 7.1 и второго 7.2, на вторые в ходы третьего 7.3 и четвертого 7.4 сумматоров поступают коды ak-1, bk-1, ck-1 и dk-1 с выходов первого 4.1, второго 4.2, третьего 4.3 и четвертого 4.4 регистров соответственно. Сумматоры 7 осуществляют суммирование кодов, поступающих на их входы в соответствии с выражениями (1). С выходов сумматоров 7 сформированные значения ak, bk, ck и dk поступают на первые информационные входы первого 2.1, второго 2.2, третьего 2.3 и четвертого 2.4 мультиплексоров соответственно. Нулевое значение признака КОНЕЦ ОПЕРАЦИИ, поступающее на управляющие входы мультиплексоров 2.1, 2.2, 2.3 и 2.4, обеспечивает прохождение информации с первых информационных входов указанных мультиплексоров на информационные входы соответствующих регистров 4. С приходом очередного ТИ на втором и третьем выходах блока 1 управления формируются сигналы ЗАНЕСЕНИЕ "1" и ЗАНЕСЕНИЕ "2" соответственно, которые, поступая на входы занесения регистров 4, осуществляют запись в регистр 4 сформированных значений ak, bk, ck и dk. На этом выполнение k-й итерации первого этапа вычислений завершается.

Итерационный процесс первого этапа продолжается до тех пор, пока в результате выполнения очередной q-й итерации значения всех m старших числовых разрядов кода aq*, поступающего с выхода первого регистра 4.1 на третий вход блока 1 управления, станут равными нулю или все разряды кода aq* станут равными единице. В этом случае признак НОМЕР ЭТАПА на шестом выходе блока управления принимает нулевое значение и устройство начинает выполнять второй этап вычислений.

На втором этапе вычислений при выполнении k-й итерации ∀ k ∈ { q+1, q+2, . . . , t} нулевой уровень признака НОМЕР ЭТАПА обеспечивает прохождение информации с первых информационных входов пятого 2.5 и шестого 2.6 мультиплексоров на их выходы. Сигналы ИНВЕРСИЯ "1" и ИНВЕРСИЯ "2" формируются на четвертом и пятом выходах блока 1 управления согласно таблице. Управляющий унитарный код сдвига Jk формируется на седьмом выходе блока управления и поступает на вторые входы сдвигателей 6 и на входы блоков 5 памяти так же, как и на первом этапе вычислений. В процессе выполнения k-й итерации второго этапа значения переменных bk и dk, сформированные на выходах второго 7.2 и четвертого 7.4 сумматоров согласно выражению (6), поступают на информационные входы второго 4.2 и четвертого 4.4 регистров соответственно и заносятся в эти регистры очередным сигналом ЗАНЕСЕНИЕ "1". Сигнал ЗАНЕСЕНИЕ "2" на втором этапе вычислений не формируется, вследствие чего в регистре 4.1 сохраняется значение aq, а в регистре 4.3 - значение cq, сформированные в результате выполнения первого этапа вычислений.

Итерационный процесс второго этапа продолжается до тех пор, пока в результате выполнения очередной t-й итерации все m старших разрядов дробной части кода bt*, поступающего с выхода регистра 4.2 на четвертый вход блока 1 управления, станут равными единице, а целая часть кода bt* - равна нулю, или все m разрядов дробной части кода bt* станут равными нулю, а целая часть кода bt* - единице. В этом случае на первом выходе блока 1 управления сформировано единичное значение признака КОНЕЦ ОПЕРАЦИИ, которое поступает на выход 12 устройства, и устройство прекращает выполнение операции. Значения cq и dt поступают на выходы 13 и 14 устройства в качестве мнимой v и действительной u частей результата соответственно.

Блок управления работает следующим образом. В исходном состоянии на первом выходе узла 15, являющемся одновременно выходом 12 блока, формируется единичное значение признака КОНЕЦ ОПЕРАЦИИ. На вход 11 блока поступают ТИ. Сигнал ПУСК, поступая на вход 10 блока, проходит на первый вход узла 15, формируя на его втором и третьем выходах сигналы ЗАНЕСЕНИЕ "1" и ЗАНЕСЕНИЕ "2", поступающие соответственно на выходы 23 и 24 блока.

В процессе выполнения k-й итерации ∀ k ∈ { 1,2, . . . , t} на входы 21 и 22 блока поступают (m+1)-разрядные коды ak-1* и bk-1* соответственно. Сумматор 17.1 по модулю два осуществляет поразрядное суммирование по модулю два числовых разрядов кода ak-1* со значением знакового разряда кода ak-1*. Сумматор 17.2 по модулю два осуществляет поразрядное суммирование по модулю два числовых разрядов дробной части кода bk-1* с инверсией разряда целой части кода bk-1*. Знаковый разряд кода ak-1* и разряд целой части кода bk-1* поступают, кроме того, на четвертый и пятый входы узла 15 соответственно. На второй и шестой входы узла 15 поступают коды с выходов сумматоров 17.2 и 17.1 по модулю два, соответственно. Узел 16 формирует на своих первом, втором, третьем, четвертом, пятом и шестом выходах признак КОНЕЦ ОПЕРАЦИИ, сигналы ЗАНЕСЕНИЕ "1", ЗАНЕСЕНИЕ "2", ИНВЕРСИЯ "1", ИНВЕРСИЯ "2" и признак НОМЕР ЭТАПА, поступающие на выходы 12, 23-27 блока соответственно. Узлы 16 формируют на своих выходах унитарные коды, содержащие единицу в разрядах, номера которых на единицу меньше номера старшего разряда входного кода, имеющего единичное значение, и нули в остальных разрядах согласно выражениям (4) на первом этапе и (8) на втором этапе вычислений. Сдвигатель 19 осуществляет сдвиг в сторону старших разрядов кода, поступающего на его первый вход, на число разрядов, равное номеру разряда, имеющего единичное значение, в коде, поступающем на его второй вход. На выходе сдвигателя 19 формируется унитарный код Jk. Мультиплексоры 18 обеспечивают прохождение информации со своих первых информационных входов на выходы при нулевом значении признака НОМЕР ЭТАПА, поступающего на управляющие входы мультиплексоров 18, и со своих вторых информационных входов на выходы - при единичном значении признака НОМЕР ЭТАПА. С выхода мультиплексора 18.2 код сдвига Jk поступает на выход 28 блока.

Узел 15 формирования управляющих сигналов работает следующим образом. В исходном состоянии значения кодов на входах 31 и 34 узла обеспечивают формирование на выходе 12 узла единичного значения признака КОНЕЦ ОПЕРАЦИИ, запрещающего прохождение ТИ с входа 11 узла через элемент И 29.8. Сигнал ПУСК, поступающий на вход 10 узла, формирует на выходах 23 и 24 узла сигналы ЗАНЕСЕНИЕ "1" и ЗАНЕСЕНИЕ "2".

При равенстве нулю кода ао* и равенстве единице кода bo* коды, поступающие на входы 31 и 34 узла, обеспечивают сохранение единичного значения признака КОНЕЦ ОПЕРАЦИИ на выходе 12 узла. В случае поступления на входы 31 и 34 узла кодов, имеющих одновременно хотя бы одну единицу и хотя бы один ноль, признак КОНЕЦ ОПЕРАЦИИ принимает нулевое значение, а на выходе элемента ИЛИ 30.1 формируется сигнал единичного уровня, поступающий на выход 27 узла в качестве признака НОМЕР ЭТАПА. Нулевое значение признака КОНЕЦ ОПЕРАЦИИ обеспечивает прохождение ТИ через элемент И 29.8 в качестве сигнала ЗАНЕСЕНИЕ "1" на выход 23 узла и через элемент И 29.9 при единичном значении признака НОМЕР ЭТАПА на выход 24 узла в качестве сигнала ЗАНЕСЕНИЕ "2". Поступающие на входы 32 и 33 узла значения bk-1*(0) и ak-1*(0) совместно с сигналом на выходе элемента ИЛИ 30.1 формируют на выходах 25 и 26 узла соответственно сигналы ИНВЕРСИЯ "1" и ИНВЕРСИЯ "2" согласно таблице. При формировании на входе 32 нулевого кода и на входе 31 единичного кода, означающих окончание операции, узел формирования управляющих сигналов переходит в исходное состояние.

Устройство производит вычисление натурального логарифма комплексного числа в среднем за n итераций, что обеспечивает двукратный выигрыш по быстродействию в сравнении с прототипом, выполняющим аналогичную операцию за 2n+1 итераций. Таким образом, положительный эффект изобретения заключается в повышении быстродействия. (56) 1. Авторское свидетельство СССР N 1179328, кл. G 06 F 7/556, 1984.

2. Авторское свидетельство СССР N 1432513, кл. G 06 F 7/556, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА | 1991 |

|

RU2010428C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ИЗМЕРЕНИЯ УРОВНЯ | 1992 |

|

RU2010175C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1985 |

|

SU1286089A1 |

| ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2010325C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ ЭЛЕКТРОМАГНИТОВ ТЕЛЕГРАФНОГО АППАРАТА С ИНДИКАЦИЕЙ НЕИСПРАВНОСТИ | 1988 |

|

RU2010330C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ | 1991 |

|

RU2010363C1 |

Устройство относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации операции вида Z=U+V·i=ln(x+y·i)(x+y·i)≠0 в форме с фиксированной точкой. Цель изобретения - увеличение быстродействия устройства. Цель достигается тем, что в устройство, содержащее четыре регистра 4.1-4.4, два сдвигателя 6.1, 6.2, четыре сумматора 7.1-7.4, два блока 5.1, 5.2 памяти, введены шесть сумматоров 3.1-3,6 по модулю два, шесть мультиплексоров 2.1-2.6, один блок 5.3 памяти и блок 1 управления. 1 з. п. ф-лы, 1 табл. , 3 ил.

Авторы

Даты

1994-03-30—Публикация

1991-03-29—Подача