Изобретение относится к измерительной и вычислительной технике и автоматике и может быть использовано, в частности, в системах корреляционной обработки сигналов.

Известные методы цифровой задержки сигналов имеют погрешность задержки, равную половине периода следования тактовых импульсов, поэтому для повышения точности задержки требуется повышать частоту тактовых импульсов, что не всегда эффективно из-за возрастания емкости счетчиков.

Прототипом предлагаемого устройства является цифровая регулируемая линия задержки, содержащая генератор тактовых импульсов, два элемента И, два счетчика, элемент И-НЕ, регистр, входную, выходную и кодовые шины и шину начальной установки. Однако данная линия задержки имеет ограниченные функциональные возможности из-за задержки входных импульсов только на интервалы, кратные целому числу периодов тактовых импульсов.

Целью изобретения является расширение функциональных возможностей за счет задержки сигналов на интервалы времени, не кратные целому числу периодов тактовых импульсов.

Цель достигается тем, что цифровая регулируемая линия задержки содержит генератор тактовых импульсов, регистр, входную, выходную и кодовую шины.

В отличие от прототипа в устройство дополнительно введены два умножителя, инвертор кода и сумматор, причем входная шина соединена с информационным входом регистра и первым входом первого умножителя, выход регистра соединен с первым входом второго умножителя, кодовая шина соединена с вторым входом первого умножителя и через инвертор кода с вторым входом второго умножителя, выходы первого и второго умножителей подключены соответственно к первому и второму входам сумматора подключен к выходной шине, с первого по третий выходы генератора тактовых импульсов соединены с синхровходами соответственно регистра, двух умножителей и сумматора.

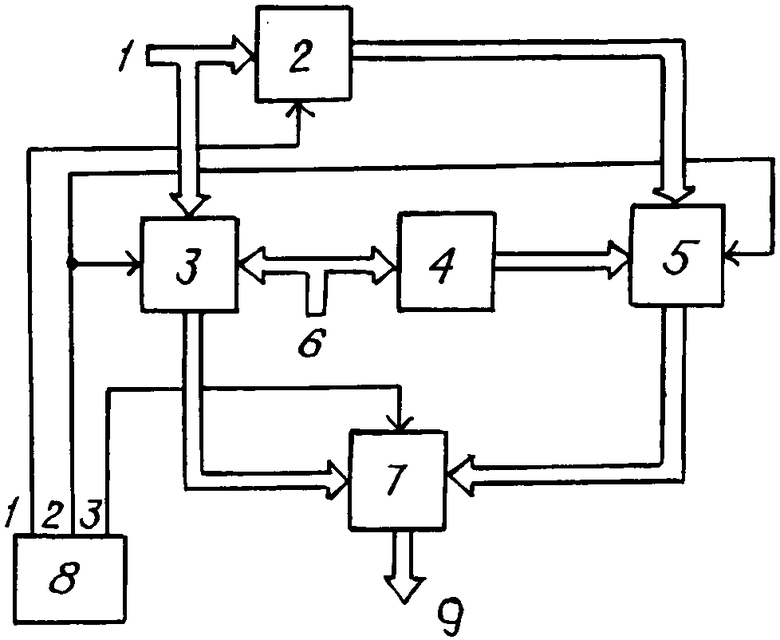

На чертеже изображена структурная схема устройства.

Приведены обозначения: 1 - входная шина; 2 - регистр (сдвига параллельного типа); 3 - умножитель (синхронизируемый); 4 - инвертор кода (поразрядная схема НЕ); 5 - умножитель (синхронизируемый); 6 - кодовая шина; 7 - сумматор (синхронизируемый); 8 - генератор тактовых импульсов; 9 - выходная шина.

Информационная шина 1 устройства подключена к информационному входу регистра 2 и к первому информационному входу умножителя 3. Выход регистра 2 соединен с первым информационным входом умножителя 5. Кодовая шина 6 устройства подключена к второму информационному входу умножителя 3 и через инвертор кода 4 - к второму информационному входу умножителя 5. Выходы умножителей 3 и 5 подключены соответственно к первому и второму информационным входам сумматора 7, выход которого соединен с выходной шиной 9 устройства. Генератор тактовых импульсов 8 своими выходами подключен к синхровходам следующих блоков:

выход 8.1 - регистр 2;

выход 8.2 - умножители 3 и 5;

выход 8.3 - сумматор 7.

Устройство работает следующим образом.

На информационную шину 1 устройства поступает код сигнала х(to). По первому импульсу с выхода 8.2 генератора тактовых импульсов (ГТИ) 8, поступающему на синхровход регистра 2, этот код сигнала х(tо) появится на выходе регистра 2 и соответственно на первом информационном входе умножителя 5. На информационную шину 1 устройства поступит через время Δ t уже следующий код отсчета сигнала х(to + Δ t), который подается и на первый информационный вход умножителя 3. На кодовую шину 6 устройства подают код требуемой относительной задержки λ = Δ τ / Δ t, Δ τ ≅ Δ t , сигнала, который поступает на второй информационный вход умножителя 3, и через инвертор кода 4 - на второй информационный вход умножителя 5. В результате, на втором информационном входе умножителя 5 присутствует код (1-λ ), так как 0 < Δ τ ≅ Δ t. По импульсу с второго выхода 8.2 ГТИ 8, поступающему на синхровходы умножителей 3 и 5, на выходах умножитетей 3 и 5 появятся соответственно коды К3 и К5:

К3 = x(to + Δ t) ˙ λ ;

K5 = x(to) ˙ (1-λ ). Эти коды К3 и К5 с выходов умножителей 3 и 5 поступают на первый и второй информационные входы сумматора 7. По импульсу с третьего выхода 8.3 ГТИ 8, поступающему на синхровход сумматора 7, на выходе сумматора 7 (выходной шине 9 устройства) появится код К9 окончательного результата - линейно аппроксимированное значение сигнала с(t) в момент времени t = to+ Δ t

K9 = x(to + Δ t) = x(to) + λ [x(to + Δ t) - x(to)]

Таким образом, предлагаемое устройство позволяет осуществлять регулируемую (код λ ) цифровую задержку сигналов х(t) на интервалы времени Δ τ , не кратные целому числу периодов следования тактовых импульсов (отсчета сигнала): 0 ≅ λ ≅ 1, λ = Δ τ / Δ t чем и достигается поставленная цель изобретения.

(56) Авторское свидетельство СССР N 1661966, кл. Н 03 Н 9/30,

Важенина З. П. и др. Методы и схемы временной задержки импульсных сигналов. М. : Сов, радио, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для обработки информации | 1989 |

|

SU1631539A1 |

| Устройство отождествления | 1991 |

|

SU1803910A1 |

| Цифровая регулируемая линия задержки | 1988 |

|

SU1690173A1 |

| Устройство обработки информации комплексной измерительной системы | 1990 |

|

SU1837283A1 |

| Устройство для определения многомерной плотности распределения случайных процессов | 1988 |

|

SU1605266A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

Цифровая регулируемая линия задержки, относящаяся к автоматике, измерительной и вычислительной технике, позволяет на основе линейной аппроксимации дискретных значений поступающего сигнала формировать значения этого сигнала в моменты времени, отличные от моментов дискретизации сигнала. 1 ил.

ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ, содержащая генератор тактовых импульсов, регистр, входную, выходную и кодовую шины, отличающаяся тем, что в нее дополнительно введены два умножителя, инвертор кода и сумматор, причем входная шина соединена с информационным входом регистра и первым входом первого умножителя, выход регистра соединен с первым входом второго умножителя, кодовая шина соединена с вторым входом первого умножителя и через инвертор кода с вторым входом второго умножителя, выходы первого и второго умножителей подключены соответственно к первому и второму входам сумматора, выход сумматора подключен к выходной шине, с первого по третий выходы генератора тактовых импульсов соединены с синхровходами соответственно регистра, двух умножителей и сумматора.

Авторы

Даты

1994-04-15—Публикация

1992-06-22—Подача