Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации.

Цель изобретения - упрощение путем сокращения числа функциональных блоков.

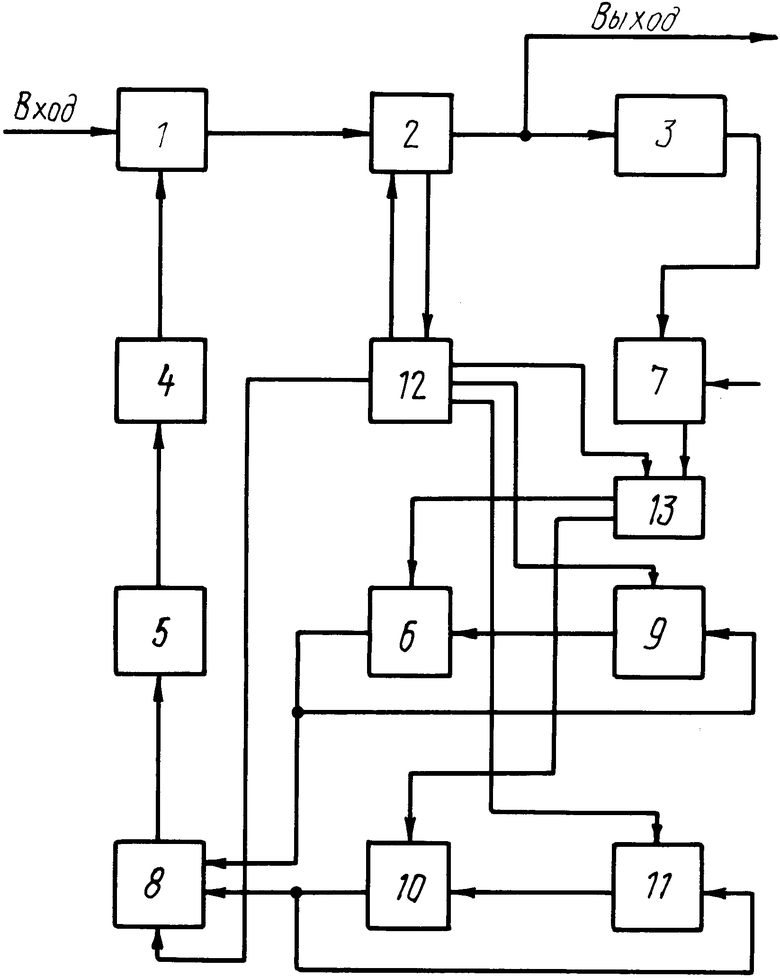

На чертеже изображена структурная электрическая схема предлагаемого компенсатора.

Адаптивный компенсатор пилот-сигнала содержит первый сумматор , аналого-цифровой преобразователь (АЦА) 2, блок 3 определения сигнала ошибки, фильтр 4 нижних частот, цифроаналоговый преобразователь (ЦАП) 5, второй сумматор 6, умножитель 7, первый коммутатор 8, первый блок 9 памяти, третий сумматор 10, второй блок 11 памяти, блок 12 формирования управляющих импульсов и второй коммутатор 13.

Адаптивный компенсатор работает следующим образом.

Входной сигнал подается на суммирующий вход сумматора 1 и с его выхода на вход АЦП. В АЦП 2 осуществляется стробирование принимаемого сигнала точно в центре глазковой диаграммы. Момент времени стробирования определяется командой от блока 12, являющегося синхронизатором работы всего устройства. Блок 12 является вспомогательным и для выработки команд управления использует дискретизированный сигнал от АЦП 2 (первый выход АЦП - цифровой, второй - дискретный). Цифровой выход АЦП 2 является выходом устройства. Одновременно выходной сигнал поступает в блок 3, где вырабатывается сигнал ошибки о величине постоянной составляющей в каждый отсчетный момент времени (т. е. разность между принятым сигналом и ближайшим эталонным уровнем). Это сигнал ошибки умножается в умножителе 7 на величину шага подстройки постоянной составляющей и в зависимости от четности или нечетности отсчета направляется по команде от блока 12 через коммутатор 13 на первый вход сумматора 6 или 10. На вторые входы этих сумматоров подаются долговременные значения постоянной составляющей четных и нечетных отсчетов, хранящихся в блоках 9 и 11 соответственно. В результате операции суммирования в блоках 9 и 11 заносятся новое значение величины постоянной составляющей. Эти значения постоянной составляющей в виде двоичного кода через коммутатор 8 в зависимости от четности (нечетности момента отсчета) по команде от блока 12 подается на ЦАП 5 и через фильтр нижних частот на вычитающий вход сумматора 1. Фильтр 14 нижних частот преобразует ступенчатый сигнал на выходе ЦАП 5 в непрерывный сигнал. При этом в нечетные моменты времени глазковая диаграмма опускается вниз, а в четные моменты поднимается вверх. Таким образом обеспечивается нулевое значение сигнала полутактовой частоты и нулевое значение постоянной составляющей в момент отсчета сигнала в АЦП 2. При наличии дрейфа постоянной составляющей предлагаемый компенсатор работает точно также.

(56) Ундроу Б. И Стернз С. Адаптивная обработка сигналов. М. : Радио и связь, 1989, рис. 12.6 и 12.10.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1993 |

|

RU2039415C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1984 |

|

SU1223373A2 |

| Адаптивная телеизмерительная система | 1983 |

|

SU1133612A2 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2019049C1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| УСТРОЙСТВО МОНИТОРИНГА ВЫСОКОВОЛЬТНЫХ ВВОДОВ И СИГНАЛИЗАЦИИ О СОСТОЯНИИ ИХ ИЗОЛЯЦИИ | 2006 |

|

RU2328009C1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

Сущность изобретения: адаптивный компенсатор пилот-сигнала содержит три сумматора, аналого-цифровой преобразователь, блок определения сигнала ошибки, фильтр нижних частот, цифроаналоговый преобразователь, умножитель, два коммутатора, два блока памяти, блок формирования управляющих импульсов. 1 ил.

АДАПТИВНЫЙ КОМПЕНСАТОР ПИЛОТ-СИГНАЛА, содержащий цифроаналоговый преобразователь, блок формирования управляющих импульсов, последовательно соединенные первый сумматор, аналого-цифровой преобразователь, блок определения сигнала ошибки и умножитель, последовательно соединенные первый блок памяти и второй сумматор, последовательно соединенные второй блок памяти и третий сумматор, выход которого и выход второго сумматора подключены к сигнальным входам соответственно второго и первого блоков памяти, управляющие входы которых и управляющий вход аналого-цифрового преобразователя соединены с одними выходами блока формирования управляющих импульсов, к входу которого подключен второй выход аналого-цифрового преобразователя, при этом первый вход первого сумматора, второй вход умножителя и первый выход аналого-цифрового преобразователя являются соответственно информационным и управляющим входами и выходом адаптивного компенсатора, отличающийся тем, что, с целью упрощения путем сокращения числа функциональных блоков, в него введены два коммутатора и фильтр нижних частот, вход и выход которого соединены соответственно с выходом цифроаналогового преобразователя, к входу которого подключен выход первого коммутатора, и с вторым входом первого сумматора, выход умножителя через второй коммутатор подключен к вторым входам второго и третьего сумматоров, выходы которых соединены с сигнальными входами первого коммутатора, управляющий вход которого и управляющий вход второго коммутатора соединены с другими выходами блока формирования управляющих импульсов.

Авторы

Даты

1994-04-15—Публикация

1990-06-14—Подача