Изобретение относится к области электросвязи, преимущественно к передаче речевых сообщений.

Известны устройства разделения направлений, конструктивно выполненные в виде эквивалентной мостовой схемы, где в одну диагональ моста включен передатчик, а в другую диагональ включено приемное устройство. Принцип действия таких систем основан на возможности организации дуплексной связи при идеально сбалансированных сопротивлениях плеч мостовой схемы. Однако, из-за разброса параметров коммутируемых каналов не удается полностью сбалансировать мостовую схему, поэтому сигналы собственного передатчика проникают в приемное устройство, существенно снижая качество работы последнего, например, увеличивая вероятность ошибочного приема единичного элемента.

Наиболее близкой по технической сущности является цифровая дифсистема, включающая в себя последовательно соединенные входной блок, коммутатор, первый цифроаналоговый преобразователь, аналого-цифровой преобразователь, первый блок памяти, вычитатель, вторым входом соединенный с выходом аналого-цифрового преобразователя, сумматор, второй блок памяти, выходом соединенный с. вторым входом сумматора, а также второй ЦАП, формирователь адреса и генератор.

Речевой сигнал является случайной функцией, поэтому цифровая дифсистема должна постоянно адаптироваться к различным параметрам речевого сигнала и канала связи, Данное же устройство не обладает возможностью постоянно подстраиваться к параметрам канала связи при изменении характеристик передаваемого сигнала. Результатом этого является низкая достоверность принимаемых сигналов, приходящих из канала связи из-за недостаточной компенсации сигналов своего передатчика в тракте приема.

сл

С

Si

со 4

|Ю

го

о

:

Целью изобретения является повышение помехоустойчивости принимаемых речевых сигналов.

Поставленная цель достигается тем, что в адаптивную цифровую дифсистему, содер- жащую последовательно соединенные первый цифроаналоговый преобразователь, аналого-цифрвоой преобразователь и блок памяти, а также входной блок, вычитатель, вторым входом соединенный с первым вхо- дом блока памяти, сумматор, второй цифро- аналоговый преобразователь, коммутатор и генератор, первым выходом соединенный соответственно с вторым входом входного блока аналого-цифрового преобразователя, вторым входом блока памяти, третий вход которого объединен с входом первого циф- роаналогового преобразователя введены последовательно соединенные триггер, счетчик, элемент И, а также детектор, эле- мент запрета, первый и второй буферный регистры, при этом второй выход аналого- цифрового преобразователя соединен с об- нуляющим входом триггера, второй тактовый вход которого соединен с первым выходом генератора, а информационный вход триггера соединен с выходом сумматора, при этом выход вычитателя соединен одновременно через второй буферный регистр по входу второго цифроаналогового преобразователя, и через детектор - к входу сумматора, на второй вход которого подано пороговое значение Мпор, при этом второй вход второго буферного регистра соединен с первым выходом генератора, третий вы- ход которого через элемент запрета соединен с вторым входом счетчика, выход которого соединен с вторым входом элемента запрета, выход коммутатора соединен с четвертым входом блока памяти, выход которого через первый буферный регистр соединен с первым входом вычитателя, второй выход генератора соединен с вторыми входами первого буферного регистра, коммутатора, и элемента И соответст- венно, выход входного блока соединен с входом первого цифроаналогового преобразователя, выход которого соединен с линией передачи, а входом и выходом устройства являются вход входного блока и выход второго цифроаналогового преобразователя, при этом выход элемента И соединен с третьим входом коммутатора, первый вход которого соединен с первым выходом генератора,

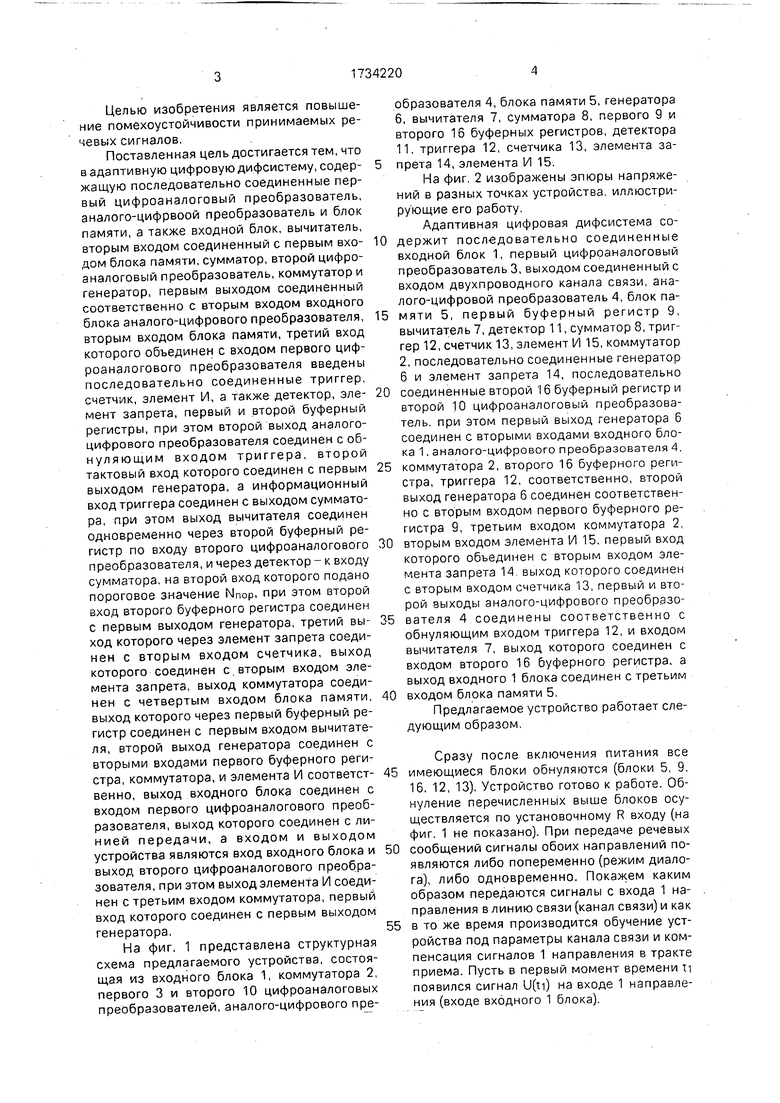

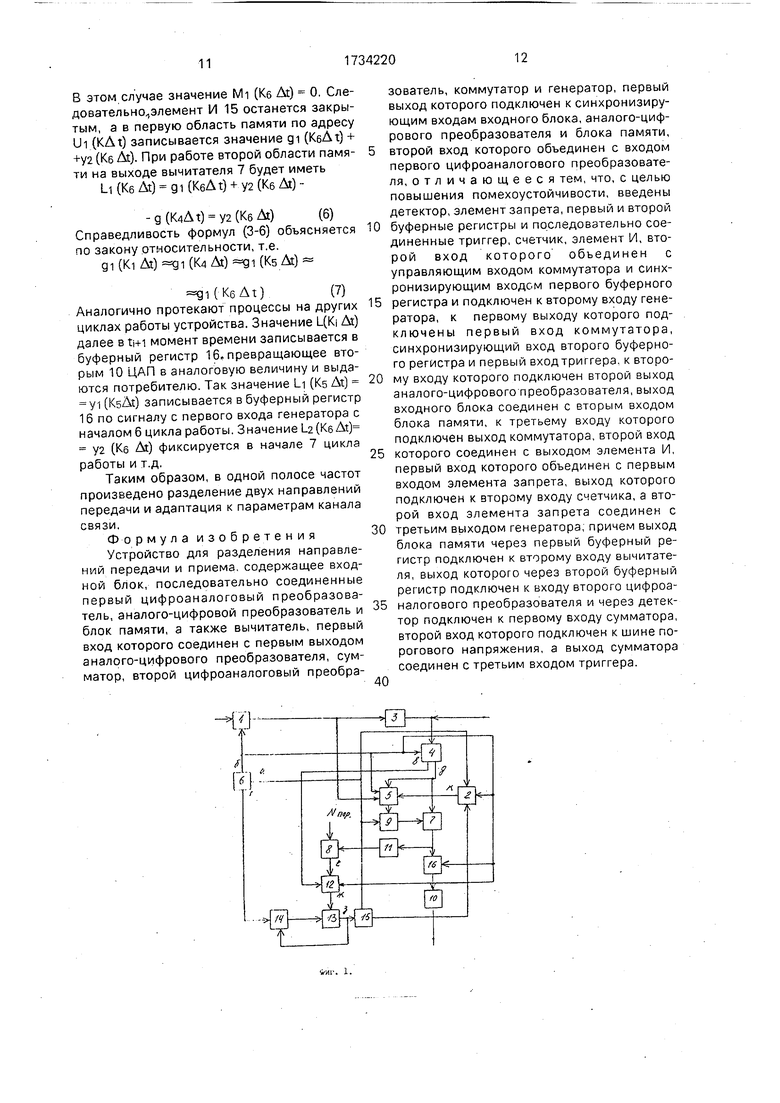

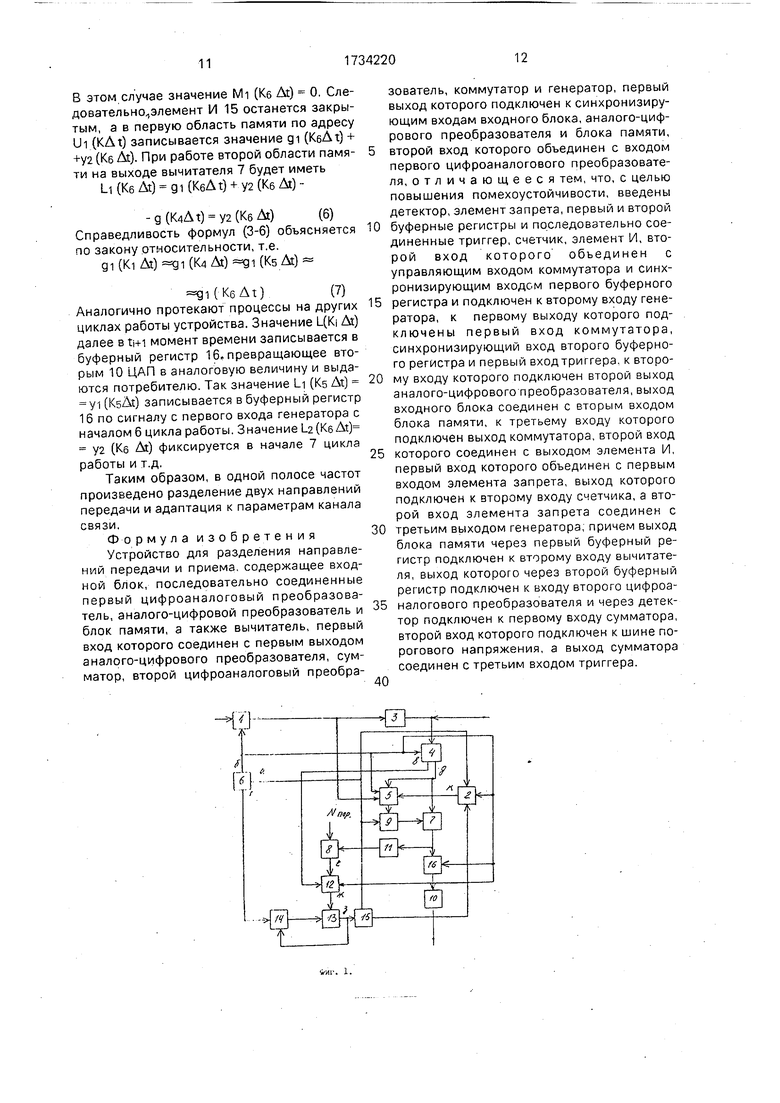

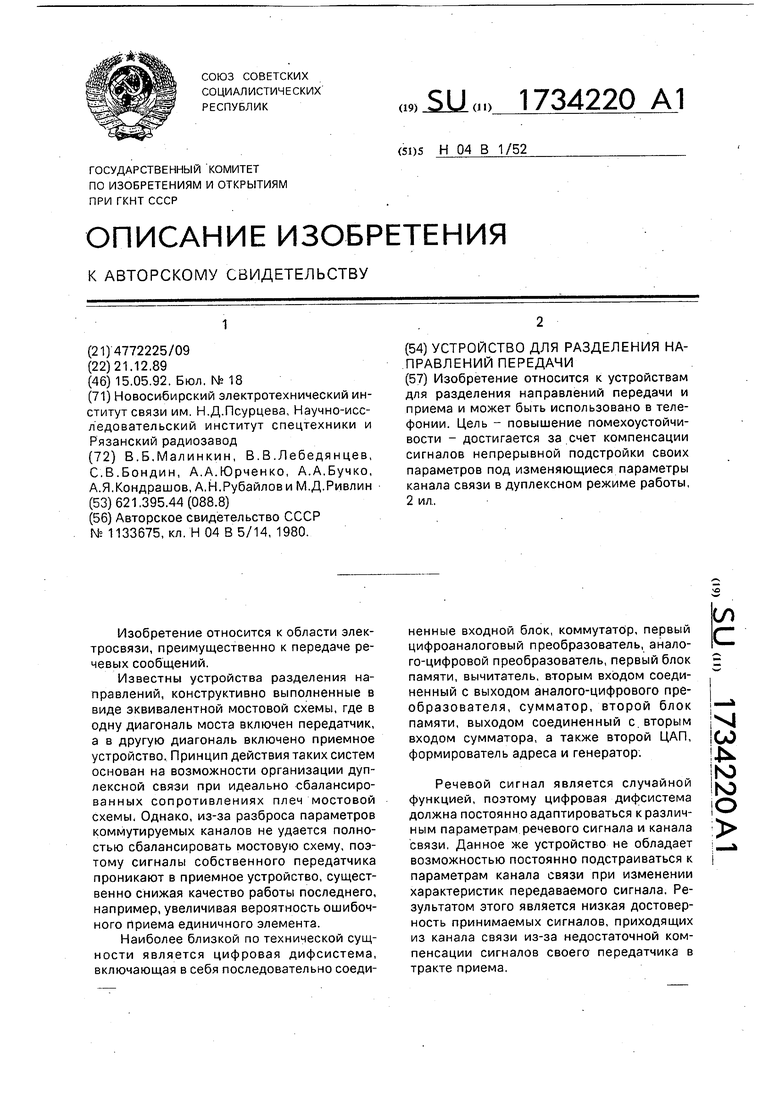

На фиг, 1 представлена структурная схема предлагаемого устройства, состоящая из входного блока 1, коммутатора 2, первого 3 и второго 10 цифроаналоговых преобразователей, аналого-цифрового преобразователя 4, блока памяти 5, генератора 6, вычитателя 7, сумматора 8, первого 9 и второго 16 буферных регистров, детектора 11, триггера 12, счетчика 13, элемента запрета 14, элемента И 15.

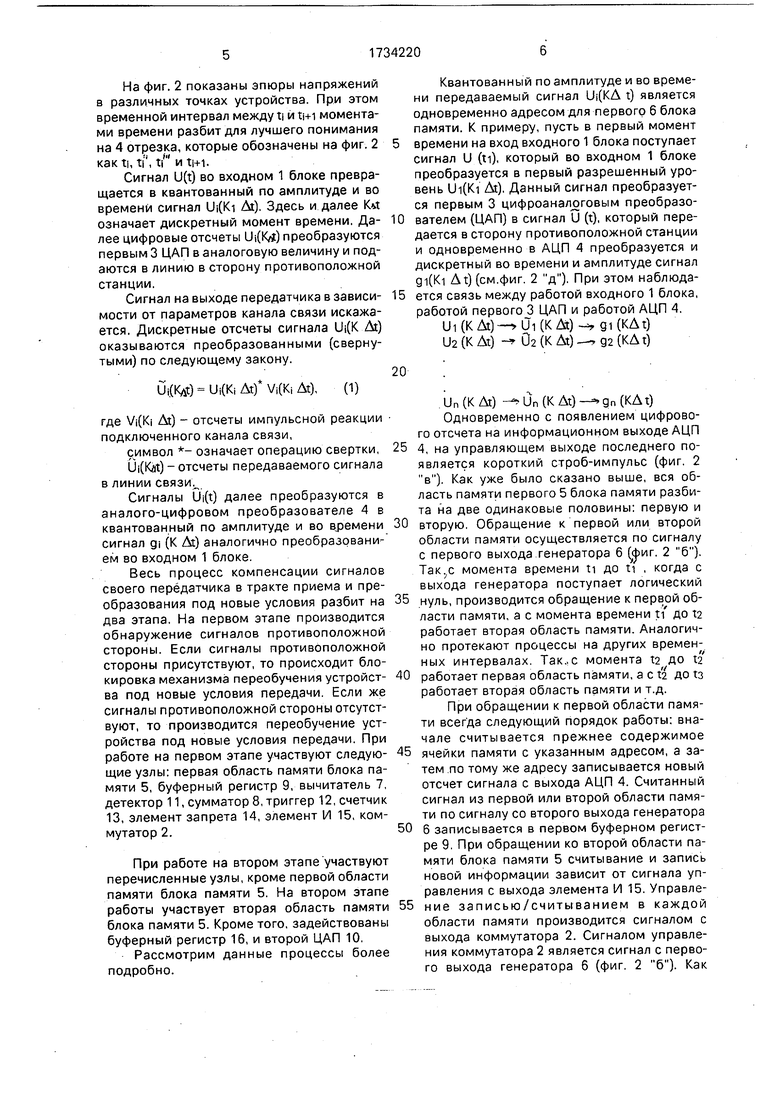

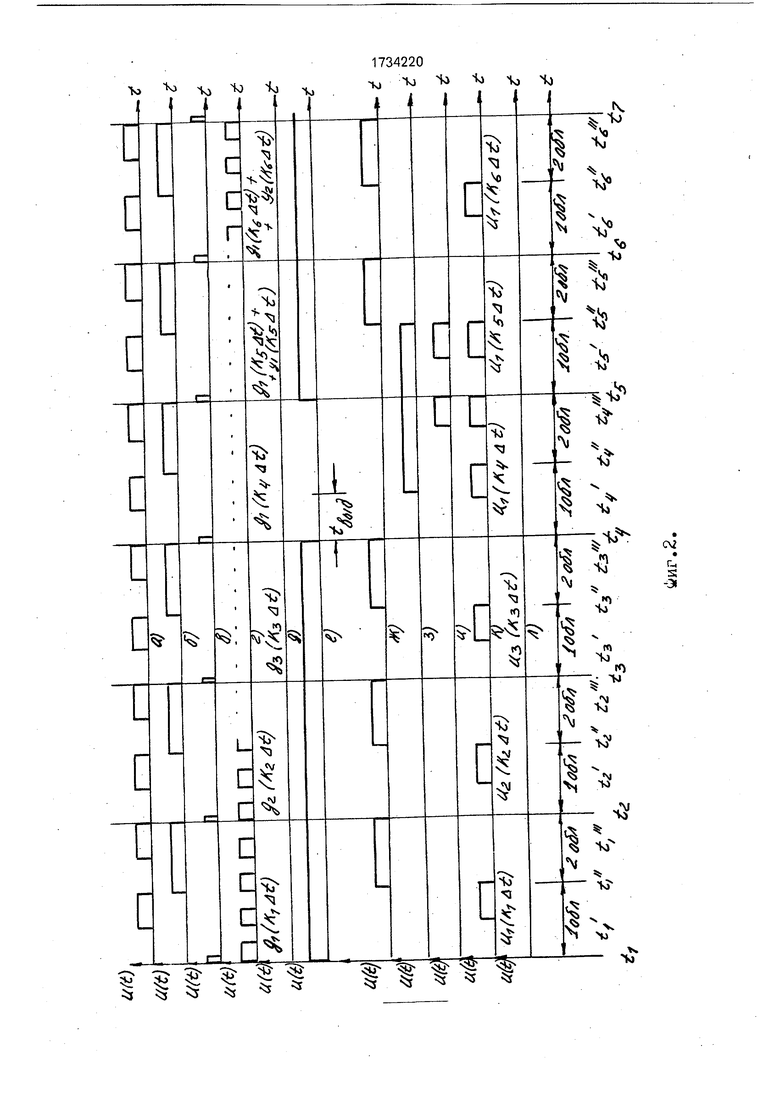

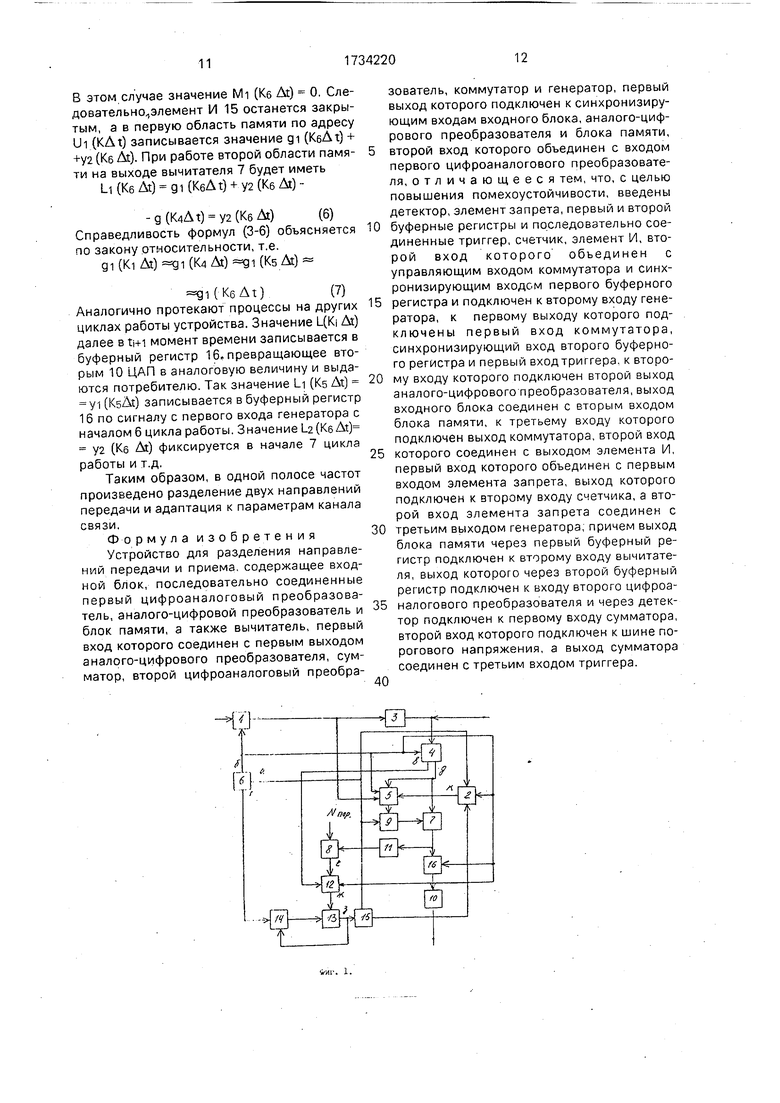

На фиг. 2 изображены эпюры напряжений в разных точках устройства, иллюстрирующие его работу.

Адаптивная цифровая дифсистема содержит последовательно соединенные входной блок 1, первый цифроаналоговый преобразователь 3, выходом соединенный с входом двухпроводного канала связи, аналого-цифровой преобразователь 4, блок памяти 5, первый буферный регистр 9, вычитатель 7, детектор 11, сумматор 8, триггер 12, счетчик 13, элемент И 15, коммутатор 2, последовательно соединенные генератор 6 и элемент запрета 14, последовательно соединенные второй 16 буферный регистр и второй 10 цифроаналоговый преобразователь, при этом первый выход генератора 6 соединен с вторыми входами входного блока 1, аналого-цифрового преобразователя 4, коммутатора 2, второго 16 буферного регистра, триггера 12, соответственно, второй выход генератора 6 соединен соответственно с вторым входом первого буферного регистра 9, третьим входом коммутатора 2, вторым входом элемента И 15, первый вход которого объединен с вторым входом элемента запрета 14 выход которого соединен с вторым входом счетчика 13, первый и второй выходы аналого-цифрового преобразователя 4 соединены соответственно с обнуляющим входом триггера 12, и входом вычитателя 7, выход которого соединен с входом второго 16 буферного регистра, а выход входного 1 блока соединен с третьим входом блока памяти 5.

Предлагаемое устройство работает следующим образом

Сразу после включения питания все имеющиеся блоки обнуляются (блоки 5, 9, 16, 12, 13). Устройство готово к работе. Обнуление перечисленных выше блоков осуществляется по установочному R входу (на фиг. 1 не показано). При передаче речевых сообщений сигналы обоих направлений появляются либо попеременно (режим диалога), либо одновременно. Покажем каким образом передаются сигналы с входа 1 направления в линию связи (канал связи) и как в то же время производится обучение устройства под параметры канала связи и компенсация сигналов 1 направления в тракте приема. Пусть в первый момент времени ti появился сигнал U(ti) на входе 1 направления (входе входного 1 блока).

На фиг. 2 показаны эпюры напряжений в различных точках устройства. При этом временной интервал между ti и ti+1 моментами времени разбит для лучшего понимания на 4 отрезка, которые обозначены на фиг. 2 как ti, ti , tj и ti+1.

Сигнал U(t) во входном 1 блоке превращается в квантованный по амплитуде и во времени сигнал Uj(Ki At). Здесь и далее означает дискретный момент времени. Далее цифровые отсчеты Ui(Krf) преобразуются первым 3 ЦАП в аналоговую величину и подаются в линию в сторону противоположной станции.

Сигнал на выходе передатчика в зависимости от параметров канала связи искажается. Дискретные отсчеты сигнала Uj(K At) оказываются преобразованными (свернутыми) по следующему закону.

Ui(KAt) Ui(K, At) V,(K, At), (1)

где Vi(Ki At) - отсчеты импульсной реакции подключенного канала связи,

символ - означает операцию свертки,

Ui(Kat) - отсчеты передаваемого сигнала в линии связи.

Сигналы Ui(t) далее преобразуются в аналого-цифровом преобразователе 4 в квантованный по амплитуде и во времени сигнал gi (К At) аналогично преобразованием во входном 1 блоке.

Весь процесс компенсации сигналов своего передатчика в тракте приема и преобразования под новые условия разбит на два этапа. На первом этапе производится обнаружение сигналов противоположной стороны. Если сигналы противоположной стороны присутствуют, то происходит блокировка механизма переобучения устройства под новые условия передачи. Если же сигналы противоположной стороны отсутствуют, то производится переобучение устройства под новые условия передачи. При работе на первом этапе участвуют следующие узлы: первая область памяти блока памяти 5, буферный регистр 9, вычитатель 7, детектор 11, сумматор 8, триггер 12, счетчик 13, элемент запрета 14, элемент И 15, коммутатор 2.

При работе на втором этапе участвуют перечисленные узлы, кроме первой области памяти блока памяти 5. На втором этапе работы участвует вторая область памяти блока памяти 5. Кроме того, задействованы буферный регистр 16, и второй ЦАП 10.

Рассмотрим данные процессы более подробно.

Квантованный по амплитуде и во времени передаваемый сигнал ЩКА t) является одновременно адресом для первого 6 блока памяти. К примеру, пусть в первый момент времени на вход входного 1 блока поступает сигнал U (ti), который во входном 1 блоке преобразуется в первый разрешенный уровень Ui(Ki At), Данный сигнал преобразуется первым 3 цифроаналоговым преобразо- вателем (ЦАП) в сигнал U (t), который передается в сторону противоположной станции и одновременно в АЦП 4 преобразуется и дискретный во времени и амплитуде сигнал gi(Ki At) (см.фиг. 2 д). При этом наблюда- ется связь между работой входного 1 блока, работой первого 3 ЦАП и работой АЦП 4. Ui (К At) - Ui (К At) --, gi (KAt) U2 (К At) - 02 (К At) - да (КД t)

.

Un (K At) - Un (K At) - gn (KAt) Одновременно с появлением цифрового отсчета на информационном выходе АЦП

4, на управляющем выходе последнего появляется короткий строб-импульс (фиг. 2 в). Как уже было сказано выше, вся область памяти первого 5 блока памяти разбита на две одинаковые половины: первую и

вторую. Обращение к первой или второй области памяти осуществляется по сигналу с первого выхода генератора 6 (фиг. 2 б). Так.с момента времени ti до ti , когда с выхода генератора поступает логический

нуль, производится обращение к первой области памяти, а с момента времени ti до t2 работает вторая область памяти. Аналогично протекают процессы на других временных интервалах. Так.,с момента t2 до 12

работает первая область памяти, а с t2 до t3 работает вторая область памяти и т.д.

При обращении к первой области памяти всегда следующий порядок работы: вначале считывается прежнее содержимое

ячейки памяти с указанным адресом, а затем по тому же адресу записывается новый отсчет сигнала с выхода АЦП 4. Считанный сигнал из первой или второй области памяти по сигналу со второго выхода генератора

б записывается в первом буферном регистре 9. При обращении ко второй области памяти блока памяти 5 считывание и запись новой информации зависит от сигнала управления с выхода элемента И 15. Управление записью/считыванием в каждой области памяти производится сигналом с выхода коммутатора 2. Сигналом управления коммутатора 2 является сигнал с первого выхода генератора 6 (фиг. 2 б). Как

видно из фиг..2 б, с момента времени ti до ti через коммутатор 2 проходит сигнал управления со второго выхода генератора 6. С момента t2 на вход блока 5 памяти коммутируется сигнал с выхода элемента И 15. При таком порядке работы коммутатора 2 при обращении к первой области памяти блока 5 памяти всегда производится вначале считывание по заданному адресу, а затем запись по тому же адресу. Так считывание в первой области памяти производится в моменты времени ti-ti , 12-12 ,...,tn-tn , а запись нового сигнала по тому же адресу производится в моменты ti -tf, ti -12 ,...tn -tn .

Пусть в момент ц на выходе АЦП 4 появился отсчет gi (Ki At) (фиг. 2 д), который одновременно поступает на выход вычита- теля 7 и вход блока памяти 5. Так как блок 5 памяти вначале сеанса был обнулен, то по адресу Ih (К At) с выхода входного блока из блока памяти 5 с момента ti до ti считывается нуль, который в момент ti записывается в первый буферный регистр 9. Из сигнала gi (Ki At) в вычитателе 7 вычитается сигнал с выхода первого 9 буферного регистра. Результат вычитания, равный 91 (Ki Аг),посту- пает на вход детектора 11, который все положительные отсчеты сигнала пропускает без изменения, а все отсчеты, имеющие отрицательный знак,превращает в положительные.

Таким образом, на выходе детектора 11 входные сигналы +gi (KAt) проходят без изменения, а входные сигналы -gi (К At) превращаются в сигналы +gi (KAt). Таким образом, сигналы на выходе детектора 11 имеют все положительные знаки. В сумматоре 8 производится сравнение двух сигналов: сигнала с выхода детектора 11 и порогового значения Мпор. Если величина сигнала /gi (К At)/ меньше порогового значения, то на выходе сумматора 8 логический нуль. Если же величина сигнала /gi (К At)/ больше порогового значения, то на выходе сумматора 8 будет логическая единица.

Так как первоначально блок памяти 5 был обнулен, то с момента ti до т.4, когда производится обучение первой области памяти блока 5 памяти под параметры канала связи (перебор всех возможных двоичных цифровых комбинаций)на выходе сумматора 8 будет всегда логическая единица.

Триггер 12 работает следующим образом.

Вначале цикла работы (моменты ti, t2, t3,...,tn) с появлением нового отсчета gi (К At) на выходе АЦП 4, производится обнуление триггера 12 строб-импульсом с управляющего выхода АЦП 4 (фиг. 2 в). В моменты

ti. ti , t3,...tn производится запись в триггер 12 выходного сигнала сумматора 8 по информационному входу. момент ti триггер 12 обнуляется, а в момент ti в триггер

12 записывается логическая единица с выхода сумматора 8. В момент t2 триггер 12 вновь обнуляется,a вновь записывается единица и т.д. Если на выходе сумматора 8 в i момент времени будет логический нуль,

то триггер 2 остается в нулевом состоянии до следующего (i+1) цикла работы. Выходной сигнал триггера 12 показан на фиг. 2 ж. Сигналом с выхода триггера 12 принудительно обнуляется счетчик 13 по R входу.

Тактовые импульсы с третьего выхода генератора 6 поступают на первый вход элемента запрета 14. Так как счетчик 13 обнуляется, то на его выходе будет логический нуль, который разрешает проходить

тактовым импульсам через элемент 14 запрета на вход счетчика 13. Если на выходе счетчика 13 будет логическая единица, то данный сигнал блокирует работу элемента запрета 14 и тем самым состояние счетчика

13 остается в таком положении до прихода очередного обнуляющего импульса с выхода триггера 12. Счетчик 13 и элемент запрета 14 являются своеобразным таймером, время срабатывания которого можно рег.улировать с помощью частоты с третьего выхода генератора 6. Если время срабатывания счетчика 13 меньше периода следования импульсов с выхода триггера 12, то на выходе счетчика 13 постоянно будет

логический нуль, тем самым блокируется работа элемента И 15. Следовательно, с момента ti до т.4 элемент И 15 закрыт и из второй области памяти блока памяти 5 постоянно считываются нули независимо от

номера ячейки памяти.

В момент времени t i на выходе вычита- теля 7 появляется отсчет gi (Ki At), который сигналом с выхода генератора (момент вре- мени t i ) переписывается во вторую буферную память 16. Аналогично отсчет дела и с другими отсчетами сигнала при работе второй области памяти блока памяти 5. Так.,в

У- ,-

момент времени t2 во второй буферный регистр 16 записывается g2 (K2 At)fa в ta - сигнал дз(Кз At). Данные сигналы превращаются вторым ЦАП 10 в аналоговую величину и выдаются потребителю. Таким образом, при первоначальном обучении устройства (обучение первой области памяти блока памяти 5) возникают так называемые эхо-сигналы, которые на следующих тактовых интервалах компенсируются.

Пусть в момент t4 на выходе входного 1 блока появляется сигнал Ui (K4 At), который пройдя 3 ЦАП, АЦП 4, превращается в сигнал gi (K4 At). Из первой области памяти блока памяти 5 по адресу Ui (К At) выводится прежнее содержимое gi (Ki At) и в момент t4 переписывается в буферный регистр 9. В вычитателе 7 производится вычитание двух сигналов: из сигнала gi (K4 At) вычитается сигнал gi(K/At). Данные сигналы по существу являются откликами канала связи на одинаковую цифровую комбинацию Ui (К At), но взятые в два соседних момента времени. Результат вычитания будет равен:

NI (Кд At) gi (K4 At) - gi (Ki At)0. (2)

По закону относительности Ni (K4 At) 0, так как параметры канала связи мало изменяются на соседних тактовых интервалах.

Следовательно, в момент Т4 на выходе сумматора 8 будет логический нуль, который в t4 переписывается в триггер 12. Обнуление счетчика 13 в момент t4 не происходит. Спустя некоторый промежуток времени t выдержки (см. фиг. 2 е) счетчик 13 достигает максимально-возможного значения и на его выходе появится логическая единица. Данный выходной сигнал счетчика 13 закрывает элемент запрета 14 и открывает элемент И 15. Тактовые импульсы со второго выхода генератора 6 с момента t4 до t5 (см. фиг. 2 а и фиг. 2 и) проходит элемент И 15, коммутатор 2 и поступают на управляющий вход режима считывание/запись блока памяти 5 (фиг. 2 к). Следовательно, с момента t4 до т.5 режим работы второй области памяти полностью соответствует режиму работы первой области памяти: вначале по адресу Ui (К At) производится считывание прежнего содержимого, т.е. нуля, а затем запись нового отсчета gi (K4 At) по тому же адресу. Таким образом, из первой области памяти вначале считывается по адресу Ui (К At) сигнал gi (Ki At), а затем записывается сигнал gi (K4 At), а из второй области памяти по тому же адресу вначале считывается нуль, а затем записывается gi (К4 At). Первая область памяти блока 5 в совокупности с вычитателем 7, детектором 11, сумматором 8, триггером 12, счетчиком 13, элементом запрета 14 и элементом И 15 является своеобразным выделителем отсутствия сигналов противоположной стороны. При отсутствии сигналов противоположной стороны при работе первой области памяти на выходе вычитателя 7 наблюдается сигнал, близкий к нулевому, а в случае присутствия сигналов противоположной стороны на выходе вычитателя 7 будет разность двух

0

5

0

5

0

5

0

5

0

5

значений принимаемого сигнала на соседних тактовых интервалах. В случае отсутствия принимаемого сигнала производится принудительное переобучение второй области памяти: запись значений счетчика канала связи на соответствующую цифровую комбинацию, поступающую на вход первого

3ЦАП. В случае присутствия сигналов противоположной стороны запись счетчика канала связи во вторую область памяти блокируется и производится только считывание информации из второй области памяти блока памяти 5. Пусть в момент ts на выходе входного 1 блока вновь появился отсчет Ui (KsAt). Пусть из канала связи в это время поступает сигнал y(ts). На выходе АЦП

4наблюдаем сумму двух сигналов gi (Ks At)+ + yi (K5 At).

Из первой области памяти блока памяти

5по адресу Ui (К At) выводится прежнее содержимое gi (K4 At). На выходе вычитателя 7 будет сигнал, равный

Ni (K5 At) 91 (Ks tA) + yi(K5At )-gi(K4At) yi(KsAt)(3)

В первую область блока памяти по адресу Ui (KAt) записывается gi (KsAt) + yi (Ks At). Так значение m (Ks At) sO, то данный сигнал, пройдя детектор 11, сумматор 8 приводит к срабатыванию в момент ts триггера 12, который принудительно обнуляет счетчик 13. Блокируется элемент И 15 и вторая область памяти 5 на данном цикле работы будет только считывать информацию из ячейки памяти с адресом Ui (К At).

В результате, при работе второй области памяти на выходе вычитателя 7 будет U (KsAt) gi (K5 At) + yi (Ks At) -gi(K4At) yi(K5At)(4)

Если на выходе входного 1 блока появляются в 6 цикле работы сигналы U2 (Кб At) или Us (Ke At), то процесс работы не будет отличаться от описанного выше.

Пусть на выходе входного блока 1 в 6 цикле работы вновь появляется отсчет, равный Ui (KeAt), а в это время из канала связи поступает сигнал у (te).

На выходе АЦП 4 будет сумма двух сигналов

gi(K6At)fy2(K6At).

При работе первой области памяти блока памяти 5 будет сигнал

Mi (Ke At) gi (Кб At) + yi (K6 At) - g 1 (К5 At) -у (Ks At) У2 (K6 At) - у 1 (К5Д t)

(5)

В этом случае значение Mi (Кб At) 0. Сле- довательнсцэлемент И 15 останется закрытым, а в первую область памяти по адресу Ui (KAt) записывается значение gi (KeAt) + +У2 (Кб At). При работе второй области памяти на выходе вычитателя 7 будет иметь Li (Кб At) g 1 (KeA t) + У2 (Кб At) -g(K4At) y2(K6At)(6)

Справедливость формул (3-6) объясняется по закону относительности, т.е.

gi (Ki At) «gi (К4 At) «gi (Ks At)

«gi(K6At)(7)

Аналогично протекают процессы на других циклах работы устройства. Значение L(Ki At) далее в ti+i момент времени записывается в буферный регистр 16. превращающее вторым 10 ЦАП в аналоговую величину и выдаются потребителю. Так значение Li (Ks At) yi (KsAt) записывается в буферный регистр 16 по сигналу с первого входа генератора с началом б цикла работы. Значение 1.2 (КеДт.) уа (Кб At) фиксируется в начале 7 цикла работы и т.д.

Таким образом, в одной полосе частот произведено разделение двух направлений передачи и адаптация к параметрам канала связи.

Формула изобретения Устройство для разделения направлений передачи и приема содержащее входной блок, последовательно соединенные первый цифроаналоговый преобразователь, аналого-цифровой преобразователь и блок памяти, а также вычитатель, первый вход которого соединен с первым выходом аналого-цифрового преобразователя, сумматор, второй цифроаналоговый преобра0

5

0

5

0

5

0

зователь, коммутатор и генератор, первый выход которого подключен к синхронизирующим входам входного блока, аналого-цифрового преобразователя и блока памяти, второй вход которого объединен с входом первого цифроаналогового преобразователя, отличающееся тем, что, с целью повышения помехоустойчивости, введены детектор, элемент запрета, первый и второй буферные регистры и последовательно соединенные триггер, счетчик, элемент И, второй вход которого объединен с управляющим входом коммутатора и синхронизирующим входом первого буферного регистра и подключен к второму входу генератора, к первому выходу которого подключены первый вход коммутатора, синхронизирующий вход второго буферного регистра и первый входтриггера к второму входу которого подключен второй выход аналого-цифрового преобразователя, выход входного блока соединен с вторым входом блока памяти, к третьему входу которого подключен выход коммутатора, второй вход которого соединен с выходом элемента И, первый вход которого объединен с первым входом элемента запрета, выход которого подключен к второму входу счетчика, а второй вход элемента запрета соединен с третьим выходом генератора, причем выход блока памяти через первый буферный регистр подключен к второму входу вычитателя, выход которого через второй буферный регистр подключен к входу второго цифроаналогового преобразователя и через детектор подключен к первому входу сумматора, второй вход которого подключен к шине порогового напряжения, а выход сумматора соединен с третьим входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1984 |

|

SU1223373A2 |

| Устройство для разделения речевых сигналов | 1989 |

|

SU1626393A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| Эхокомпенсатор | 1990 |

|

SU1707766A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Устройство сжатия аналоговой информации | 1988 |

|

SU1709368A1 |

Изобретение относится к устройствам для разделения направлений передачи и приема и может быть использовано в телефонии. Цель - повышение помехоустойчивости - достигается за счет компенсации сигналов непрерывной подстройки своих параметров под изменяющиеся параметры канала связи в дуплексном режиме работы, 2 ил,

4

i so

-VJ

(Л2

Пч

S -Э

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-05-15—Публикация

1989-12-21—Подача