формирователь 5 адреса, два блока 6, 10 памяти, reHepatop 7 управляющих импульсов, вычитатель 8, сумматор 9, блок 12 упрайления (ВУ), состоящий из источника 13 опорного напряжения, формирователя 14 интервала адаптации, накапливающего сумматора 15, триггера 16, двух элеИзобретение относится к технике электросвязи, может использоваться в системах передачи данных для разделения направлений передачи и является усовершенствованием устройства по основному авт.св. №1133675.

Цель изобретения - повышение помехоустойчивости при изменяющихся параметрах канала связи.

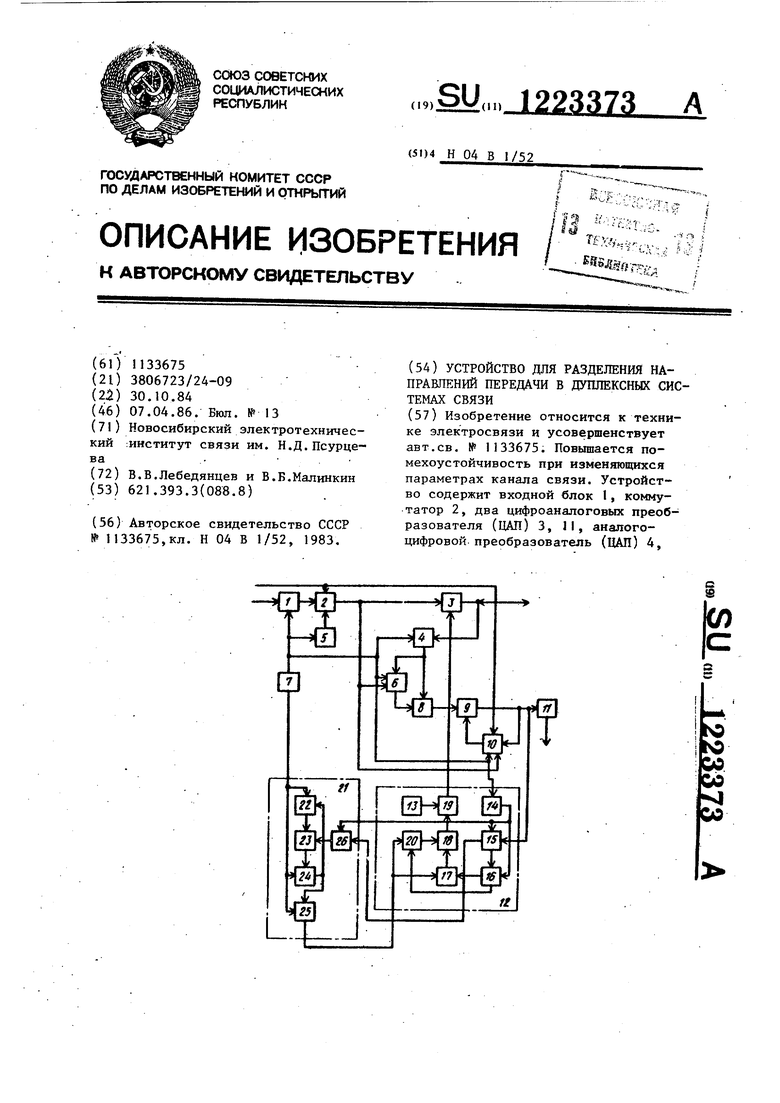

На чертеже представлена струк- ; турная электрическая схема предлагаемого устройства.

Устройство для разделения направлений передачи в дуплексных системах связи содержит входной блок 1, коммутатор 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, формирователь 5 адреса, первый блок 6 памяти, генератор 7 управляющих импульсов, вычитатель 8, сумматор 9, второй блок 10 памяти, второй цифроаналоговый преобразователь 11, блок 12 управления, состоящий из источника 13-опорного напряжения, формирователя 14 интервала адаптации, накапливающего сумматора 15, триггера 16, первого элемента И 17, реверсивного счетчика 18, цифроаналогового преобразователя 19 и второго элемента И 20, адаптив- ньй делитель 21 частоты, состоящий из счетчика 22, порогового блока 23, триггера 24, элемента ИЛИ 25 и блока 26 буферной памяти.

Устройство работает следующим образом.

Работу предлагаемого устройства условно можно разбить на процесс предварительной адаптации и процесс адаптивного разделения Ааправлений передачи сигналов.

1223373

ментов И 17, 20, реверсивного счетчика 18, ЦАП 19, адаптивньй делитель частоты 21, состоящий из счетчика 22, порогового блока 23, триггера 24, элемента ИЛИ 25 и блока 26 буферной памяти. Цель достигается введением делителя АДЧ 21 и БУ 12. 2 з.п. ф-лы, 1 ил.

Процесс предварительной адаптации не отличается от процесса адаптации в известном устройстве h заключается в следующем. -Управляющий сигнал от конечного оборудования данных (не показан), подаваемый автоматически или вручную, поступает на коммутатор 2 и одновременно на второй блок 10 памяти. Данный сигнал обнуляет второй блок 10 памяти и подключает выход формирователя 5 адреса к входу первого цифроаналогового преобразователя 3 через коммутатор 2. Формирователь 5 адреса в цифровой форме

- выдает на вход первого цифроаналогового преобразователя 3 все используемые цифровые комбинации: a,a,..a. Эти цифровые комбинации превращаются первым цифроаналоговым .преобра- зователём 3 в напряжения и,,,,... Uj,, которые подаются в .канал связи. Одновременно указанные напряжения преобразуются аналого-цифровым преобразователем 4 в соответствующие цифровые комбинации U(K,,ut), U.(KjAt),...,и„() и записьшаются - в первый блок 6 памяти, причем по адросу а, записывается U(),no адресу а - UjCKjAt), по адресу а„ - U(), где К:; - номер текущего отсчета. На этом процесс предварительной адаптации заканчивается и по (Сигналу от оконечного оборудования - данных коммутатор 2 подключает выход входного блока к входу первого циф5 роаналогового преобразователя 3. Одновременно снимается обнуляющий сигнал с второго блока 10 памяти. Причем в процессе предварительной адаптации сигналы противополож ной стороны должны отсутствовать.

0

Процесс адаптивного разделения предачи можно пояснить следующим образом.

Входной блок 1 преобразует входящий сигнал U;(t) в одну из кодовы комбинаций aj. Предположим, например, что первый момент времени входной блок I преобразует входящий сигнал U(t) в первую цифровую ком- бинахщю а . Эта цифровая комбинация превращается первым цифроаналоговым преобразователем 3 в сигнал U , который подается в сторону противоположной станции. Одновременно из канала связи поступает сигнал У , причем на входе аналого-цифрового преобразователя 4 присутствует суммарный сигнал Г, и,+У, , которьй преобразуется аналого-цифровым преобразователем 4 в цифровую форму

ot:(K,,, At)U,(K,,t)-Hy,(K,,ut)(l.)

и подается на первый вход вычцтате- ля 8 (где п - номер предыдущего отсчета). Так как в сторону противоположной станции передается цифровая комбинация а,, то из первого блока 6 памяти выводится содержимое а яч,ейки памяти U () и подается н второй вход вычитателя 8. На выходе вычитателя 8 результирующий сигнал имеет вид

М(К,, 4t)«, (Kn,,ut)-U,(K, 4t) У, (K,,,ut)+u,,(2)

где Д| и,(К„+, ut)- - погрешность -U, (к,it) компенсации.

Причем U,(Kn+,it) и и,(к,At) -; сигналы, характеризующие передачу цифровой комбинации а, в разные (nft i K,ut) моменты времени. При постоянных параметрах канала связи значения Л i на выходе татеЛя 8 имеют разные значения, не превышающие шага квантования аналого-цифрового преобразователя 4, и разные знаки.

Результат вычитания с выхода вычитателя 8 складывают с содержимым ячейки памяти второго блока 10 памяти в сумматоре 9, тем самым восстанавливая форму принимаемого сигнала y{t), который затем преобразуется во втором цифроаналоговом преобразователе 1 I. Так, после первого такта на выходе сумматора 9 будет величина

D(K,,ut)M,(K,,,it)y,(K.,6tU

+ Д;.(3)

После m тактов (где m - количество тактов с момента начала работы) на

выходе сумматора 9 будет величина

m

D(K,,ut)yHK,,ut)+Z:u,-. (h

тill

Величина .51 Л; может быть близка fQ к нулю при постоянных параметрах канала либо отличаться от нуля при изменяющихся параметрах канала свя- яи.

Для устранения сигнала недоком- , пенсации служит блок 12 управления и адаптивный делитель 21 частоты. Блок 12 управления выносит решение о наличии на входе приемника сигнала недокомпенсации и дает управляющий Q сигнал для новых условий передачи соответствующим изменениям амплитуды выходного сигнала передатчика.

С этой целью сигналы D;(K ut) подают в накапливающий сумматор 15, 5 на выходе которого накапливается сигнал с величиной, равной

г(ч.(;чь.

0: р.(.ь|г/иЬч, .,«

W . где; гГ - определяет ошибку недо- , ° компенсации; S- д. определяет ошибку шумов j«t i«i квантования; L определяет ошибку, порож-. -t7 J/ i дающую принимаемым сигАналазируя выражение (5) для большого значения (), нетруд- - но видеть, что знак суммы Z(t) оп I л

-

ределяется знаком величины i- uW;,

IJM J . .

.которая в свою очередь зависит от

знака сигнала недокомпеисации. Таким образом, из-за случайного характера изменения зиака и величины принимаемого сигнала и шумов квантования их. среднее значение близко . Так как отсчеты сигнала -uWj - имеют . одинаковый знак, то при больших N 0 . i ti

s величина . AWj существенно больше .

значений йёрвых двух слагаемых. Следовательно, знак сигнала Z(t) определяется знаком сигнала недокомпенсации, которая, в свою очередь, определяется направлением измеиения параметров канала связи, например модуля входного сопротивления.

5

$1

Интервал адаптации (величину N) задает формирователь 14 интервала адаптации, по окончании которого

I . :

знак величины Sgn с первого Y. 1

выхода накапливаюи еГо сумматора 15 фиксируется в триггере 16, а абсолют

значение

н

.SIuW; Г

J фиксируется в

блоке 26 буферной памяти для управления коэффициентом деления адаптивного делителя 21 частоты.

Сигналы с выхода триггера 16 (логические 1 или о) открывают первый элемент И 17 либо второй элемент И 20 и пропускают на один из входов реверсивного счетчика 18 импульсы с выхода адаптивного делителя 21 частоты. Эти импульсы изменяют состояние реверсивного счетчика 18, тем самым изменяется код подаваемый на вход цифроаналогового преобразователя 19. Последний преобразователь 19 производит умножение опорного сигнала с выхода источника 13 опорного напряжения и цифровой комбинацией с выхода реверсивного счетчика 18. Выходной сигнал цифроаналогового преобразователя 19, который является опорным сигналом для первого цифроаналогового преобразователя 3, изменяет амплитуду передаваемых отсчетов в противофазе изменения параметров канала связи. К примеру, если входное сопротивление ка ,N

нала связи увеличилось, то

имеет положительный знак. Фиксируется логическая 1 в триггере 16, тем самым открьгоается первый элемент И 17 и тактовые импульсы проходят на (-) вход реверсивного счетчика 18, в результате этого выходной сигнал цифроаналогового преобразователя 19 уменьшается, уменьшается опорное напряжение первого цифроаналогового преобразователя

3. и выходные сигналы уменьшаются

к

до тех пор, пока величина

.

Г- J rt становится равной О.

Для увеличения скорости сходимости процесса компенсации сигналов ошибки служит адаптивний делитель 21 частоты. Выходная частота адап223373 6

тивног о делителя 21 частоты определяется как

1-fJ..W,|

(б)

например, если

N

10

.iWj|-20,Toi,,,,-i,,(l-,

а если

N

il-4.,, nr/2,

где

ЪГзаданное значение тактовой частоты.

Таким образом, чем больше величина недокомпенсации, тем выше тактовая частота на выходе адаптивного делителя 21 частоты, что позволяет сократить время адаптации.

Поясним подробнее эго работу. Тактовые импульсы с выхода генератора 7 поступают на вход счетчика 22, элемент ИЖ 25. Триггер 24 находится в исходном (нулевом) состоянии. В блоке 26 буферной памяти

- - зафиксирована величина

IftW

Пороговый блок 23 сравнивает состоясчетчика 22 и величины

1 г

N ,. -bW

С выхода блока 26 буферной памяти. Как только состояние счетчика 22 достигает величины состояния блока 26 буферной памяти, на выходе порогового блока 23 появляется сигнал логической единицы, которая очередным (К+1)-м тактом записывается в триггер 24. Триггер 24 обнуляет- счетчик 22, в результате чего попадает сигнал с выхода порогового блока 23, и очередным (К+2)-м тактом возвращается в исходное состояние. Таким образом, триггер 24 находится два такта f j в.единичном состоянии

I W - , на интервале iVJ, и тем самым заI J4

прещает прохождение f на выход адаптивного делителя 21 частоты.

Формула изобретения

1. Устройство для разделения направлений передачи в дуплексных системах связи по авт.св. № 1133675, отличающееся тем, что.

с целью повышения помехоустойчивости устройства при изменяющихся параметрах канала связи, в него введены адаптивный делитель частоты и блок управления, первый, второй и третий выходы которого подключены -соответст венно к дополнительному входу первого цифроаналогового преобразователя и к первому и второму входам адаптивного делителя частоты, выход которого соединен с первым входом блока управления, второй и третий входы которого соединены соответственно с выходом сумматора и выходом генератора управляющих импульсов, кото рый подключен к третьему входу адаптивного делителя частоты.

2. Устройство по п. I, отличающееся тем, что адаптивный делитель частоты содержит блок буферной памяти и последовательно ссгединенные счетчик, пороговый блок, триггер и элемент ИЛИ, второй вход которого соединен с первым входом счетчика, к второму входу которого подключен выход триггера, второй вход которого соединен с вторым вхоом элемента ИЛИ, выход которого явяется выходом адаптивного делителя частоты, первым, вторым и третьим ходами которого являются соответстенно входы блока буферной памяти.

Составитель А.Москевич Редактор О.Бугир Техред О.Гортвай

Заказ 1725/59 Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35. Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

23373 8

выход которого подключен к второму входу порогового блока, и первый вход счетчика.

, 3. Устройство по п. 1, отличающееся тем, что блок управления содержит последовательно соединенные источник опорного напряжения и цифроаналоговый преобра- 10 зователь, первый элемент И и последовательно соединенные формирователь интервала адаптации, накаплива-. ющий сумматор, триггер, второй элемент И и реверсивный счетчик, второй 15 вход и выход которого соединены соответственно с выходом первого элемента И, к первому входу которого подключен второй выход триггера, и с вторым входом цифроаналогового

20 преобразователя, выход которого, выход формирователя интервала адаптации и второй выход накапливающего сумматора являются соответствен- i но первым, вторьи и третьим выходами

25 : блока управления, nepBwi, вторым и третьим входами которого являются соответственно второй вход первого элемента И, который соединен с вторым входом второго элемента И, вто -

30 рой вход накапливающего уммйгора и вход формирователя интервала адап- :тации. .:

Корректор Г.Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

| Устройство для усреднения сигналов | 1985 |

|

SU1322316A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Способ адаптивной временной дискретизации и устройство для его осуществления | 1983 |

|

SU1095390A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

Изобретение относится к технике электросвязи и усовершенствует авт.св. № 1133675. Повышается помехоустойчивость при изменяющихся параметрах канала связи. Устройство содержит входной блок 1, коммутатор 2, два цифроаналоговых преобразователя (ЦАП) 3, |, аналого- цифровой преобразователь (ЦАП) 4,

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-07—Публикация

1984-10-30—Подача