1

Изобретение относится к области автоматики и вычислительной техники. Известно частотно-импульсное множнтельио-делительное устройство, содержащее счетчики, регистр, триггеры, элементы И и ИЛИ.

Иедостатками известного устройства являются ннзкая точность вычислений и ограниченный диапазон изменения входных частот и результирующей частоты.

Наиболее близким техническим решением к предложенному является устройство, содержащее первый счетчик, разрядные выходы которого иодключены к соответетвующим входам региетра через первую грунпу элементов И, вторые входы элементов И первой группы через первый элемент задержки подключены к управляющему входу регистра, который через второй элемент задержкн подключен к первому входу первого счетчика, и непоередственно к входу первого триггера, к выходу первого элемента И и через третий элемент задержки - к входу второго триггера, выход которого нодключен к первому входу второго элемента И, выход которого подключен к входу третьего триггера, нулевой выход которого подключен к первому входу третьего элемента И, второй вход которого подключен к первому входу устройства и к первому входу первого элемента И, второй вход которого подключен к второму входу

устройства и к первому входу четвертого элемента И, второй вход которого подключен к единичному выходу третьего триггера, третий вход четвертого элемента И подключен к

третьему входу устройства и к первому входу пятого элемента И. второй вход которого подключен к выходу четвертого триггера и к первому входу шеетого элемента И. второй вход которого подключен к четвертому входу устройства и к первым входам седьмого и восьмого элементов И, выход седьмого элемента И через четвертый элемент задержки подключен к входу четвертого триггера, второй вход седьмого элемента И подключен к выходу

первого триггера и к второму входу восьмого элемента И, выход которого подключен к второму входу нервого счетчнка, разрядные выходы регистра подключены к первым входам элементов И второй грунпы, выходы которых

подключены к соответствующим входам второго счетчика, вторые входы элементов И второй грзнпы подключены к выходу пятого элемента задержкп, выход шестого элемента И подключен ко пятого триггера, выход

которого подключен к третьему входу еедьмого элемента И, выход нятого элемента И нодключен к первому входу элемента ИЛИ.

Недостатками прототипа являются ограниченный диапазон п низкая точность вычислеНИИ.

Целью изобретения является расширение диапазона умножения и повышение точности.

Поставленная цель достигается тем, что в устройство введены блок определения величины управляюших сигналов, блок регулировки задержки, блок сдвига фазы, дополнительный элемент I-i, дополнительные триггер и элемент задержки, вход которого иодключсн к четвертому входу устройства, а выход иодключен к единичному входу донолнительного триггера, выход которого подключен к третьему входу восьмого элемента И, нулевой вход донолннтсльного триггера через второй элемент задержки подключен к нервому входу первого триггера, второй вход элемента ИЛИ подключен к выходу блока регулировки задержки, к иервому входу блока сдвига фазы, второй вход которого подключен к выходу четвертого элемента И, а выход подключен к управляющему входу второго счетчика и дополнительного элемента И, входы которого подключены к разрядным выходам второго счетчика, а выход подключен к иервому входу блока регулировки задержки и к входу иятого элемента задержки, второй вход блока регулировки задержки подключен к выходу блока определения величины управляющих сигналов, нервы вход которого подключен к четвертому входу устройства, второй вход блока определения велпчтиил управлякяних сигналов подключен к выходу первого элемента И, а третий вход подключен к третьему входу уетройетва, выход элемента ИЛИ является выходом устройства.

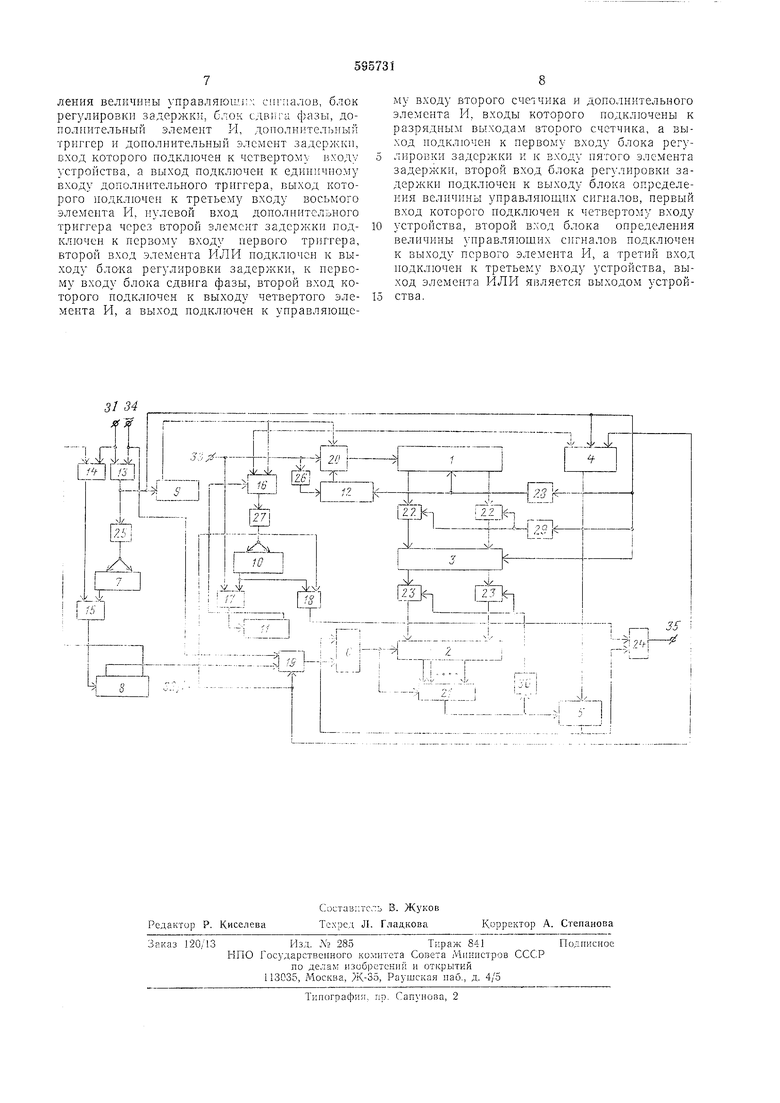

Схема устройства представлеиа на чертеже. Она содержит счетчики 1, 2, регистр 3, блок определения величины управляющих сигналов 4, блок регулировки задержки 5, блок сдвига фазы 6, триггеры 7-11, дополнительны; триггер 12, элементы И 13-20, дополнительный элемент И 21, группы элементов И 22, 23, элемент ИЛИ 24, элемент задержки 25, дополнительный элемент задержки 26, элементы задержки 27-30, входы устройства 31-34, выход устройства 35.

Входные сигналы иервой иоследовательностн с частотой следования FI, характеризующие одни из еомножителей, подаются на вход 3. Сигналы с частотой следования F3, характеризуюи1,ие другой сомножитель, подаются на вход 32.

Сигналы с частото следования /2, характер изуюигис делитель, нодаютея иа вхо;, 32. Далее сигиалы последовательно с чаетотой подаются на входы элементов И 13 и 14, сигналы с частотой F2 - на входы элементов И 16, 17, 20 и на вход элемента задержки 26 и сигналы с частотой F3 - на входы элементов И 18 и 19. Иаряду с этим все три носледовательиости иодаются иа входы блока 4. В исходиом состоянии счетчики 1, 2, регистр 3 и триггеры обнулены.

На вход 34 нодается сигиа-л разрещения. При этом иервый импульс, подаваемый на вчод 31, проходит через элемент PI 13 и переВОДИТ триггер 9 в единичное состояние. В результате открывается элемент И 20 и на вход счетчика 1 начинают проходить сигналы, характеризующие делитель с частотой , которые наканлнпаютея в счетчике 1 до момента ноетуплення следуюи. ходно:о сшпала на вход 31. Следует отмот1гг,, что подача одного пз имп л1зсов частоты ;ia вход ч тчика 1 занрещается. Это осуществляется с 11смощь;о триггера 12, элемента задержкн 23 и элемента И 20. Сигнал из последовательности каждый раз устанавливает триггер 12 в иулевое состояние, запирая элемент И 20. При этом нервый после иодачи сигнал а 1;з иоелсдозательности FI сигиал частоты F2 не нроходнт через элемент И 20, а проходя через элемент задержки 26, устанавливает триггер 12 в единичное состояние. Все последующие сигналы частоты 2 проходят иа вход счетчика I.

Одновременно с подаче си нала на вход 31 блок 4 начинает «нределснис унравля 0щего сигнала юнравк периода выходиого сигнала. С поступлением следующего (второго после подач сигнала разрешення) 1мпульса ннформання, накопленная в счетчике 1, Передается через элементы И 22 н регнстр 3, где запом нается, а счетч 1к 1 обнуляется.

Иеобход1 мы временно сдвиг между моментам подачи И формани об1 улениел: счетчика 1 осу1иест1 лястея с элементов задержки 28 i 29. Далее иродесс повторяется.

С нр 1ходом каждого нослсду още 0 нмнульса из последовательности с частотой следова 1ия он осуществляет обнулен е рег стра 3 и иередачу нако 1ленной в счетчике 1 информации в регистр 3, а также обнуление счетчика 1. Иеобход1 мая задержка в подаче сигналов из ослсдоватсльност F3 иа вход счетч 1ка 2 в данном случае оеуществлястся с номощью триггеров 7, 8 элеме}ггов И 14, 15 элеме 1та задер/кк 1 22. Иослс одачи сигиала разреще ия на вход 34 иервый сигнал из иос.тедователь юст и с частотой / 1 проходит ia выход элементов И 13, 14. При этом с выхода элемента И 13 он ностунает через элемент задержки 25 на вход 7, 1 ереводя его 13 нулевого в ед1 ничное соСТОЯ Ие.

Очевидно, что iipi этом с улемеита И 14 по нрох(.дпт ia вход элемента И 15, так как отпирам1ний с триггера 7 выдается на его с задержкой за счет элемента задержки 25. При ноступле ; ; ; следу ощего сигнала иа вход 31 с выхода э.леме1гга И 14 нроходит иа выход элемента И 15, переводя триггер 8 в единичное состоя iiie. В результате (;тся И 19 а вход счетч :ка 2 через блок сдвига фазы 6 начинают одаваться .мпульсы с частотой следования F3.

С переводом триггера 8 в един1;чное состояние элемент И 14 запираетея для сигналов, одаваемых на вход 31. Для юлучення информации о результате в течение первого периода частоты F служат элементы И 16, 17, 18, триггеры 10, 11 и элемент задержки 27. После подачи сигнала разрешения на вход 34 прохождения импульса с входа 31 через элемент И 13 и перевода триггера 9 в единичное состояние на выход элемента И 16 проходит сигнал последовательности с частотой F2 с входа 33.

Одновременно импульс с входа 33 подается на вход элемента И 17. С выхода элемента И 16 сигнал через элемент задержки 27 проходит на счетный вход триггера 10, переводя его в единичное состояние. При этом открывается элемент И 18 и па его выход проходят сигналы с входа 32 и далее через элемент ИЛИ 24 - на выходной вход 35, образуя первые сигналы результатов. При поступлении следующего сигнала с входа 33 он проходит через элемент И 17, в результате чего триггер 11 переводится в единичное состояние, а при подаче сн-иала на счетный вход триггера 10 последний переводится в нулевое состояние. При этом за 1ираются элементы И 16, 17 и 18. В результате выдача импульсов с входа 32 прекращается, что необходимо для нормального функционирования устройства.

Выходные сигиалы пересчета со счетчика 2 формируются па выходе многовходового элемента И 21, подключенного к разрядным выходам счетчика 2 таким образом, что ои открывается для входных сигпалов с частотой F3 лишь в момент достижения в счетчике 2 единичной ннформации.

В этот момент появляется на его выходе сигнал пересчета. Указанные сигналы подаются на вход блока регулировки задержки 5 и через элемент задержки 30 - на управляющие входы элементов И группы 23. В результате этого информация, запомненная в регистре 3, периодическ передастся через элементы И груипы 23 в счетчик 2, образуя его исходиую установку, а также осуществляется задер кка сигнала, вырабагываемая в блоке 4. Задержанные сигналы с выхода блока регулировки задержки 5 пОхО.аются на один нз входов блока сдвига фазы 6 и через элемеит ПЛИ 24 - на выход 35 устройства. Па выходе блока сдвига фазы 6 вырабатываются нрн иодачс снгналов с выхода блока регулнровки задержки сдвинутые по фазе сигналы с частотой F3 таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока регулировки задержки. В этом случае на входе блока 5 имеют место сигналы, период которых изменен на величину, вырабатываемую на выходе блока 4.

В зависимости от величины исходной уставки иа выходе элемента И 21 устаиавлпвается вполне определенная частота. При этом каждый последующий и.М1тульс частоты / осуществляет иериодическнй сброс старой ииформации в регистре 3 и запись новой информации.

Таким образом, из изложенного следует, что предложенное устройство обесиечивает

существецное noBbiHieniie точности при одновременно% расширении диапазона изменения входных и выходной частоты.

Это обусловлено тем, что в устройстве осуществляется коррекция периода выходного сигнала на величину, зависящую от соотнощення АГнач н АГкои. При ЭТОМ сохраняется высокая точность при широком изменении частот и она теперь уже не зависит от из.менения частот. Поэтому н имеет место высокая точность при широком диапазоне изменения частот.

Формула изобретения

Частотио-импульсное множительно-дслительное устройство, содержащее нервый счетчик, разрядные выходы которого подключены к соответствующим входам регистра через

первую груииу элементов П, вторые входы элементов И первой грунпы через первый элемент задержки подключены к управляющему входу регистра, который через второй элемент задержки подключен к первому входу первого

счетчика, и непосредственно к входу первого

триггера, к .выходу первого элемента И и через

третий элемент задержки - к входу второго

триггера, выход которого подключен к первому

входу второго элемента И, выход которого

подключен к входу третьего триггера, нулевой выход которого подключен к первому входу третьего элемента II, второй вход которого подключен к первому входу устройства и к первому входу первого элемента И, второй

вход которого подключен к второму входу уетройства и к иервому входу четвертого элемеита М, второй вход которого подключен к единичному выходу третьего триггера, третий вход четвертого элемента II подключен к

третьему входу устройства и к иервому входу иятого элемента П, второй вход которого подключен к выходу чстБ ;-ртого триггера и к первому входу шестого элемента П, второй вход которого подключен к четвертому устройства н к нервым входам седьмого и восьмого элементов П, выход седьмого элемента И через четвертый элемент задержки подключен к входу четвертого триггера, второй вход седьмого элемента II подключен к выХОД} первого триггера н к второму входу восьмого элемента П, выход которого подключен к второму входу первого счетчика, разрядные выходы регистра подключены к первых; входам элементов II второй группы, выходы которых подключены к соответствующпм входам второго счетчика, вторые входы элементов И второй группы подключены к выходу пятого элемента задержки, выход шестого элемента П подключен ко входу пятого T iiirrcpa,

выход которого подключен к третьему входу седь:,1ого элемента П, выход пятого элемента М подключен к первому входу элемента I1JIM, отлнчающееся тем, что, с целью расширения дпаназона умножешгя п повышения

точности, в устройство введены блок онределения величины управляют);:-: сигналов, олск регулировки задержки, блок фазы, дополнительный элемент И, дополнительный триггер п донолиительный элемент задержки, вход которого подключен к четвертому Г ход;/ уетройства, а выход подключен к единичному входу дополнительного триггера, выход которого подключен к третьему входу воеьмого элемента И, нулевой вход дополннтельного триггера через второй элемент задержки подключен к первому входу первого триггера, второй вход элемента ИЛИ нодключен к выходу блока регулировки задержки, к первому входу блока сдвига фазы, второй вход которого подключен к выходу четвертого элемента И, а выход подключен к управляюп ему входу второго ечетчика и дополнительного элемента И, входы которого подключены к разрядным выходам второго ечетчика, а выход подключен к первому входу блока регулировки задержки и к входу пятого элемента задержки, второй вход блока регулировки задержки подключен к выходу блока определения величины управляющих еигналов, первый вход которого подключен к четвертому входу уетройства, второй вход блока оиределеиия величины унравляюших сигналов подключен к выходу первого элемента И, а третий вход подключен к третьему входу )етройства, выход элемента ИЛИ Я15ляется выходом устройства.

Авторы

Даты

1978-02-28—Публикация

1975-12-22—Подача