Изобретение относится к приборостроению и может быть использовано при построении долговременных запоминающих устройств на подвижном носителе.

Известны устройства записи-воспроизведения, содержащие накопитель на магнитном носителе, блок записи и воспроизведения цифровой информации, сумматор простробированных воспроизведенных импульсов и формирователь сигнала ошибки.

Однако они обладают низкой технологичностью эксплуатации, характеризуемой повышенной затратой мощности источника питания при осуществлении в процессе штангой работы, длительного хранения записанной информации до момента ее воспроизведения, невозможностью воспроизве- дения с высокой достоверностью записанной ранее информации на другом комплекте аналогичного устройства и отсутствием возможности создания банка хранения данных ошибок информации, индексированных по номеру носителя памяти и дате записи информации, что бывает часто необходимо на практике.

Известны также устройства записи-воспроизведения цифровой информации с использованием корректирующих кодов, которые образуются добавлением некоторого количества дополнительных корректирующих разрядов к информационным разрядам, содержащие блоки промежуточного запоминания информации, блоки формирования информационных разрядов выходного кода, блоки автоматического обнаружения и исправления определенного количества ошибок (Коган Б. С. и др. Запоминающие устройства большой емкости. М. "Энергия", 1968, с, 307).

Недостатками этих устройств являются также низкая технологичность эксплуатации, характеризуемая вышеперечисленными признаками, и надежность работы при аварийном отключении основного источника питания.

Известны также устройства записи-воспроизведения цифровой информации от нескольких источников с контрольными разрядами на четность для каждой из ее частей, содержащие накопитель на подвижном носителе, блок записи и воспроизведения цифровой информации, сопряженный с накопителем, блок буферной памяти, блок контроля информации по частям (Патент США N 3569934, кл. 340-146.1, 1971).

Недостатками этих устройств также являются низкая технологичность эксплуатации.

Наиболее близким по технической сущности и достигаемому эффекту является устройство записи-воспроизведения цифровой информации (авт. св. N 1721630, N 4817522/24-10/004723, 1990), содержащее накопитель на подвижном носителе, блок записи и воспроизведения цифровой информации, блок буферной памяти, элементы И, ИЛИ первый, второй и третий блоки памяти, реверсивный счетчик, компараторы, блок управления, регистры памяти, триггеры, селектор сигналов, формирователи сигналов, блок управления приводом.

Недостатками известного технического решения являются низкая технологичность эксплуатации, обусловленная повышенной затратой мощности напряжения питания при длительном хранении записанной информации до момента ее воспроизведения, с высокой достоверностью записанной ранее информации на другом комплекте аналогичного устройства и отсутствием возможности создания банка хранения данных ошибок информации, индексированных по номеру памяти на подвижном носителе и дате записи информации, что бывает часто необходимо на практике, а также низкой надежностью работы устройства при аварийном отключении источника питания.

Целью изобретения является повышение технологичности эксплуатации.

Кроме того повышение надежности работы устройства при аварийном отключении источника напряжения питания.

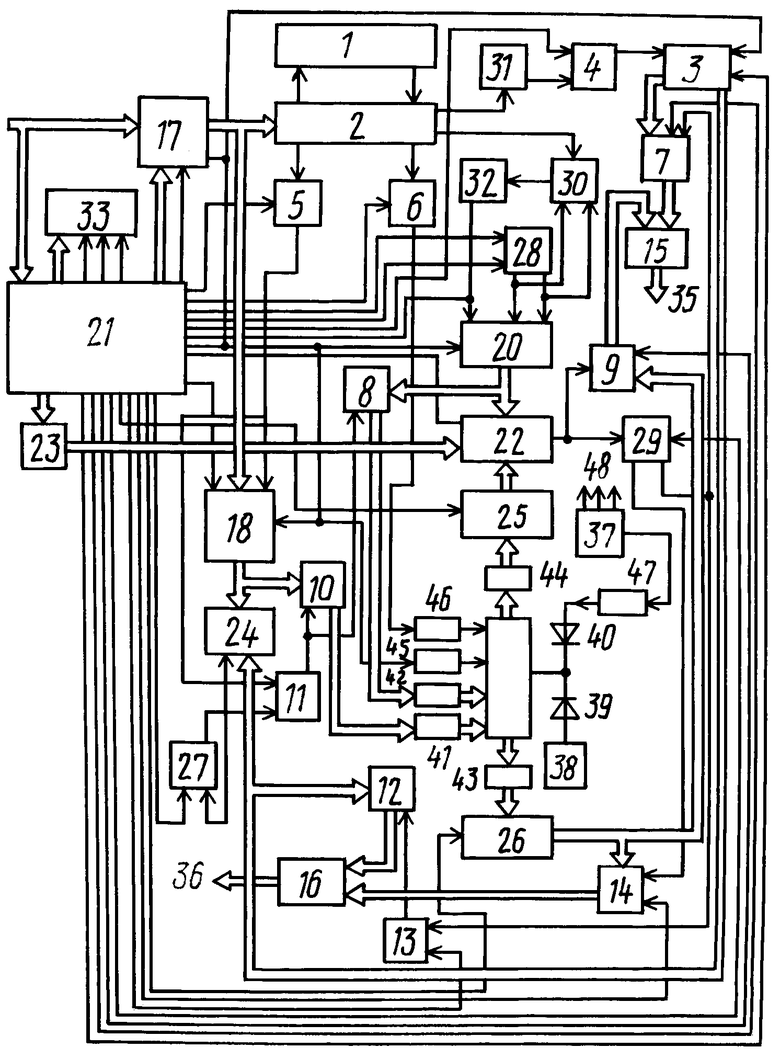

На чертеже приведена структурная электрическая схема предлагаемого устройства записи-воспроизведения цифровой информации.

Устройство записи-воспроизведения цифровой информации содержит накопитель 1 на подвижном носителе, блок 2 записи и воспроизведения цифровой информации (сопряженный с накопителем 1 на подвижном носителе), блок 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, первый элемент И 4, второй элемент И 5, третий элемент И 6, четвертый элемент И 7, пятый элемент И 8, шестой элемент И 9, седьмой элемент И 10, восьмой элемент И 11, девятый элемент И 12, десятый элемент И 13, одиннадцатый элемент И 14, первый элемент ИЛИ 15, второй элемент ИЛИ 16, первый блок 17 памяти, второй блок 18 памяти, третий блок 19 образцовой памяти с ограниченным объемом, реверсивный счетчик 20, блок 21 управления, адресный компаратор 22, первый регистр 22 адреса, компаратор 24 данных цифровой информации, второй регистр 25 адреса, регистр 26 памяти, первый триггер 27, второй триггер 28, третий триггер 29, селектор 30 сигналов, формирователь 31 импульсов, формирователь 32 синхроимпульсов, блок 33 управления приводом, шину 34 входной цифровой информации, шину 35 выходной цифровой информации в последовательном коде, шину 36 выходной цифровой информации в параллельном коде, источник 37 питания, автономный маломощный элемент 38 питания, первый диод 39, второй диод 40, первую, вторую, третью и четвертую группы электрически разъемных контактов 41, 42, 42, 44, электрически разъемные контакты 45, 46, 47, шины 48 напряжения источника питания.

Выходы и входы накопителя 1 на подвижном носителе подключены и сопряжены к соответствующим входам и выходам блока 2 записи и воспроизведения, первый, второй, третий и четвертый выходы которого подключены соответственно к первому входу второго элемента И 5, к первому входу третьего элемента И 6, к первой входной шине селектора 30 сигналов и к входу формирователя 31 импульсов, выход которого подключен к первому первого элемента И 4, выход которого подключен к информационному входу блока 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, шина выходов цифровой информации в последовательном коде и шина выходов цифровой информации, в параллельном коде которого подключены соответственно к информационным входам четвертого элемента И 7 и к параллельно соединенным информационным входам девятого элемента И 12 и вторым информационным входам компаратора 24 данных цифровой информации, шина 34 входной цифровой информации подключена к шине входов цифровой информации из линии связи первого блока 17 памяти и к шине входов сигналов сопровождения цифровой информации блока 21 управления, первый, второй и третий выходы сигналов управления и шина сигналов цифрового кода управления скоростью движения носителя блока 21 управления подключены соответственно к первой, к второй, к третьей входным шинам и к шине входных сигналов цифрового кода блока 33 управления приводом, шина сигналов команд и четвертый выход сигнала управления блока 21 управления подключены соответственно к шине сигналов команд и к шине сдвига цифровой информации в регистрах первого блока 17 памяти, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый и двадцатый выходы сигналов управления блока 21 управления подключены соответственно к второму входу второго элемента И 5, к второму входу третьего элемента И 6, к первому, к второму устойчивым входам второго триггера 28, к второму входу первого элемента И 4, к параллельно соединенным входам установки в "0" блока 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде, блоков 17, 18 и 19 первой, второй и третьей образцовой памяти и реверсивного счетчика 20, к шине сигнала сдвига цифровой информации в регистрах второго блока 18 памяти, к первому установочному входу первого триггера 27, к выходу сигнала управления регистра 26 памяти, к первому входу одиннадцатого элемента И 14, к первому входу десятого элемента И 13, к входу управления второго регистра 25 адреса, к второму установочному входу третьего триггера 29, к второму входу шестого элемента И 9, к второму входу четвертого элемента И 7, к управляющему входу блока 3 буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном и параллельном коде.

Шина сигналов цифрового кода адреса блока 21 управления подключена к шине цифрового кода адреса первого регистра 23 адреса, шина информационных выходов которого подключена к второй шине цифрового кода адреса адресного компаратора 22, первый и второй информационные входы блока 21 управления подключены соответственно к соединенным между собой выходу формирователя 32 синхроимпульсов и счетному входу реверсивного счетчика 20 и к информационному выходу адресного компаратора 22, выход второго элемента И 5 подключен к информационному выходу адресного компаратора 22, выход второго элемента И 5 подключен к параллельно соединенным шине входов цифровой информации второго блока 18 памяти с первым входом восьмого элемента 11, выход третьего элемента И 6 через второй электрически разъемный контакт 46 подключен к управляющему входу третьего блока 19 образцовой памяти с ограниченным объемом, шина информационных выходов и третий вход четвертого элемента И 7 подключены соответственно к второй шине информационных входов первого элемента ИЛИ 15 и к соединенным между собой второму информационному выходу третьего триггера 29 с вторым входом десятого элемента И 13, второй установочный вход и информационный выход первого триггера 27 подключены соответственно к информационному выходу компаратора 24 данных цифровой информации и к второму входу восьмого элемента И 11, выход которого подключен к параллельно соединенным разрешающим входам пятого элемента И 8 и седьмого элемента И 10.

Шина информационных входов и шина информационных выходов пятого элемента И 8 подключены соответственно к соединенным между собой шине информационных выходов реверсивного счетчика 20 с первой шиной цифрового кода адреса адресного компаратора 22 и через вторую группу электрически разъемных контактов 42 к шине входных сигналов цифрового кода текущего адреса третьего блока 19 образцовой памяти с ограниченным объемом, шина выходных сигналов цифровой информации первого блока 17 памяти подключена к параллельно соединенным шине цифровой информации из линии связи блока 2 записи и воспроизведения цифровой информации из линии связи второго блока 18 памяти, шина выходных сигналов цифровой информации которого подключена к параллельно соединенным первой входной шине входных сигналов цифровой информации компаратора 24 данных цифровой информации с шиной входных сигналов цифровой информации седьмого элемента И 10, шина выходных сигналов цифровой информации которого через первую группу электрически разъемных контактов 41 подключена к шине цифрового кода дефектной части цифровой информации третьего блока 19 образцовой памяти с ограниченным объемом, шины выходов цифровой информации которого подключены соответственно через третью и четвертую группы электрически разъемных контактов 43 и 44 к шине входных сигналов цифровой информации регистра 26 памяти и к шине цифрового кода адресного второго регистра 25, шина сигналов цифровой информации регистра 26 памяти подключена к параллельно соединенным шине входных цифровых сигналов шестого элемента И 9 с шиной входных цифровых сигналов одиннадцатого элемента И 14, шина выходных цифровых сигналов которого подключена к второй шине входных сигналов цифровой информации второго элемента ИЛИ 16.

Выход десятого элемента И 13 подключен к входу сигнала разрешения девятого элемента И 12, шина выходных цифровых сигналов которого подключена к первой шине входных сигналов цифровой информации второго элемента ИЛИ 16, шина выходных сигналов цифровой информации которого подключена к второй шине 36 выходной цифровой информации в параллельном коде, шина выходов сигналов цифрового кода адреса второго регистра 25 адреса подключена к третьей шине сигналов цифрового кода адреса адресного компаратора 22, шина выходных цифровых сигналов шестого элемента И 9 подключена к первой шине информационных входов первого элемента ИЛИ 15, шина выходных сигналов цифровой информации которого подключена к первой шине 35 выходной цифровой информации в последовательном коде, первый и второй информационные выходы второго триггера 28 подключены соответственно к параллельно соединенным входу прямого счета реверсивного счетчика 20 с вторым входом селектора 30 сигналов и к параллельно соединенным входу обратного счета реверсивного счетчика 20 с третьим входом селектора 30 сигналов, выход селектора 30 сигналов подключен к входу формирователя 32 синхроимпульсов, катоды диодов 39, 40 объединены и подключены к шине подачи напряжения питания третьего блока 19 образцовой памяти с ограниченным объемом, анод диода 39 подключен к выходу автономного элемента 38 напряжения питания, а анод диода 40 через третий электрически разъемный контакт 47 к выходу источника питания 37.

Устройство записи-воспроизведения цифровой информации работает следующим образом.

Предварительно сигналом установки в "0", поступающим с десятого выхода блока 21 управления, производят подготовку к работе блока 3 буферной памяти с преобразователями кода, реверсивного счетчика 20, первого блока 17 памяти, второго блока 18 памяти и третьего блока 19 образцовой памяти с ограниченным объемом.

Режим периодического чередования записи и воспроизведения задается сигналами соответственно с первого, второго и третьего выходов блока 21 управления, подаваемыми на первую, вторую и третью шины сигналов управления блока 33 управления приводом. При этом также с выходной шины сигналов цифрового кода блока 21 управления поступают на четвертую, пятую и шестую шины блока 33 управления приводом соответствующие сигналы цифрового кода управления скоростью движения носителя, а с седьмого и восьмого выходов блока 21 управления поступают на первый и второй установочные входы второго триггера 28 и соответственно на входы прямого и обратного счета реверсивного счетчика 20 и на вторую и третью входные шины селектора 30 сигналов, соответствующие установленному режиму сигналы управления. Входная цифровая информация с сигналами сопровождения из линии связи с входной шины 34 подается на вход первого блока 17 памяти. При этом сигналы сопровождения подаются на входную шину блока 21 управления. В памяти блока управления в каждый данный момент вырабатывается запись входной цифровой информации. Если ни одна ячейка в памяти первого блока 17 памяти не заполнена, то входная цифровая информация (в режиме воспроизведения) записывается в первую ячейку, следующая во вторую и т, д. а в режиме записи проходит на выход первого блока 17 памяти. В начальный момент работы устройства осуществляется режим записи. При этом входная цифровая информация проходит с входной шины 34 через первый блок 17 памяти транзитом (поскольку ни одна ячейка в памяти блока 17 не заполнена) на вход блока 2 записи и воспроизведения, откуда осуществляется запись ее на накопитель 1, и на вход второго блока 18 памяти, где производится запись текущей цифровой информации в режиме записи устройства. Одновременно в этом режиме осуществляется подсвет реверсивным счетчиком 20 синхроимпульсов, поступающих на его счетный вход с выхода блока 2 записи и воспроизведения. При этом на информационных выходах реверсивного счетчика 20 воспроизводится текущий адрес части цифровой информации, записываемой в накопитель 1 на движущемся носителе. Таким образом, в режиме записи осуществляется запись входной цифровой информации на носитель и одновременно эта же информация записывается в второй блок 18 памяти. Режим записи осуществляется до момента достижения равенства кода адреса с реверсивного счетчика 20 коду адреса выставленного с блока 21 управления в первом регистре 23 адреса. При совпадении цифровых кодов адресов с выходов реверсивного счетчика 20 и регистра 23 адреса на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый на второй информационный вход блока 21 управления.

При этом блок 21 управления вырабатывает соответствующий сигнал реверса, подаваемый на соответствующую шину сигнала управления блока 33 управления приводом, в результате чего начинает осуществляться режим воспроизведения. Наряду с этим с блока 21 управления выставляется в первом регистре 23 адреса код адреса, до которого осуществляется режим воспроизведения. В данном режиме входная информация записывается в первый блок 17 памяти и информация, записанная в накопитель 1 на подвижном носителе, считывается, осуществляется промежуточное запоминание ее частей в блоке 3 буферной памяти с преобразователями кода и с помощью компаратора 24 данных цифровой информации поразрядное сравнение с идентичной информацией, считываемой из второго блока 18 памяти. При несовпадении на выходе элемента И 10 вырабатывается сигнал, по которому несовпавшая информация из второго блока 18 памяти записывается в третий блок 10 образцовой памяти с ограниченным объемом вместе с текущим адресом (через элемент И 8), зафиксированным в данный момент на реверсивном счетчике 20.

Режим воспроизведения осуществляется до момента совпадения кода с информационных выходов реверсивного счетчика 20 с кодом выставленным с блока 21 памяти управления. При этом на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый через блок 21 управления на блок управления приводом. Кроме того, блок 21 управления выставляет код адреса. При этом блок 33 управления приводом осуществляет реверс и форсированный режим перемотки магнитной ленты накопителя 11 до момента совпадения кода с реверсивного счетчика 20 и кода выставленного с блока 21 управления. При этом по сигналу с адресного компаратора 22 блок 21 управления вырабатывает сигнал на блок 33 управления приводом, по которому прекращается форcированный режим перемотки магнитной ленты накопителя 1 и начинается следующий цикл нормальной записи входной цифровой информации в накопитель 1 на подвижном носителе. При этом блок 21 управления выставляет адрес, до которого должен осуществляться данный режим записи. В момент достижения равенства кода адреса и реверсивного счетчика 20 и кода адреса, выставленного с блока 21 управления, на выходе адресного компаратора 22 вырабатывается сигнал, подаваемый на блок 21 управления. И далее аналогично описанному выше с той лишь разницей, что входная цифровая информация записывается в накопитель 1 и второй блок 18 памяти.

При окончательном воспроизведении записанной в накопитель 1 на подвижном носителе информации (описанным выше способом) с блока 21 управления на блок 33 управления приводом подается соответствующий сигнал управления, выставляется оконечный адрес считывания и подаются соответствующие сигналы управления на реверсивный счетчик 20 и селектор 30 сигнала, и на блоки 17, 18 и 19 соответственно первой, второй и третьей образцовой памяти с ограниченным объемом. При этом реверсивный счетчик 20 должен считать в обратном направлении.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА О СОСТОЯНИИ ОБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010261C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2042219C1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| СПОСОБ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2042150C1 |

| СПОСОБ МОДУЛЯЦИИ ИМПУЛЬСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2022461C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 1991 |

|

RU2010422C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1644217A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| РАДИОЛОКАЦИОННЫЙ ОТВЕТЧИК | 1990 |

|

RU2041477C1 |

Использование: приборостроение, при построении долговременных запоминающих устройств на подвижном носителе. Сущность: устройство позволяет осуществлять с высокой точностью и достоверностью воспроизведение записанной ранее информации в другом месте и на другом устройстве записи-воспроизведения, обеспечивает уменьшение потребления мощности напряжения питания в режиме штатной работы, в котором просматриваются длительные паузы между воспроизведениями отдельных зон цифровой информации, предусматривает возможность формирования банка данных дефектной части информации, индексированной по номерам накопителей и датам ее записи. 1 ил.

УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее накопитель на подвижном носителе, блок записи и воспроизведения цифровой информации, сопряженный с накопителем, блок буферной памяти с преобразователями кода с шинами выходов цифровой информации в последовательном параллельном коде, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И, первый и второй элементы ИЛИ, первый, второй и третий блоки памяти, реверсивный счетчик, компаратор данных цифровой информации, адресный компаратор, блок управления, первый и второй регистры адреса, регистр памяти, первый, второй и третий триггеры, селектор сигналов, формирователь импульсов, формирователь синхроимпульсов, блок управления приводом, шину входной цифровой информации, шину выходной цифровой информации в последовательном коде, шину выходной цифровой информации в параллельном коде и источник питания, отличающееся тем, что в него введены первая, вторая, третья, четвертая группы электрически разъемных контактов, первый, второй и третий электрически разъемные контакты, автономный маломощный элемент питания, первый и второй диоды, катоды которых объединены и подключены к клемме подачи напряжения на третий блок памяти, анод первого диода подсоединен к выходу автономного маломощного элемента питания, а анод второго диода через третий электрически разъемный контакт к выходу источника питания, выходы блока управления, третьего, пятого и седьмого элементов И подключены соответственно к входу установки в исходное состояние третьего блока питания через первый электрически разъемный контакт, к управляющему входу третьего блока памяти через второй электрически разъемный контакт, к шине входных сигналов цифрового кода текущего адреса третьего блока памяти через вторую группу электрически разъемных контактов и через первую группу электрически разъемных контактов к шине цифрового кода дефектной части цифровой информации третьего блока памяти, шины выходов цифровой информации которого через третью и четвертую группы электрически разъемных контактов подключены соответственно к шине входных сигналов цифровой информации регистра памяти и к шине цифрового кода адреса второго регистра адреса.

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-07-09—Публикация

1992-02-06—Подача