Изобретение относится к автоматике и вычислительной технике, а также к импульсной и измерительной технике и может быть использовано в системах обработки информации и управления производственными процессами.

Известно запоминающее устройство, содержащее множество ячеек, расположенных рядами и столбцами, при этом каждая ячейка содержит два транзистора с перекрестными обратными связями, причем коллектор каждого транзистора непосредственно соединен с базой другого транзистора (патент США N 3725878, кл. 340-173 FF, 1973).

Недостатками этого устройства являются низкая надежность и ограниченные функциональные возможности, что обусловлено значительным количеством используемых элементов и тем, что осуществляется запоминание и воспроизведение информации лишь в кодовом представлении.

Известно запоминающее устройство (авт. св. СССР N 559283, кл. G 11 C 27/00, 1977), содержащее первый, второй, третий, четвертый и пятый элементы И, генератор импульсов, выход которого подключен к первому входу первого элемента И.

Недостатками этого устройства являются низкая точность и ограниченный диапазон изменения значений входных сигналов. Низкая точность обусловлена тем, что входной сигнал задается не в виде широтно-импульсного сигнала, а в виде напряжения (что говорит также об ограниченных функциональных возможностях). Кроме того, запоминание входных сигналов осуществляется на запоминающем конденсаторе, что сопряжено с погрешностями за счет наличия утечки. И наконец, имеет место весьма существенная составляющая погрешности за счет последующей операции преобразования напряжения (запомненного на конденсаторе) в длительность импульсов, а также за счет погрешности импульсных источников тока и напряжения и других аналоговых элементов.

Наиболее близким к изобретению по технической сущности и достигаемому эффекту является запоминающее устройство (авт.св. СССР N 503298, кл. G 11 C 27/00, 1976), содержащее генератор импульсов, первый реверсивный счетчик, первый регистр памяти, первый, второй, третий и четвертый триггеры, первую и вторую группы элементов И, первый и второй элементы ИЛИ, первый и второй элементы И, причем информационные выходы первого реверсивного счетчика подключены к первым входам первой группы элементов И, выходы которых соединены с входами первого регистра памяти, выходы которого соединены с первыми входами второй группы элементов И, прямой и инверсный выходы первого триггера подключены к управляющим входам реверсивного счетчика.

Недостатком этого устройства являются ограниченные функциональные возможности, обусловленные тем, что не осуществляется запоминание широтно-импульсных сигналов, а также преобразование кода в широтно-импульсный сигнал.

Целью изобретения является расширение функциональных возможностей устройства, заключающееся в обеспечении запоминания широтно-импульсных сигналов, а также преобразования кода в широтно-импульсный сигнал.

Цель достигается тем, что усовершенствуется запоминающее устройство, содержащее генератор импульсов, первый реверсивный счетчик, первый регистр памяти, первый, второй, третий и четвертый триггеры, первую и вторую группы элементов И, первый и второй элементы ИЛИ, первый и второй элементы И, причем информационные выходы первого реверсивного счетчика подключены к первым входам первой группы элементов И, выходы которых соединены с входами первого регистра памяти, выходы которого соединены с первыми входами второй группы элементов И, прямой и инверсный выходы первого триггера подключены к управляющим входам первого реверсивного счетчика.

Отличительными признаками предложенного устройства являются следующие. В устройство введены второй реверсивный счетчик, второй регистр памяти, пятый и шестой триггеры, третья и четвертая группы элементов И, первый и второй инверторы, третий, четвертый и пятый элементы ИЛИ, первая и вторая группы элементов ИЛИ, третий, четвертый, пятый и шестой элементы И, при этом информационные входы первого реверсивного счетчика соединены с выходами первой группы элементов ИЛИ, первые входы которых подключены к выходам второй группы элементов И, а вторые являются информационными входами первой группы устройства, прямой и инверсный выходы первого триггера подключены к управляющим входам второго реверсивного счетчика, выходы которого подключены к первым входам третьей группы элементов И, выходы которых соединены с входами второго регистра памяти, выходы которого подключены к первым входам четвертой группы элементов И, информационные входы второго реверсивного счетчика соединены с выходами второй группы элементов ИЛИ, первые входы которых подключены к выходам четвертой группы элементов И, а вторые являются информационными входами второй группы устройства, вторые входы первой и третьей групп элементов И объединены и подключены к единичному входу первого триггера и являются вторым управляющим входом устройства, вторые входы второй и четвертой групп элементов И подключены соответственно к выходам первого и второго реверсивных счетчиков, нулевой вход первого триггера соединен с входами установки в ноль первого и второго реверсивного счетчиков, первого и второго регистров памяти и является третьим управляющим входом устройства, счетный вход первого реверсивного счетчика соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам первого и второго элементов И, первый вход первого элемента И соединен с нулевым выходом второго триггера и является выходом устройства, а второй соединен с выходом генератора импульсов, первыми входами третьего и четвертого элементов И и второго элемента И, второй вход которого соединен с нулевым выходом третьего триггера и входом первого инвертора, а третий вход является информационным входом устройства и соединен с входом второго инвертора и первым входом пятого элемента И, счетный вход второго реверсивного счетчика соединен с выходом второго элемента ИЛИ, первый вход которого соединен с нулевыми входами третьего и четвертого триггеров и с выходом третьего элемента И, второй вход второго элемента ИЛИ соединен с выходом четвертого элемента И, второй вход которого соединен с нулевым выходом шестого триггера, второй вход третьего элемента И подключен к выходу второго инвертора, третий подключен к нулевому выходу пятого триггера, единичный вход третьего триггера соединен с выходом шестого элемента И, второй вход которого соединен с выходом четвертого триггера, единичный вход которого является первым управляющим входом устройства, единичный вход второго триггера соединен с выходом третьего элемента ИЛИ, первый вход которого является вторым управляющим входом устройства, а второй подключен к выходу второго реверсивного счетчика, нулевой вход второго триггера соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого реверсивного счетчика, а второй является третьим управляющим входом устройства и подключен к первому входу пятого элемента ИЛИ, единичный вход пятого триггера подключен к выходу второго элемента И, а нулевой к выходу пятого элемента И, второй вход которого соединен с выходом первого инвертора, нулевой вход шестого триггера соединен с выходом второго реверсивного счетчика.

Не обнаружены технические решения, имеющие сходные признаки с признаками, отличающими заявляемое решение от прототипа, следовательно, предлагаемое техническое решение обладает существенными отличиями.

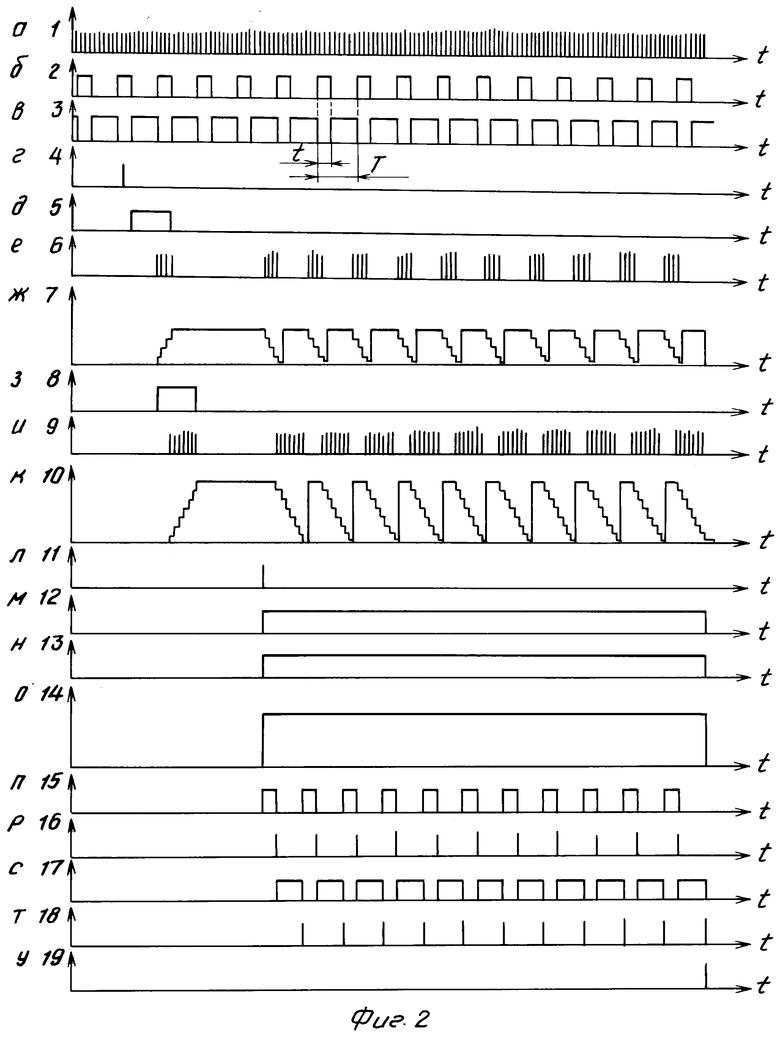

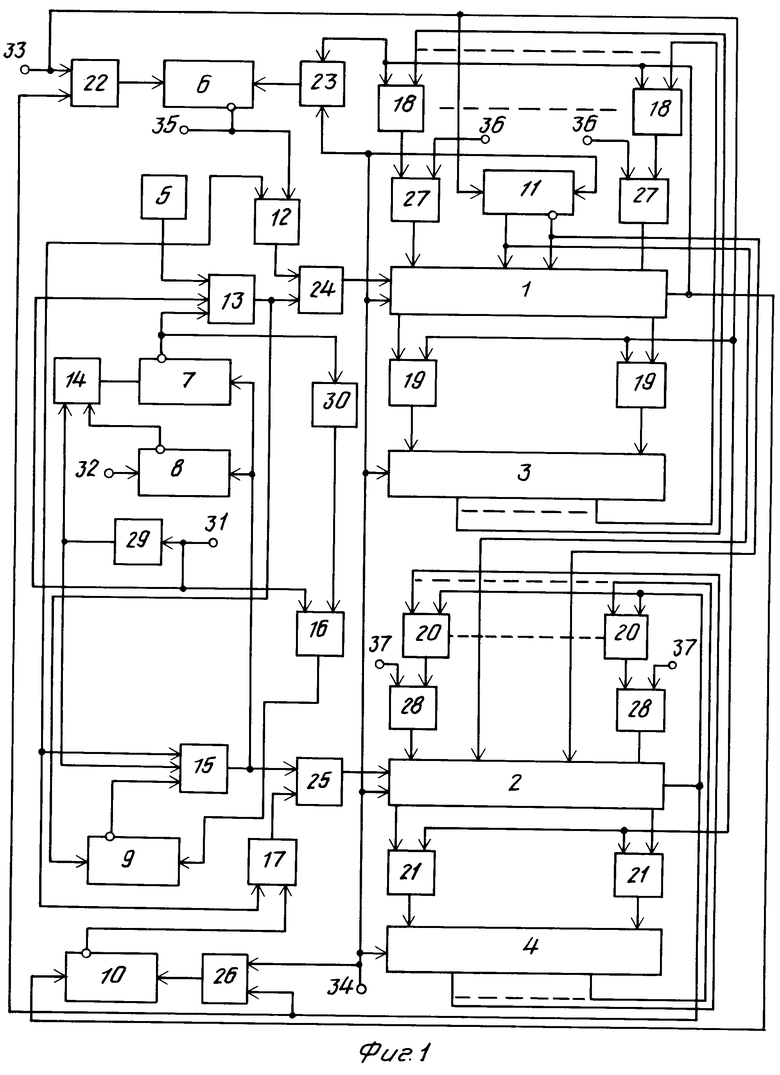

На фиг.1 приведена структурная схема предлагаемого запоминающего устройства; на фиг.2 временная диаграмма, поясняющая принцип действия устройства.

Запоминающее устройство содержит реверсивные счетчики 1, 2, регистры 3, 4, памяти, генератор 5 импульсов, триггеры 6-11, элементы И 12-17, группы элементов И 18-21, элементы ИЛИ 22-26, группы элементов ИЛИ 27, 28, инверторы 29, 30.

Информационные входы первого реверсивного счетчика 1 подключены к первым входам группы элементов И 19, выходы которых соединены с входами регистра 3 памяти, выходы которого соединены с первыми входами группы элементов И 18. Прямой и инверсный выходы триггера 11 подключены к управляющим входам реверсивного счетчика 1, информационные входы которого соединены с выходами группы элементов ИЛИ 27, первые входы которых подключены к выходам группы элементов И 18, а вторые к информационным входам 36 первой группы устройства. Прямой и инверсный выходы триггера 11 подключены к управляющим входам реверсивного счетчика 2, выходы которого подключены к первым входам группы элементов И 21. Выходы последних соединены с входами регистра 4 памяти, выходы которого подключены к первым входам группы элементов И 20. Информационные входы реверсивного счетчика 2 соединены с выходами группы элементов ИЛИ 28, первые входы которых подключены к выходам группы элементов И 20, а вторые к информационным входам 37 второй группы устройства. Вторые входы группы элементов И 18 и группы элементов И 20 объединены и подключены к единичному входу триггера 11 и к управляющему входу 33 устройства. Вторые входы групп элементов И 18 и 20 подключены соответственно к выходам реверсивного счетчика 1 и реверсивного счетчика 2. Нулевой вход триггера 11 соединен с входами установки в ноль реверсивных счетчиков 1 и 2, регистров 3 и 4 памяти и с управляющим входом 34 устройства. Счетный вход реверсивного счетчика 1 соединен с выходом элемента ИЛИ 24, первый и второй входы которого подключены соответственно к выходам элементов И 12 и 13. Первый вход элемента И 12 соединен с нулевым выходом триггера 6 и с выходом 35 устройства, а второй с выходом генератора 5 импульсов, первыми входами элементов И 15 и 17 и элемента И 13, второй вход которого соединен с нулевым выходом триггера 7 и входом инвертора 30, а третий вход с информационным входом 31 устройства и соединен с входом инвертора 29 и первым входом элемента И 16. Счетный вход реверсивного счетчика 2 соединен с выходом элемента ИЛИ 25, первый вход которого соединен с нулевыми входами триггеров 7 и 8 и с выходом элемента И 15. Второй вход элемента ИЛИ 25 соединен с выходом элемента И 17, второй вход которого соединен с нулевым выходом триггера 10, второй вход элемента И 15 подключен к выходу инвертора 29, третий к нулевому выходу триггера 9. Единичный вход триггера 7 соединен с выходом элемента И 14, второй вход которого соединен с выходом триггера 8, единичный вход которого подключен к управляющему входу 32 устройства. Единичный вход триггера 6 соединен с выходом элемента ИЛИ 22, первый вход которого подключен к управляющему входу 33 устройства, а второй к выходу реверсивного счетчика 2. Нулевой вход триггера 6 соединен с выходом элемента ИЛИ 23, первый вход которого соединен с выходом реверсивного счетчика 1, а второй с управляющим входом 34 устройства и с первым входом элемента ИЛИ 26. Единичный вход триггера 9 подключен к выходу элемента И 13, а нулевой к выходу элемента И 16, второй вход которого соединен с выходом инвертора 30. Нулевой вход триггера 10 соединен с выходом элемента ИЛИ 26, второй вход которого соединен с выходом реверсивного счетчика 2.

Запоминающее устройство работает следующим образом.

Импульсы эталонной частоты с выхода генератора 5 импульсов поступают на входы реверсивных счетчиков 1 и 2 соответственно через элементы И 13 и 15 в режиме записи и через элементы И 12 и 17 в режиме воспроизведения.

Сигналы с информационных выходов реверсивных счетчиков через группы элементов И 19 и 21 передаются соответственно в регистры 3 и 4 памяти, с выходов которых через группы элементов И 18 и 20 и группы элементов ИЛИ 27 и 28 подаются на информационные входы реверсивных счетчиков. Управление режимом работы счетчиков осуществляется сигналами с выходов триггера 11, а управление прохождением сигналов через элементы И 12, 13, 14, 15, 16, 17 и через группы элементов И 18, 19, 20, 21 осуществляется сигналами с выходов триггеров 6, 7, 8, 9, 10, сигналами с выходов реверсивных счетчиков 1, 2 и входными сигналами управления, подаваемыми на входы 31, 32, 33, 34 устройства.

В исходном состоянии реверсивные счетчики, регистры памяти и триггеры находятся в нулевом состоянии, а реверсивные счетчики к тому же установлены в режим работы "сложение". Устройство может работать в двух режимах в режиме записи действующего значения входной информации и в режиме воспроизведения запомненной информации.

Сначала реализуется режим записи. Импульсы эталонной частоты с выхода генератора 5 импульсов (фиг.2а) подаются на входы ряда элементов И, в том числе и на входы элементов И 13 и 15, но они далее не проходят через упомянутые элементы, так как эти элементы заперты сигналами с выходов триггеров 7 и 9.

Цикл запоминания действующего значения широтно-импульсного сигнала (фиг. 2б), подаваемого на информационный вход, начинается с подачи сигнала записи на управляющий вход 32. При этом триггер 8 переводится в состояние "1" и отпирается элемент И 14 для сигналов с выхода инвертора 29. Очевидно, что элемент И 14 открывается только в случае действия в данный момент сигнала паузы входного сигнала на управляющем входе 31, что необходимо для выполнения условия синхронизации. При отпирании элемента И 14 триггер 7 переводится в состояние "1", в результате чего отпирается элемент И 13 для входных сигналов длительностью t и для сигналов с выхода генератора 5 импульсов. С поступлением входного сигнала длительностью t на счетный вход реверсивного счетчика 1 через элемент ИЛИ 24 начинают проходить импульсы эталонной частоты с выхода генератора 5 импульсов (фиг.2е), которые в нем суммируются. Информация в реверсивном счетчике 1 представлена на фиг.2ж. При этом одновременно с появлением первого сигнала на выходе элемента И 13 триггер 9 переводится в состояние "1" (фиг.2з), отпирая элемент И 15 для сигналов с выхода инвертора 29 (фиг.2в) и с выхода генератора 5 импульсов. По окончании действия импульсов входного сигнала элемент И 13 запирается и подача импульсов эталонной частоты на вход реверсивного счетчика 1 прекращается. При этом в нем фиксируется информация, соответствующая длительности t импульса входного сигнала (фиг.2ж). Одновременно на выходе инвертора 29 воспроизводится высокий уровень напряжения, который имеет место в течение действия паузы Т-t входного сигнала, где Т период повторения широтно-импульсного сигнала. При этом через элемент ИЛИ 25 на счетный вход реверсивного счетчика 2 начинают проходить импульсы эталонной частоты (фиг.2и) с выхода генератора 5 импульсов, которые в нем суммируются. Информация в реверсивном счетчике 2 представлена на фиг.2к.

Под действием первого сигнала с выхода элемента И 15 триггеры 7 и 8 переводятся в нулевое положение. При этом элемент И 16 отпирается для входного сигнала. С появлением импульса входного сигнала он проходит на выход элемента И 16, переводя триггер 9 в нулевое состояние. На этом цикл записи входной информации заканчивается.

Значение периода Тэт эталонной частоты должно быть существенно меньше, чем длительность t и паузы Т-t входного сигнала.

Число импульсов n1, зафиксированное в реверсивном счетчике 1, определяется как

n1=  (1) а число импульсов, зафиксированное в реверсивном счетчике 2,

(1) а число импульсов, зафиксированное в реверсивном счетчике 2,

n2=  (2)

(2)

В режиме воспроизведения устройство функционирует следующим образом.

При необходимости выдачи запомненной информации в течение определенного отрезка времени на второй управляющий вход 33 подается сигнал начала воспроизведения (фиг. 2л). При этом через группы элементов И 19 и 21 информация, запомненная в реверсивных счетчиках 1 и 2, передается соответственно в регистры 3 и 4 памяти, где запоминается (фиг.2 н,о), а триггер 11 переводится в состояние "1", в результате чего реверсивного счетчики 1 и 2 переводятся в режим работы "вычитание".

Одновременно сигнал начала воспроизведения через элемент ИЛИ 22 поступает на вход триггера 6, переводя его в состояние "1" (фиг.2п). Выходные сигналы триггера 6 являются выходными сигналами устройства и подаются на выход 35. При этом открывается элемент И 12 и сигналы эталонной частоты с его выхода начинают поступать через элемент ИЛИ 24 на счетный вход реверсивного счетчика 1 (фиг.2е). Поскольку перед этим реверсивный счетчик 1 был установлен в режим работы "вычитание", то при подаче сигналов эталонной частоты на его вход осуществляется считывание запомненной в нем информации (фиг. 2ж). По достижении нулевой информации в реверсивном счетчике 1 на его выходе вырабатывается сигнал (фиг.2р), который подается на вход установки в "1" триггера 10 и через элемент ИЛИ 23 на вход триггера 6. При этом триггер 10 переводится в состояние "1", а триггер 6 в состояние "0", что приводит к запиранию элемента И 12 и отпиранию элемента И 17 для сигналов эталонной частоты с выхода генератора 5 импульсов, которые начинают подаваться на счетный вход реверсивного счетчика 2 (фиг.2 и). Одновременно сигнал с выхода реверсивного счетчика 1 подается на управляющие входы группы элементов И 18, связанной с регистром 3 памяти. При этом информация запомненная в регистре 3 памяти, переписывается в реверсивный счетчик 1. Далее осуществляется процесс считывания информации в реверсивном счетчике 2 (фиг.2к) аналогично описанному выше процессу считывания в реверсивном счетчике 1.

По достижении нулевой информации в реверсивном счетчике 2 на его выходе вырабатывается сигнал (фиг. 2т), который подается через элемент ИЛИ 26 на вход установки в "0" триггера 10 и через элемент ИЛИ 22 на вход триггера 6. При этом триггер 10 переводится в состояние "0", а триггер 6 в состояние "1", что приводит к отпиранию элемента И 12 и запиранию элемента И 17. Сигнал с выхода реверсивного счетчика 2, кроме того, подается на управляющие входы группы элементов И 20, связанной с регистром 4 памяти. При этом информация, запомненная в регистре 4 памяти, переписывается в реверсивный счетчик 2. Далее осуществляется считывание информации в реверсивном счетчике 1 и описанный выше процесс повторяется. Таким образом, в зависимости от исходных уставок в реверсивных счетчиках 1 и 2 на их выходах воспроизводятся сигналы через вполне определенное время, характеризующее соответственно длительность t и паузу Т t широтно-импульсного сигнала. Покажем это. При считывании информации в реверсивном счетчике 1 интервал времени от момента начала считывания до момента выработки выходного сигнала определяется как

Т1 Тэт ˙ n1 (3)

Подставляя выражение (1) в уравнение (3), получают выражение для Т1:

T1= Tэт t (4)

t (4)

При считывании информации в реверсивном счетчике 2 интервал времени от момента начала считывания до момента выработки выходного сигнала определяется как

Т2 Тэт ˙ n2 (5)

Подставляя выражение (2) в уравнение (5), получают выражение для Т2:

T2= Tэт T-t

T-t

Таким образом, из приведенных выражений следует что на выходе триггера 6, связанном с выходом 35 устройства, воспроизводится запомненный ранее широтно-импульсный сигнал, что и требовалось получить.

Для прекращения выдачи запомненной информации подается сигнал "Окончание воспроизведения" на третий управляющий вход 34 устройства (фиг.2у), который через элементы ИЛИ 23 и 26 поступает на нулевые входы триггеров 6 и 10, переводя их в нулевое состояние. При этом запираются элементы И 12 и 17 и прекращается подача сигналов эталонной частоты на входы реверсивных счетчиков 1 и 2. Реверсивные счетчики и регистры памяти устанавливаются в нулевое состояние.

В предложенном устройстве имеется возможность записи входной информации, заданной в виде кода. При этом информация, характеризующая величину t, подается на информационные входы 36 первой группы устройства и далее через группу элементов ИЛИ 27 записывается в реверсивный счетчик 1, а информация, характеризующая величину Т-t, подается на информационные входы 37 второй группы устройства и далее через группу элементов ИЛИ 28 записывается в реверсивный счетчик 2. Это обстоятельство способствует расширению функциональных возможностей устройства.

В данном случае предлагаемое устройство может быть использовано в качестве преобразования кода в широтно-импульсный сигнал.

Технико-экономическое преимущество предложенного запоминающего устройства по сравнению с известными заключается в том, что обеспечивается существенное расширение функциональных возможностей. Это обусловлено тем, что в устройстве реализуется запоминание широтно-импульсных сигналов, а также преобразование кода в широтно-импульсный сигнал.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

| СПОСОБ МОДУЛЯЦИИ ИМПУЛЬСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2022461C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА О СОСТОЯНИИ ОБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010261C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 1991 |

|

RU2010422C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2042150C1 |

| ДОПЛЕРОВСКАЯ РАДАРНАЯ СИСТЕМА | 1991 |

|

RU2009521C1 |

| ДИСКРИМИНАТОР ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1991 |

|

RU2007852C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОИСКОМ ТЕКСТОВЫХ ДОКУМЕНТОВ В ИНФОРМАЦИОННОЙ БАЗЕ ДАННЫХ | 2003 |

|

RU2241253C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации и управления производственными процессами. Запоминающее устройство содержит реверсивные счетчики 1, 2, регистры 3, 4 памяти, генератор 5 импульсов, триггеры 6 11, элементы И 12 17, группы элементов И 18 21, элементы ИЛИ 22 26, группы элементов ИЛИ 27, 28, инверторы 29, 30. 2 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее генератор импульсов, первый реверсивный счетчик, первый регистр памяти, первый, второй, третий и четвертый триггеры, первую и вторую группы элементов И, первый и второй элементы ИЛИ, первый и второй элементы И, информационные входы первого реверсивного счетчика подключены к первым входам первой группы элементов И, выходы которых соединены с входами первого регистра памяти, выходы которого соединены с первыми входами второй группы элементов И, прямой и инверсный выходы первого триггера подключены к управляющим входам реверсивного счетчика, отличающееся тем, что оно содержит второй реверсивный счетчик, второй регистр памяти, пятый и шестой триггеры, третью и четвертую группы элементов И, первый и второй инверторы, третий, четвертый и пятый элементы ИЛИ, первую и вторую группы элементов ИЛИ, третий, четвертый, пятый и шестой элементы И, информационные входы первого реверсивного счетчика соединены с выходами первой группы элементов ИЛИ, первые входы которых подключены к выходам второй группы элементов И, а вторые являются информационными входами первой группы устройства, прямой и инверсный выходы первого триггера подключены к управляющим входам второго реверсивного счетчика, выходы которого подключены к первым входам третьей группы элементов И, выходы которых соединены с входами второго регистра памяти, выходы которого подключены к первым входам третьей группы элементов И, информационные входы второго реверсивного счетчика соединены с выходами второй группы элементов ИЛИ, первые входы которых подключены к выходам четвертой группы элементов И, а вторые являются информационными входами второй группы устройства, вторые входы первой и третьей групп элементов И объединены и подключены к единичному входу первого триггера и являются вторым управляющим входом устройства, вторые входы второй и четвертой групп элементов И подключены соответственно к выходам первого и второго реверсивных счетчиков, нулевой вход первого триггера соединен с входами установки в "о" первого и второго реверсивных счетчиков, первого и второго регистров памяти и являются третьим управляющим входом устройства, счетный вход первого реверсивного счетчика соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам первого и второго элементов И, первый вход первого элемента И соединен с нулевым входом второго триггера и является выходом устройства, а второй соединен с выходом генератора импульсов, первыми входами третьего и четвертого элементов И и второго элемента И, второй вход которого соединен с нулевым выходом третьего триггера и входом первого инвертора, а третий вход является информационным входом устройства, входом второго инвертора и первым входом пятого элемента И, счетный вход второго регистра счетчика соединен с выходом второго элемента ИЛИ, первый вход которого соединен с нулевыми входами третьего и четвертого триггеров и выходом третьего элемента И, второй вход второго элемента ИЛИ соединен с выходом четвертого элемента И, второй вход которого соединен с нулевым выходом шестого триггера, второй вход третьего элемента И подключен к выходу второго инвертора, третий к нулевому выходу пятого триггера, единичный вход третьего триггера соединен с выходом шестого элемента И, второй вход которого соединен с выходом четвертого триггера, единичный вход которого является первым управляющим входом устройства, единичный вход второго триггера соединен с выходом третьего элемента ИЛИ, первый вход которого является вторым управляющим входом устройства, а второй подключен к выходу второго реверсивного счетчика, нулевой вход второго триггера соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого реверсивного счетчика, а второй является третьим управляющим входом устройства и подключен к первому входу пятого элемента ИЛИ, единичный вход пятого триггера подключен к выходу второго элемента И, а нулевой к выходу пятого элемента И, второй вход которого соединен с выходом первого инвертора, нулевой вход шестого триггера соединен с выходом пятого элемента ИЛИ, второй вход которого соединен с выходом второго реверсивного счетчика.

| Частотно-импульсное запоминающее устройство | 1974 |

|

SU503298A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-08-20—Публикация

1992-06-15—Подача