Изобретение относится к автоматике, вычислительной технике, а также к импульсной и измерительной технике.

Известно устройство преобразования кода в частоту импульсов, содержащее регистр, счетчик импульсов, вход которого соединен с выходом генератора импульсов, диодный дешифратор, к входным шинам которого подключены выходы регистра и счетчика, а выходные шины соединены с входами элемента ИЛИ, соединенного обратной связью с входом установки в ноль счетчика [1]

Недостатками известного устройства являются ограниченный диапазон преобразования, низкие точность и надежность.

Известен также преобразователь цифрового кода в частоту следования импульсов, содержащий первый, второй и третий счетчики импульсов, первый и второй регистры памяти, первую, вторую и третью группы элементов И переноса, первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы задержки [2]

Недостатками известного преобразователя являются низкая точность, ограниченный диапазон значений преобразуемого кода и невысокое быстродействие. Это обусловлено тем, что при увеличении значений входного кода N частота импульсов на выходе первого счетчика уменьшается, что приводит к увеличению погрешности дискретности, поскольку информация во втором счетчике фиксируется с точностью до периода входного сигнала в течение заданного интервала Т.

Наиболее близким к изобретению по технической сущности и достигаемому эффекту является преобразователь цифрового кода в частоту следования импульсов, содержащий первый, второй и третий счетчики импульсов, первый и второй регистры памяти, блок коррекции, блок задержки сигналов, блок сдвига фазы, первую, вторую и третью группы элементов И, первый, второй, третий, четвертый и пятый триггеры, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй, третий, четвертый и пятый элементы задержки, шины входного кода и управляющего сигнала, первую и вторую шины импульсов эталонной частоты, шину временного интервала и выходную шину [3]

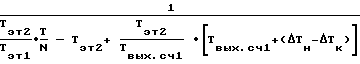

В данном преобразователе в процессе преобразования входного цифрового кода в частоту следования импульсов реализуется следующее выражение:

Fвых=  (1) где Тэт1 и Тэт2 периоды сигналов эталонных частот, подаваемых соответственно на первую и вторую шины импульсов эталонной частоты:

(1) где Тэт1 и Тэт2 периоды сигналов эталонных частот, подаваемых соответственно на первую и вторую шины импульсов эталонной частоты:

N входной цифровой код;

Т интервал времени образования промежуточного кода во втором счетчике;

Твых.сч1 период сигналов с выхода первого счетчика;

ΔТн интервал времени между моментом поступления импульса частоты Fсч1 (с выхода первого счетчика) и моментом поступления импульса частоты F (периодом Т) в начале интервала Т;

ΔТк интервал времени между моментом поступления импульса частоты Fсч1 и моментом поступления импульса частоты F в конце интервала Т.

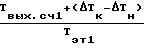

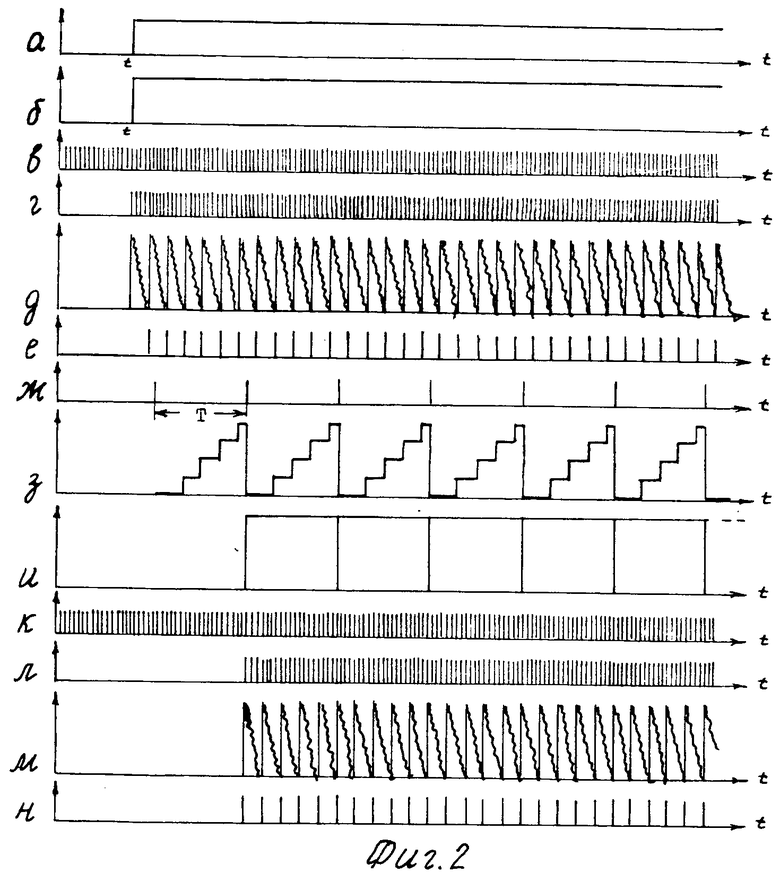

Известный преобразователь относится к устройствам на основе цифрового модулятора периода и реализует операцию преобразования с учетом дробной части периода. Причем конкретно поправка периода выходной частоты осуществляется на величину

Tвых.сч1+(ΔTн-ΔTк)

Tвых.сч1+(ΔTн-ΔTк) . (2)

. (2)

Однако известный преобразователь имеет относительно низкую точность реализации операции преобразования. Это обусловлено тем, что в зависимости от соотношения значений ΔТн и Δ Тк величина поправки периода выходной частоты может изменяться в пределах от 0 до 2Тэт2. В соответствии с принципом действия известного преобразователя после каждого очередного пересчета информации в третьем счетчике сигналами с выхода блока сдвига фазы на выходе первого элемента И появляется сигнал, который далее задерживается на величину ΔТ, определяемую выражением (2). Но правильная реализация коррекции периода выходного сигнала осуществляется лишь для случая, если поправка периода ΔТ лежит в пределах от 0 до Тэт2. В интервале Тэт2 < ΔT≅Тэт2 появляется погрешность за счет того, что за время задержки сигнала с выхода первого элемента И на величину, большую Тэт2, на вход третьего счетчика может поступить сигнал с выхода блока сдвига фазы, что нежелательно и приводит к погрешности преобразователя.

Правильная работа осуществляется только в том случае, когда определенным образом синфазированные сигналы с выхода блока сдвига фазы начинают поступать на вход третьего счетчика только после появления сигнала с выхода блока задержки.

Целью изобретения является повышение точности преобразователя.

Цель достигается тем, что в преобразователе цифрового кода в частоту следования импульсов, содержащем первый, второй и третий счетчики импульсов, первый и второй регистры памяти, блок коррекции, блок задержки сигналов, блок сдвига фазы, первую, вторую и третью группы элементов И, первый, второй, третий, четвертый и пятый триггеры, первый, второй третий, четвертый, пятый и шестой элементы И, первый, второй, третий, четвертый и пятый элементы задержки, шины входного кода и управляющего сигнала, первую и вторую шины импульсов эталонной частоты, шину временного интервала и выходную шину, причем вход третьего элемента задержки объединен с входом второго триггера, с первым входом пятого элемента И и подключен к выходу четвертого элемента И, а выход к счетному входу третьего триггера, разрядные входы первого регистра памяти являются шиной входного кода, а его выходы соединены с первыми входами первой группы элементов И, вторые входы которых подключены к выходу первого счетчика импульсов и объединены с входом первого триггера и с первым входом второго элемента И, а выходы подключены к разрядным входам первого счетчика импульсов, счетный вход которого подключен к выходу первого элемента И, первый вход которого является шиной управляющего сигнала, а второй первой шиной импульсов эталонной частоты, первый вход третьего элемента И является второй шиной импульсов эталонной частоты, а второй его вход соединен с единичным выходом четвертого триггера, второй вход второго элемента И подключен к единичному выходу второго триггера, а выход к счетному входу второго счетчика импульсов, разрядные выходы которого соединены соответственно с первыми входами второй группы элементов И, вторые входы которых через второй элемент задержки объединены с входом установки в исходное состояние второго регистра памяти, с первым входом четвертого элемента И и являются шиной временного интервала, которая через первый элемент задержки соединена с входом установки в ноль второго счетчика импульсов, выходы второй группы элементов И подключены соответственно к разрядным входам второго регистра памяти, разрядные выходы которого подсоединены к первым входам третьей группы элементов И, выходы которых соединены соответственно с разрядными входами третьего счетчика импульсов, второй вход четвертого элемента подключен к единичному выходу первого триггера, а третий к нулевому выходу четвертого триггера, вход которого соединен с выходом пятого элемента И, второй вход которого подключен к единичному выходу третьего триггера, первый вход блока коррекции подключен к выходу первого счетчика импульсов, второй его вход является первой шиной импульсов эталонной частоты, третий вход второй шиной импульсов эталонной частоты, четвертый вход шиной временного интервала, а выходы блока коррекции соединены соответственно с первыми входами блока задержки сигналов, второй вход которого подключен к выходу шестого элемента И и объединен с входом четвертого элемента задержки, выход которого подключен к вторым входам третьей группы элементов И, а выход блока задержки сигналов является выходной шиной и подключен к первому входу блока сдвига фазы, второй вход которого соединен с выходом третьего элемента И, а его выход с первым входом шестого элемента И и со счетным входом третьего счетчика импульсов, разрядные выходы которого соединены с соответствующими вторыми входами шестого элемента И, третий вход второго элемента И подключен к единичному выходу пятого триггера, вход установки в "1" которого соединен через пятый элемент задержки с выходом первого счетчика импульсов, а вход установки в "0" объединен с входом установки в ноль второго счетчика импульсов, выход шестого элемента И подключен к входу обнуления блока сдвига фазы.

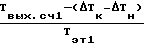

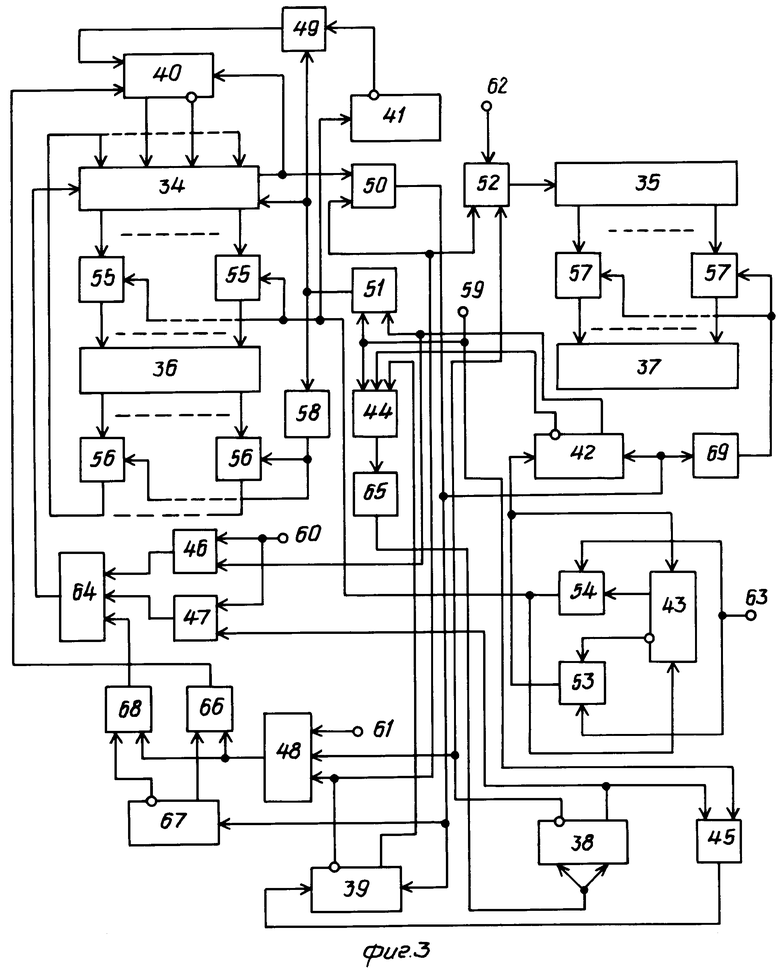

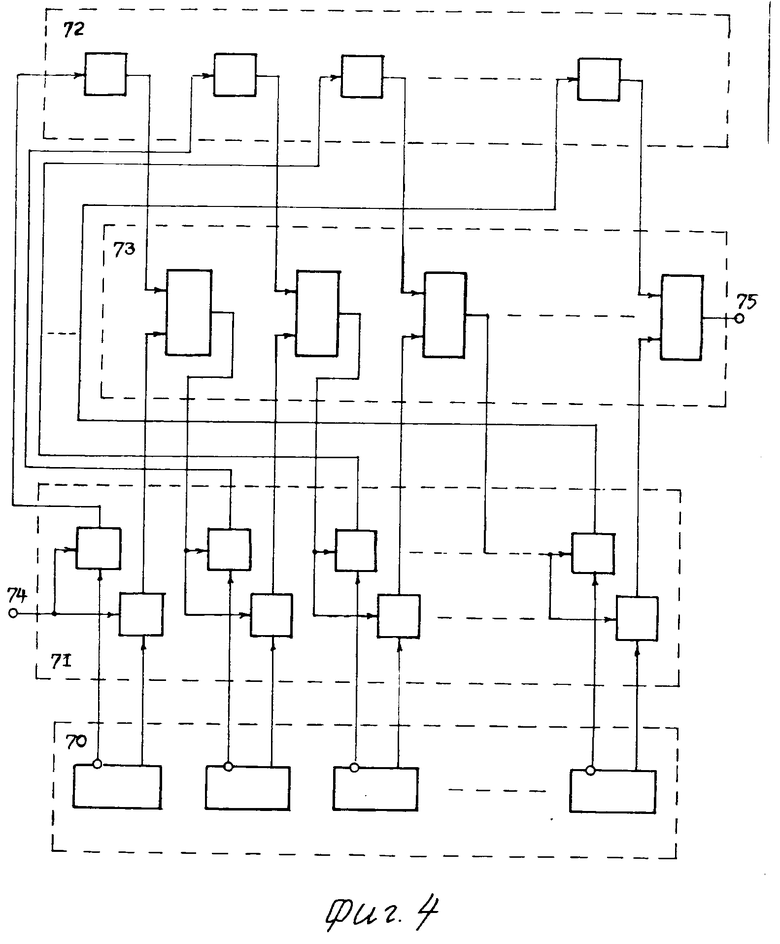

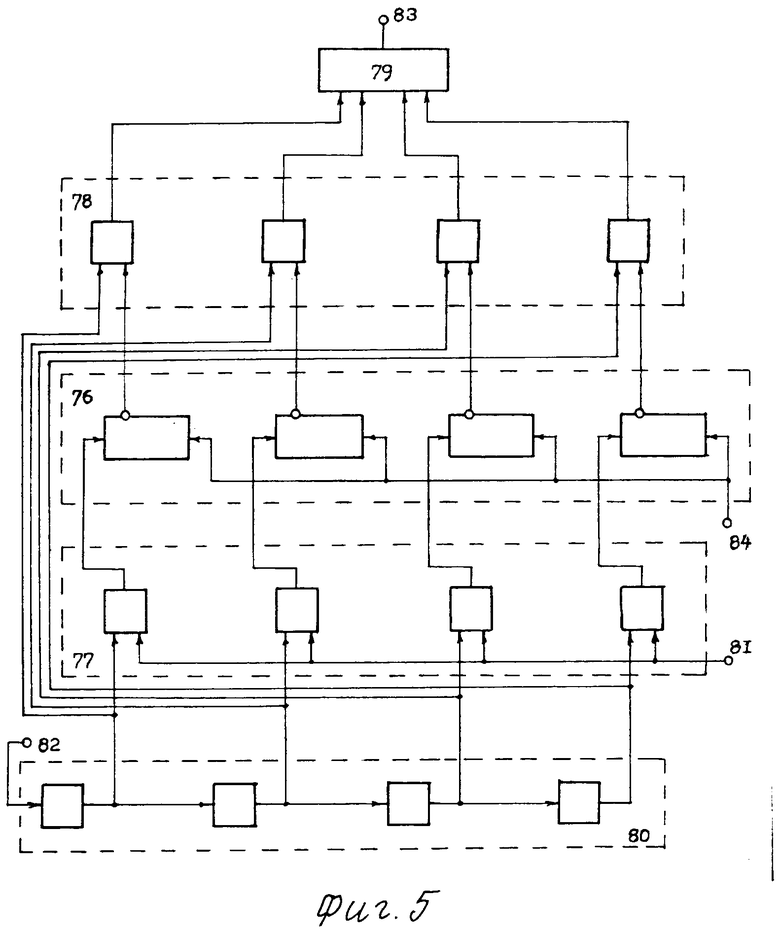

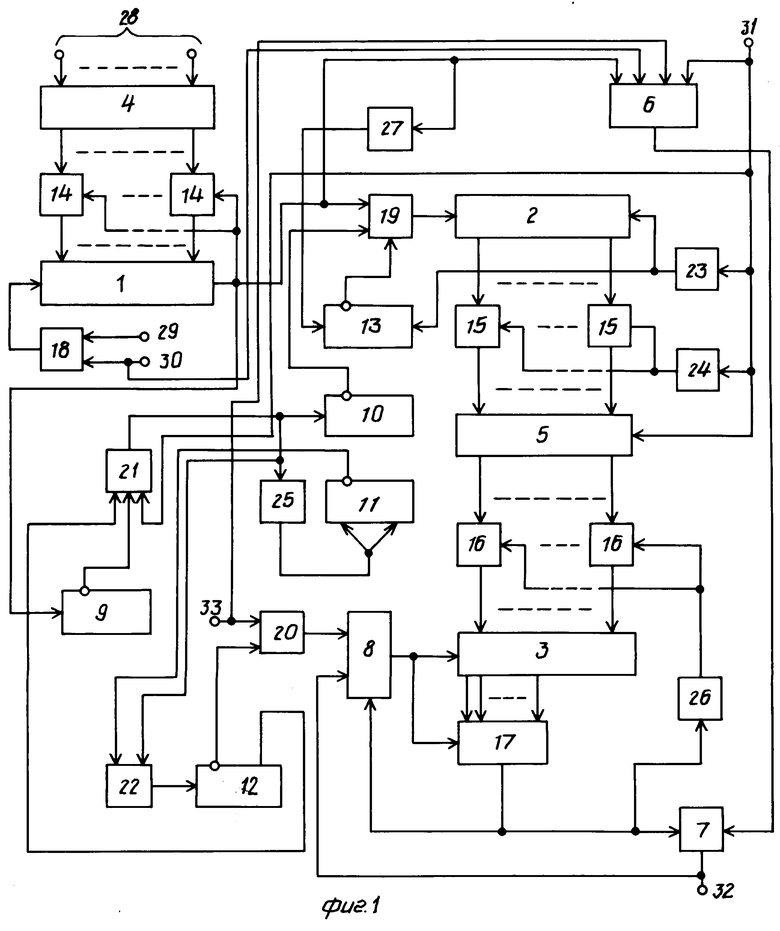

На фиг. 1 приведена структурная схема предлагаемого преобразователя цифрового кода в частоту следования импульсов; на фиг. 2 временная диаграмма, поясняющая принцип работы преобразователя; на фиг. 3 структурная схема блока коррекции; на фиг. 4 структурная схема блока задержки; на фиг. 5 структурная схема блока сдвига фазы.

Преобразователь цифрового кода в частоту следования импульсов содержит счетчики 1, 2, 3 импульсов, регистры 4, 5 памяти, блок 6 коррекции, блок 7 задержки сигналов, блок 8 сдвига фазы, триггеры 9-13, группы элементов И 14-16, элементы И 17-22, элементы 23-27 задержки, шины 28 преобразуемого кода, шину 29 управляющего сигнала, первую шину 30 импульсов эталонной частоты, шину 31 временного интервала, выходную шину 32 и вторую шину 33 импульсов эталонной частоты.

В преобразователе цифрового кода в частоту следования импульсов реализуется поправка выходного периода до обеспечения истинного его значения путем задержки выходного сигнала и сдвига фазы сигналов из последовательности с частотой Fэт2. Но это возможно осуществить лишь для ΔТ со знаком плюс. Для обеспечения введения поправки в выходной период при разных соотношениях ΔТн и Δ Тк в процессе подсчета импульсов частоты Fвых.сч1 вторым счетчиком предусмотрен запрет в подаче одного импульса из последовательности Fвых.сч1 на вход упомянутого счетчика. При этом изменяется значение поправки. В этом случае целое количество импульсов частоты Fвых.сч1, зафиксирвоанное во втором счетчике, равно

N = N1-1 ent

= N1-1 ent -1 (3) и соответствующее ему значение выходного периода определяется как

-1 (3) и соответствующее ему значение выходного периода определяется как

T = T

= T ent

ent -1

-1 = Tэт2·ent

= Tэт2·ent - Tэт2= Tz1-Tэт2. (4)

- Tэт2= Tz1-Tэт2. (4)

Значение поправки в выходной период в этом случае определяется в результате вычитания из действительного значения периода Тz2 значения Тz1, полученного из выражения (4):

ΔT′= Tz2-T = Tz1+

= Tz1+  ·(ΔTк-ΔTн)-Tz1+Tэт2=

·(ΔTк-ΔTн)-Tz1+Tэт2=

Tвых.сч1+(ΔTк-ΔTн)

Tвых.сч1+(ΔTк-ΔTн) . (5)

. (5)

В преобразователе и реализуется поправка значения периода выходных сигналов на величину ΔТ' в соответствии с выражением (5).

Величина ΔТ' всегда имеет знак плюс при любых соотношениях ΔТн и ΔТк.

При Δ Тк≥ΔТн значение периода Твых.сч1 в выражении (5) складывается с разностью ΔТк- ΔТн, а при Δ Тк< Тн из значения периода Т вых.сч1 вычитается разность ΔТн- ΔТк.

Преобразователь кода в частоту следования импульсов работает следующим образом.

Перед началом цикла преобразования все счетчики, регистры памяти и триггеры установлены в исходное нулевое состояние путем подачи сигнала на их входы установки в ноль. Затем на шины 28 входного кода в момент t1подаются сигналы входного преобразуемого кода, который запоминается в регистре 4 памяти (фиг. 2а). Одновременно на шину 29 подается управляющий сигнал (фиг. 2б), отпирающий элемент И 18 для импульсов эталонной частоты, подаваемых на шину 30. Сигналы, подаваемые на шину 30, представлены на фиг. 2в, а сигналы на счетном входе счетчика 1 на фиг. 2г. В процессе функционирования информация в счетчике 1, который работает в режиме вычитания, имеет вид, представленный на фиг. 2д. При этом сигналы с выхода счетчика 1 (фиг. 2е) подается на вход элемента И 19, на вход триггера 9 и на управляющие входы группы элементов И 14 переноса. В результате этого информация, запомненная в регистре 4 памяти, периодически передается через элементы И 14 в счетчик 1, образуя его исходную уставку.

Таким образом, в зависимости от величины исходной уставки на выходе счетчика 1 устанавливается вполне определенная частота, которая обратно пропорциональна величине кода N. Это определяется следующим образом. Период последовательности импульсов на выходе счетчика 1, который работает в режиме вычитания, определяется выражением

Твых.сч.1=Тэт1 ˙N, (6) где Тэт1 период последовательности импульсов эталонной частоты, действующей на входе счетчика 1;

N число импульсов, соответствующих входному преобразуемому коду.

В частном представлении выражение (6) можно представить как

Fвых.сч1=  . (7)

. (7)

Величина Fэт1 характеризует собой эталонную частоту сигналов, подаваемых на вход счетчика 1, и является константой.

После появления первого сигнала на выходе счетчика 1 (фиг. 2е) триггер 9 переводится из нулевого состояния в единичное. При этом первый после момента переброса триггера 9 импульс, подаваемый на шину 31 (фиг. 2ж), проходит через элемент И 21, переводит триггер 10 и с задержкой триггер 11 в единичное состояние. В результате перевода триггера 10 в единичное состояние отпирается элемент И 19 для сигналов с выхода счетчика 1, которые начинают проходить на вход счетчика 2. Информация в счетчике 2 представлена на фиг. 2з. Информация в счетчике 2 накапливается до момента поступления следующего сигнала на шину 31, причем подача одного из импульсов частоты Fвых.сч1 на вход счетчика 2 запрещается. Это осуществляется с помощью триггера 13, элемента 27 задержки и элемента И 19. Сигнал из последовательности частоты F (подаваемый на шину 31) каждый раз устанавливает триггер 13 в нулевое состояние, запирая элемент И 19. При этом первый после подачи сигнала из последовательности F сигнал частоты Fвых.сч1 не проходит через элемент И 19, а, пройдя через элемент 27 задержки, устанавливает триггер 13 в единичное состояние. Все последующие сигналы частоты Fвых.сч1 проходят на вход счеатчика 2.

Количество импульсов с частотой Fвых.сч1, поступивших в течение периода Т на вход счетчика 2, определяется выражением (3). Одновременно с подачей сигнала на шину 31 блок 6 коррекции начинает определение сигнала поправки периода выходного сигнала в соответствии с выражением (5). С поступлением на шину 31 следующего импульса, информация, накопленная в счетчике 2, передается через группу элементов И 15 в регистр 5 памяти (фиг. 2и), где запоминается, а счетчик 2 обнуляется. В блоке 6 коррекции при этом определяется величина ΔТ' в соответствии с выражением (5), которая подается на вход блока 7 задержки сигналов. Необходимый временной сдвиг между моментом подачи информации и обнулением счетчика 2 осуществляется с помощью элементов 23 и 24 задержки. Далее процесс повторяется. С приходом каждого последующего импульса из последовательности с частотой следования F осуществляются обнуление регистра 5 памяти и передача запомненной в счетчике 2 информации в регистр 5 памяти, а также обнуление счетчика 2.

Необходимая задержка в подаче сигналов из последовательности Fэт2на вход счетчика 3 в данном случае осуществляется с помощью схемы, состоящей из триггеров 11, 12, элементов И 20, 22 и элемента 25 задержки. После подачи сигнала с выхода триггера 9 первый сигнал из последовательности с частотой F (сигнал, подаваемый на шину 31) проходит на выход элемента И 21. С выхода элемента И 21 он поступает через элемент 25 задержки на счетный вход триггера 11, переводя его из нулевого состояния в единичное. При этом сигнал с выхода элемента И 21 не проходит на выход элемента И 22, так как отпирающий сигнал с триггера 11 подается на его вход с задержкой в элементе 25 задержки. При поступлении следущюего сигнала на шину 31 сигнал с выхода элемента И 21 проходит на выход элемента И 22, переводя триггер 12 в единичное состояние. В результате открывается элемент И 20 и на вход счетчика 3 через блок 8 сдвига фазы начинают подаваться импульсы эталонной частоты с шины 33 (фиг. 2к) с частотой следования Fэт2. При этом сигналы на входе счетчика 3 представлены на фиг. 2л. С переводом триггера 12 в единичное состояние элемент И 21 запирается для сигналов, подаваемых на шину 31. В процессе функционирования преобразователя информация в счетчике 3 имеет вид, представленный на фиг. 2м. Выходные сигналы пересчета со счетчика 3 формируются на выходе многовходового элемента И 17, подключенного к разрядным выходам счетчика 3 таким образом, что он открывается для входных сигналов с частотой Fэт2 лишь в момент достижения в счетчике 3 единичной информации. В этот момент на его выходе появляется сигнал пересчета.

Указанные сигналы подаются на вход блока 7 задержки сигналов, на третий вход блока 8 сдвига фазы и через элемент 25 задержки на управляющие входы группы элементов И 16 переноса. В результате этого информация, запомненная в регистре 5 памяти, периодически передается через группу элементов И 16 в счетчик 3, образуя его исходную уставку, а также осуществляются задержка сигнала на величину ΔТ', вырабатываемую в блоке 6 коррекции, и запрет в подаче сигналов с выхода блока 8 сдвига фазы на счетный вход счетчика 3 до момента появления сигнала на выходе блока 7 задержки сигнала. Задержанные сигналы с выхода блока 7 задержки подаются на второй вход блока 8 сдвига фазы, снимая запрет в подаче сигналов на вход счетчика 3, и на выходную шину 32 устройства. На выходе блока 8 сдвига фазы вырабатываются при подаче сигналов с выхода блока 7 задержки сигналов сдвинутые по фазе сигналы с частотой Fэт2 таким образом, чтобы отсутствовал сдвиг по отношению к сигналам с выхода блока 7 задержки сигналов. В этом случае на выходе блока 7 задержки сигналов имеют место сигналы, период которых изменен на величину, вырабатываемую на выходе блока 6 коррекции. В зависимости от величины исходной уставки на выходе элемента И 17 устанавливается вполне определенная частота. При этом каждый последующий импульс частоты F осуществляет периодический сброс старой информации в регистре 5 памяти (фиг. 2и) и запись новой информации. При этом нетрудно установить, что значение выходной частоты прямо пропорционально входному преобразуемому коду.

Блок коррекции (фиг. 3) содержит счетчики 34, 35 импульсов, регистры 36, 37 памяти, триггеры 38-43, элементы И 44-54, группы элементов И 55-57 переноса, элемент 58 задержки, шину 59 сигналов с выхода счетчика преобразователя с частотой Fвых.сч1, шину 60 импульсов эталонной частоты Fэт1, шину 61 импульсов эталонной частоты Fэт2, шину 62 сигналов с частотой Fвых.сч1, шину 63 сигналов с частотой F, элемент ИЛИ 64.

В исходном состоянии счетчики, регистры и триггеры обнулены путем подачи сигнала на их входы установки в ноль. Первый импульс частоты F, подаваемый на шину 63, проходит через элемент И 54 на управляющие входы группы элементов И 55. Сигналы эталонной частоты Fэт1 через открытый элемент И 46 и элемент ИЛИ 64 проходят на вход счетчика 34, считатающий в прямом направлении. Каждый поступающий с шины 59 импульс частоты Fвых.сч.1 проходит через открытый элемент И 51 на вход установки в ноль счетчика и через элемент 58 задержки на управляющие входы группы элементов И 56. При этом информация в счетчике 34 сбрасывается, и затем подсчет импульсов осуществляется вновь. Такой счет производится до момента прихода сигнала частоты F (с шины 63), который через открытый элемент И 54 поступает на управляющие входы группы элементов И 55 и переводит триггеры 41 и 43 в единичное состояние. При этом из счетчика 34 в регистр 36 памяти переносится информация ΔТн/ΔТэт1, характеризующая интервал времени Тн с момента поступления импульса частоты F. Следующий за импульсом F импульс Fвых.сч1 обнуляет счетчик и через время задержки, определяемое элементом 58, заносит информацию ΔТн/ΔТэт1 из регистра 36 памяти опять в счетчик 34. Наряду с этим упомянутый сигнал из последовательности с частотой Fвых.сч1 проходит через открытый элемент И 49 на единичный вход триггера 40, переводя его в единичное состояние. В результате счетчик 34 переводится в режим работы "вычитание". Далее осуществляется периодическое считывание записанной в счетчике 34 информации. Причем по достижении нулевого значения в счетчике 34 в процессе считывания на его выходе вырабатывается сигнал, который переводит триггер 40 в нулевое состояние, в результате чего счетчик переводится в режим работы "сложение". Далее в счетчике 34 накапливается разность по абсолютному значению до момента прихода импульса из последовательности Fвых.сч1. С приходом следующего импульса из последовательности Fвых.сч1 осуществляются сброс информации в счетчике 34, перевод его в режим работы "вычитание" и запись в него информации из регистира 36 памяти. Далее процесс повторяется. Если до момента прихода следующего импульса из последовательности Fвых.сч1 поступает импульс из последовательности частоты F, который теперь уже проходит через открытый элемент И 53, он осуществляет перевод триггеров 42 и 43 в единичное состояние. В результате элементы И 46 и 51 запираются соответственно для сигналов Fэт1 и Fвых.сч1, и в счетчике фиксируется абсолютное значение разности ΔТк/Тэт1- ΔТн/Tэт1. Состояние триггера 40 при этом характеризует знак указанной разности.

Далее в зависимости от знака полученной разности осуществляется получение суммы или разности полученного результата с периодом Твых.сч1. Это осуществляется следующим образом. С переводом триггера 42 в единичное состояние под действием сигнала из последовательности F открывается элемент И 44 для сигналов с частотой Fвых.сч1. При этом первый после момента перевода триггера 42 в единичное состояние импульс из последовательности Fвых.сч1 проходит на выход элемента И 44 и через время, определяемое элементом 65 задержки, переводит триггер 38 в единичное состояние. Открываются элементы И 47 и 45, и на вход счетчика 34 начинают поступать импульсы эталонной частоты, которые подаются до момента поступления следующего сигнала из последовательности частоты Fвых.сч1. Следующий импульс из последовательности Fвых.сч1проходит через открытые элементы И 44 и 45. В результате триггер 39 переводится в "1", триггер 38 с задержкой в нулевое состояние. При этом запирается эле- мент И 47, прекращается подача импульсов Fэт1 и в счетчике 34 фиксируется информация

либо

(8)

либо  в зависимости от знака ( ΔТк ΔТн), который определяется состоянием триггера 40.

в зависимости от знака ( ΔТк ΔТн), который определяется состоянием триггера 40.

Одновремено с запиранием элемента И 47 открывается элемент И 48 для сигналов с частотой Fэт2, на входы которого подаются отпирающие уровни с выходов триггеров 38 и 39. При этом первый импульс с выхода элемента И 48 проходит через открытый элемент И 66 и устанавливает триггеры 40 и 67 в единичное состояние (или подтверждает единичное состояние триггера 40). Счетчик 34 либо переводится, либо подтверждается в режиме работы "вычитание", и открывается элемент И 68 для сигналов Fэт2 на вход счетчика 34. Одновременно с этим открывается элемент И 52 для сигналов n˙ Fвых.сч1. которые начинают проходить на вход счетчика 35. Сигналы из последовательности Fэт2 считывают информацию, записанную в счетчик 34, до момента его обнуления. В этот момент на выходе счетчика 34 вырабатывается сигнал, который переводит триггеры 39, 40, 41, 42 и 67 в нулевое состояние. Счетчик 34 переводится в режим работы "сложение", и элементы И 48, 49, 52, 68 запираются, а элементы И 46, 51, 66 отпираются, В результате в счетчике 35 фиксируется результат с точностью до постоянного множителя в соответствии с выражением (8), который спустя время, определяемое элементом 69 задержки, переносится в регистр 37 памяти, где и запоминается. Выходы регистра 37 памяти являются выходами блока коррекции.

Блок 7 задержки сигналов (фиг. 4) состоит из триггерного регистра 70, группы 71 элементов И, совокупности элементов 72 задержки, группы 73 элементов ИЛИ, шины 74 входного сигнала и выходной шины 75.

Задержка входного импульса, который подается с выхода элемента И 17 преобразователя кода в частоту следования импульсов, осуществляется, начиная со старшего разряда. В качестве регистра памяти используется регистр 37 блока 6 коррекци. В каждом разряде имеются два элемента И, входящие в группу 71 элементов И, один из которых связан с единичным, а другой с нулевым выходом соответствующего триггера регистра. Кроме того, на каждый разряд приходится один элемент задержки, входящий в группу 72 элементов задержки, и один элемент ИЛИ, входящий в группу 73 элементов ИЛИ. Величина задержки, которую обеспечивает элемент задержки в каждом разряде, устанавливается в соответствии с весовым значением двоичного разряда, т.е. для старшего разряда является максимальной и далее уменьшается по двоичному закону. Входной импульс с шины 74 поступает на входы двух элементов И, каждый из которых связан соответственно с единичным и нулевым выходами триггера старшего разряда регистра памяти. Если упомянутый триггер находится в состоянии "1", то входной сигнал проходит на вход элемента задержки, где задерживается и далее через элемент ИЛИ поступает на входы элементов И следующего разряда. Если триггер старшего разряда находится в нулевом состоянии, то входной сигнал проходит через элемент И, связанный с нулевым выходом, минуя элемент задержки, и далее через элемент ИЛИ поступает в следующий разряд.

В последующих разрядах прохождение сигнала осуществляется аналогично описанному выше. Таким образом, на выходной шине 75 имеется задержанный сигнал в соответствии с кодом, записанным в регистре памяти. Далее задержанный сигнал подается на выход преобразователя кода в частоту, а также на вход блока 8 сдвига фазы, который сдвигает по фазе сигналы из последовательности с частотой Fэт2.

Блок 8 сдвига фазы (фиг. 5) состоит из триггерного регистра 76, первой группы 77 элементов И, второй группы 78 элементов И, элемента ИЛИ 79, совокупности элементов 80 задержки, шины 81 входного сигнала, шины 82 импульсов эталонной частоты Fэт2, выходной шины 83 и шины 84 сигнала с выхода элемента И 17 преобразователя кода в частоту.

Входной сигнал с выхода блока 7 задержки преобразователя кода в частоту подается с шины 81 на первые входы элементов И группы 77 элементов И, на вторые входы которых поступают сигналы эталонной частоты Fэт2 с шины 82, последовательно задерживаемые элементами задержки из совокупности элементов 80 задержки. При этом на вход первого элемента И группы 77 элементов И поступает сигнал эталонной частоты, задержанный одним элементом задержки на величину Δ t, на вход второго элемента И группы 77 элементов И поступает сигнал эталонной частоты, задержанный двумя элементами задержки на величину 2 Δt и т. д. При поступлении сигнала на шину 81 с выхода блока 7 задержки преобразователя кода в частоту происходит его совпадение с одним из задержанных сигналов последовательности Fэт2 и на выход соответствующего элемента И из группы 77 элементов И проходит сигнал, который переводит в "1" связанный с элементом И триггер регистра 76. В результате открывается соответствующий элемент И из группы 78 элементов И для задержанных сигналов. При этом на выход открытого элемента И проходят задержанные на соответствующую величину сигналы эталонной частоты Fэт2, которые далее через элемент ИЛИ 79 проходят на выходную шину 83.

При подаче сигнала на шину 84 (вход обнуления) с выхода элемента И 17 преобразователя кода в частоту на все триггеры регистра 76 подается сигнал установки в ноль и триггер, находившийся ранее в единичном состоянии, переводится в нулевое состояние. Прохождение задержанных сигналов эталонной частоты на выходную шину 83 при этом прекращается.

Технико-экономическое преимущество предложенного преобразователя цифрового кода в частоту следования импульсов по сравнению с известными заключается в том, что с помощью простых средств обеспечивается существенное повышение точности. Это обусловлено тем, что в предложенном преобразователе в результате введения связи между выходом шестого элемента И и входом обнуления блока сдвига фазы осуществляется запрет в подаче сигналов с выхода блока 8 сдвига фазы на вход счетчика 3 в интервале времени между моментом выработки сигнала пересчета на выходе элемента И 17 и моментом появления задержанного сигнала на выходе блока 7 задержки. В результат обеспечивается нормальная коррекция периода выходного сигнала во всем диапазоне возможных значений коррекции от 0 до 2Тэт2 (27Тэт2 период сигнала частоты Fэт2).

В известном устройстве отсутствует возможность запрета сигналов с выхода блока сдвига на вход счетчика 3 в интервале времени с момента появления сигнала пересчета с выхода элемента И 17 до момента появления задержанного сигнала с выхода блока 7 задержки. В результате нормальная коррекция периода выходного сигнала осуществляется лишь в диапазоне значений коррекции от 0 до Тэт2. При значениях коррекции в интервале Тэт2 < ΔT ≅2Tэт2 коррекция осуществляется с погрешностью, поскольку в данном случае возможно прохождение ложных сигналов на вход счетчика 3 до момента появления сигнала с выхода блока 7 задержки. Отсюда следует, что предложенный преобразователь цифрового кода в частоту следования импульсов обеспечивает существенное повышение точности (более чем на порядок) по сравнению с известными.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СТРЕЛОЧНЫМ ПЕРЕВОДОМ | 1998 |

|

RU2147008C1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1999 |

|

RU2160929C1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЗАДАННОГО ЧИСЛА ИМПУЛЬСОВ | 1993 |

|

RU2066921C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2042219C1 |

| ЭЛЕКТРОННЫЙ ПРЕОБРАЗОВАТЕЛЬ СИЛЫ ДЛЯ ВЕСОВ | 1991 |

|

RU2037793C1 |

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

Изобретение относится к автоматике, вычислительной технике, а также к импульсной и измерительной технике. Целью изобретения является повышение точности преобразователя. Цель достигается тем, что выход шестого элемента И подключен к входу обнуления блока сдвига фазы. Преобразователь цифрового кода в частоту следования импульсов содержит счетчики 1 - 3 импульсов, регистры 4, 5 памяти, блок 6 коррекции блок 7 задержки сигналов, блок 8 сдвига фазы, триггеры 9 - 13, группы элементов И 14 - 16, элементы И 17 - 22, элементы 23 - 27 задержки, шины 28 преобразуемого кода, шину 29 управляющего сигнала, первую шину 30 импульсов эталонной частоты, шину 31 временного интервала, выходную шину 32 и вторую шину 33 импульсов эталонной частоты. Блок 6 коррекции содержит два счетчика импульсов, два регистра памяти, шесть триггеров, десять элементов И, три группы элементов И переноса, элемент задержки, шину сигналов с выхода счетчика преобразователя с частотой Fвых.сч.1 , шину импульсов эталонной частоты Fэт1 , шину импульсов эталонной частоты Fэт2 , шину сигналов с частотой Fвых.сч.1, шину сигналов с частотой F, элемент ИЛИ. Блок задержки сигналов содержит триггерный регистр, группу элементов И, совокупность элементов задержки, группу элементов ИЛИ, шину входного сигнала и выходную шину. Блок сдвига фазы содержит триггерный регистр, первую группу элементов И, вторую группу элементов И, элемент ИЛИ, совокупность элементов задержки, шину входного сигнала, шину импульсов эталонной частоты Fэт2 , выходную шину и шину сигнала с выхода первого элемента И преобразователя кода в частоту. 5 ил.

ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий первый третий счетчики импульсов, первый и второй регистры памяти, блок коррекции, блок задержки сигналов, блок сдвига фазы, первую третью группы элементов И, первый пятый триггеры, первый шестой элементы И, первый - пятый элементы задержки, шины входного кода и управляющего сигнала, первую и вторую шины импульсов эталонной частоты, шину временного интервала и выходную шину, вход третьего элемента задержки объединен с входом второго триггера, с первым входом пятого элемента И и подключен к выходу четвертого элемента И, а выход к счетному входу третьего триггера, разрядные входы первого регистра памяти являются шиной входного кода, а его выходы соединены с первыми входами первой группы элементов И, вторые входы которых подключены к выходу первого счетчика импульсов и объединены с входом первого триггера и с первым входом второго элемента И, а выходы подключены к разрядным входам первого счетчика импульсов, счетный вход которого подключен к выходу первого элемента И, первый вход которого является шиной управляющего сигнала, а второй первой шиной импульсов эталонной частоты, первый вход третьего элемента И является второй шиной импульсов эталонной частоты, а второй его вход соединен с единичным выходом четвертого триггера, второй вход второго элемента и подключен к единичному выходу второго триггера, а выход к счетному входу второго счетчика импульсов, разрядные выходы которого соединены соответственно с первыми входами второй группы элементов И, вторые входы которых через второй элемент задержки объединены с входом установки в исходное состояние второго регистра памяти, с первым входом четвертого элемента И и являются шиной временного интервала, которая через первый элемент задержки соединена с входом установки в "0" второго счетчика импульсов, выходы второй группы элементов И подключены соответственно к разрядным входам второго регистра памяти, разрядные выходы которого подсоединены к первым входам третьей группы элементов И, выходы которых соединены соответственно с разрядными входами третьего счетчика импульсов, второй вход четвертого элемента И подключен к единичному выходу первого триггера, а третий к нулевому выходу четвертого триггера, вход которого соединен с выходом пятого элемента И, второй вход которого подключен к единичному выходу третьего триггера, первый вход блока коррекции подключен к выходу первого счетчика импульсов, второй его вход является первой шиной импульсов эталонной частоты, третий вход второй шиной импульсов эталонной частоты, четвертый вход шиной временного интервала, а выходы блока коррекции соединены соответственно с первыми входами блока задержки сигналов, второй вход которого подключен к выходу шестого элемента И и объединен с входом четвертого элемента задержки, выход которого подключен к вторым входам третьей группы элементов И, а выход блока задержки сигналов является выходной шиной и подключен к первому входу блока сдвига фазы, второй вход которого соединен с выходом третьего элемента И, а его выход с первым входом шестого элемента И и со счетным входом третьего счетчика импульсов, разрядные выходы которого соединены с соответствующими вторыми входами шестого элемента И, третий вход второго элемента И подключен к единичному выходу пятого триггера, вход установки в "1" которого соединен через пятый элемент задержки с выходом первого счетчика импульсов, а вход установки в "0" объединен с входом установки в "0" второго счетчика импульсов, отличающийся тем, что выход шестого элемента И подключен к входу обнуления блока сдвига фазы.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-06-19—Публикация

1992-05-21—Подача