Изобретение относится к автоматике и вычислительной технике и выполняет быстрый алгоритм преобразования дискретной функции, заданной 2n точками, по ортонормированной системе базисных показательных функций с основанием два и по Уолшу-Адамару.

Устройство может быть использовано в аппаратуре обработки образцов, сжатия информации при передаче данных, для анализа и обработки звуковых сигналов, для цифровой фильтрации и спектрального анализа случайных процессов.

Целью изобретения является расширение функциональных возможностей устройства за счет реализации преобразования ортонормированной системы базисных показательных функций с основанием два.

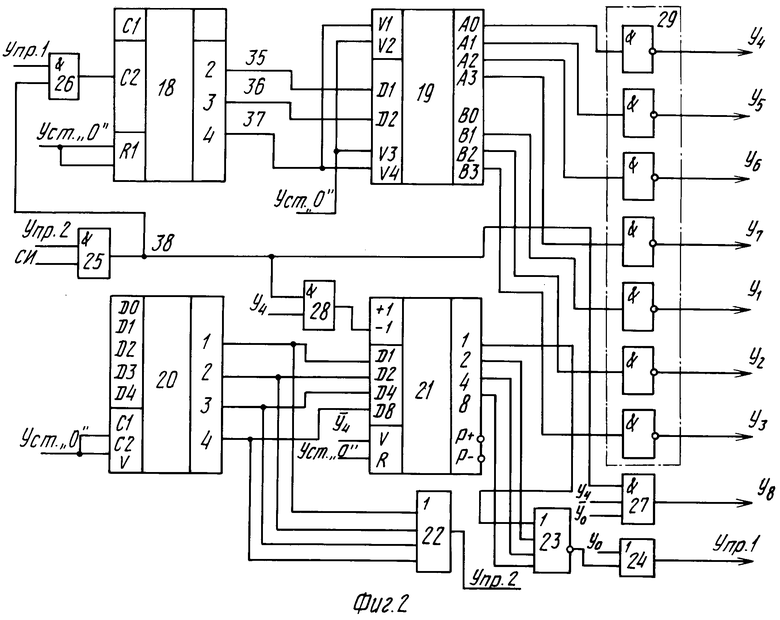

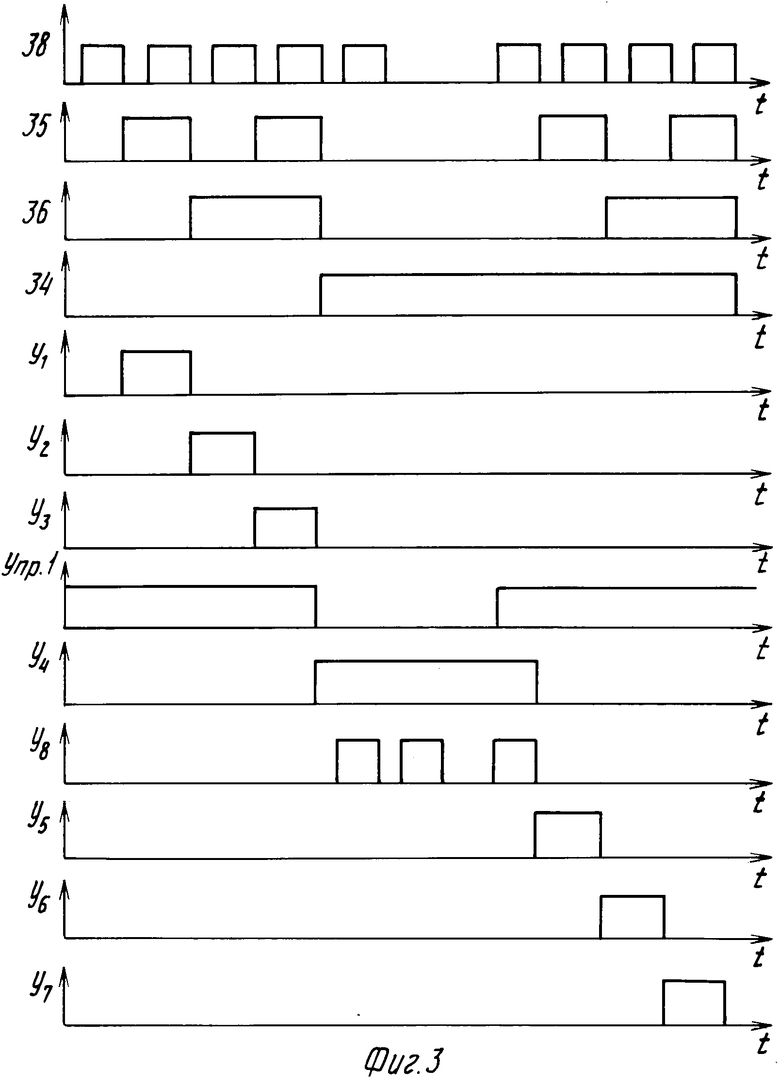

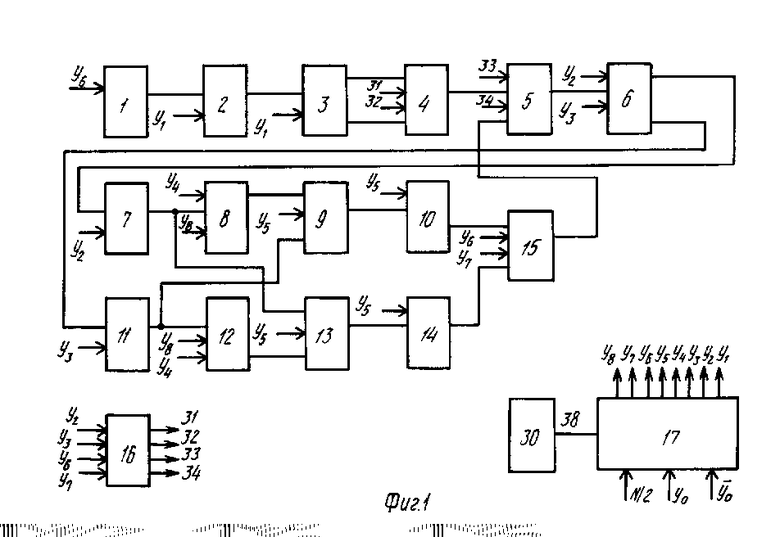

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока синхронизации; на фиг. 3 - временная диаграмма работы блока синхронизации.

Устройство и блок синхронизации (фиг. 1 и 2) содержат счетчик 1 адреса, блок 2 постоянной программируемой памяти, регистр 3 адреса, мультиплексор 4, блок 5 оперативной памяти, демультиплексор 6, первый регистр 7, первый сдвигающий регистр 8, вычитатель 9, третий и первый регистры 10 и 11, второй сдвигающий регистр 12, сумматор 13, четвертый регистр 14, мультиплексор 15, блок 16 элементов ИЛИ, блок 17 синхронизации, двоичный счетчик 18, дешифратор 19, сдвигающий регистр 20, реверсивный счетчик 21, элемент ИЛИ 22, элемент ИЛИ-НЕ 22, элемент ИЛИ 24, четыре элемента И 25-28, блок 29 элементов НЕ, генератор 30 тактовых импульсов, выходы 31-34 блока 16 элементов ИЛИ, выходы 35-37 счетчика 18, выход 38 генератора 30.

Счетчик 1 формирует адрес слова блока 2, в каждом слове которого записан адреса двух операндов, над которыми проводится вычисление i-й итерации. Адрес первого операнда записывается в младшие разряды регистра 3, адрес второго операнда - в старшие разряды. В блоке 5 хранятся элементы исходного массива, а также записываются промежуточные и конечные результаты обработки.

Сигнал yo подается на вход признака кода операции блока синхронизации и определяет режим работы устройства. Если сигнал yoсоответствует уровню логической "1", то устройство работает в режиме преобразования Уолша-Адамара, если yo соответствует уровню логического "0", то устройство работает в режиме преобразования ортонормированной системы базисных показательных функций с основанием два.

Предлагаемое устройство работает следующим образом.

При подаче сигнала "Установка О" все элементы устройства устанавливаются в состояние "О", кроме регистра 20, куда заносится значение N/2 (N - число элементов обрабатываемого массива). При этом вырабатывается сигнал "Упр. 2" на выходе элемента ИЛИ 22, который разрешает появление синхроимпульса на выходе элемента И 25. При поступлении первого синхроимпульса на счетный вход двоичного счетчика 18 по его заднему фронту он переходит в новое состояние. По сигналу y1блок 2 считывает информацию по адресу, поступающему из счетчика 1, и по заднему фронту y1 информация записывается в регистр 3 адреса. Второй синхроимпульс изменяет состояние счетчика 18, и появляется сигнал на выходе 36.

По сигналу y2 младшие разряды регистра 3 передаются через мультиплексор 4 в блок 5 оперативной памяти. Информация по заданному адресу считывается из блока 5 и через демультиплексор 6 по заднему фронту y2 записывается в регистр 7. По сигналу y3 старшие разряды регистра 3 передаются через мультиплексор 4 в блок 5 оперативной памяти, считанная информация передается через демультиплексор и записывается в регистр 11 по заднему фронту y3. По сигналу y4 информация, хранящаяся в регистрах 7, 11, передается в сдвигающие регистры 8, 12 соответственно. Информация, хранящаяся в регистре 20 блока синхронизации, передается в реверсивный счетчик 21.

На выходе элемента ИЛИ-НЕ 23 появляется сигнал логического "0", который поступает на второй вход элемента ИЛИ 24, на первый вход которого поступает сигнал y0. Если y0 соответствует уровню логического "0", то на выходе элемента ИЛИ 24 получают сигнал "Упр. 1", соответствующий уровню логического "0". Этот сигнал запрещает поступление синхроимпульса через элемент И 26 к счетному входу счетчика 18. По заднему фронту y8 происходит сдвиг информации, хранящийся в регистрах 8 и 12, вправо.

При прохождении синхроимпульса через элемент И 28 на вычитающий вход реверсивного счетчика 21 по переднему фронту происходит вычитание единицы. Этот процесс продолжается до тех пор, пока содержимое счетчика 21 не станет равным нулю. Тогда сигнал "Упр. 1" соответствует уровню логической "1" и разрешает поступление синхроимпульса через элемент И 26 на счетный вход счетчика 18.

Когда сигнал y0 соответствует уровню логической "1" "Упр. 1" всегда соответствует уровню логической "1" и разрешает прохождение синхроимпульсов на счетый вход счетчика 18. При этом сигнал y8 не вырабатывается.

По сигналу y5 информация из регистра 7 и 12 поступает на входы сумматора 13, а из регистров 11 и 8 информация поступает на входы вычитателя 9. По заднему фронту y5 результаты вычитания и сложения записываются в регистры 10 и 14. По сигналу y6 информация, хранящаяся в регистре 10, поступает на вход блока 5 через мультиплексор 4 и происходит запись информации. По заднему фронту сигнала y6 счетчик 1 адреса переходит в новое состояние.

По сигналу y7 содержимое регистра 14 передается на адресный вход блока 5 через мультиплексор 15, старшие разряды регистры 13 - на адресный вход блока 5 через мультиплексор 4, происходит запись информации. По заднему фронту y7 содержимое регистра 20 сдвигается влево. Этот цикл работы продолжается до тех пор, пока содержимое регистра 20 не станет равно нулю. Тогда уровень сигнала "Упр. 2" на выходе элемента ИЛИ 22, равный нулю, запрещает поступление последующих синхроимпульсов через элемент И 25 к блоку синхронизации. При этом устройство позволяет реализовать два вида преобразований: преобразование ортонормированной системы базисных показательных функций с основанием два по формуле

xl(i) = xl-1(i)+2kxl-1(j);

xl(j) = 2kxl-1(i)-xl-1(j), где l - номер итерации, l= 1, 2, . . . , logN;

k =  ;

;

xl(j), xl(i) - коэффициент преобразования, и преобразование Уолша-Адамара по формуле

xl(i) = xl-1(i)+xl-1(j);

xl(i) = xl-1(i)-xl-1(j).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1418776A1 |

| Устройство для приведения полиномов по модулям циклотомических полиномов | 1985 |

|

SU1357948A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство формирования телевизионного изображения с перемещением управляемого фрагмента | 1988 |

|

SU1644171A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

Устройство относится к автоматике и вычислительной технике и выполняет быстрый алгоритм преобразования дискретной функции, заданной 2n точками, по ортонормированной системе базисных показательных функций с основанием два и по Уолшу-Адамару. Целью изобретения является расширение функциональных возможностей устройства за счет реализации преобразования ортонормированной системы базисных показательных функций с основанием два. Устройство содержит счетчик 1 адреса, блок 2 постоянной программируемой памяти, регистр 3 адреса, мультиплексор 4, блок 5 опреративной памяти, демультиплексор 6, регистр 7, сдвигающий регистр 8, вычитатель 9, регистры 10, 11, 14, сдвигающий регистр 12, сумматор 13, мультиплексор 15, блок 16 элементов ИЛИ, блок 17 синхронизации. 3 ил.

УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО УОЛШУ-АДАМАРУ, содержащее сумматор, первый регистр, два сдвигающих регистра, блок элементов ИЛИ, блок синхронизации, отличающееся тем, что, с целью расширения функциональных возможностей за счет реализации преобразования ортонормированной системы базистных показательных функций с основанием два, устройство содержит с второго по четвертый регистры, вычитатель, счетчик адреса, блок постоянной программируемой памяти, блок оперативной памяти, регистр адреса, два мультиплексора, демультиплексор, причем выход счетчика адреса соединен с адресным входом блока постоянной программируемой памяти, выход которого соединен с информационным входом регистра адреса, выходы старших и младших разрядов которого соединены соответственно с первым и вторым информационными входами первого мультиплексора, выход которого соединен с адресным входом блока оперативной памяти, выход которого соединен с информационным входом демультиплексора, первый и второй выходы которого соединены с информационными входами первого и второго регистров соответственно, выход первого регистра соединен с информационным входом первого сдвигающего регистра, первым информационным входом сумматора, второй информационный вход которого соединен с выходом второго сдвигающего регистра, информационный вход которого соединен с выходом второго регистра и первым информационным входом вычитателя, второй информационный вход которого соединен с выходом первого сдвигающего регистра, выходы вычитателя и сумматора соединены с информационными входами третьего и четвертого регистров соответственно, выходы которых соединены с первым и вторым информационными входами второго мультиплексора, выход которого соединен с информационным входом блока оперативной памяти, первый выход блока синхронизации соединен с входом разрешения записи регистра адреса и входом разрешения считывания блока постоянной программируемой памяти, второй выход блока синхронизации соединен с первым входом блока элементов ИЛИ, входом разрешения записи первого регистра и первым управляющим входом демультиплексора, второй управляющий вход которого соединен с входом разрешения записи второго регистра, третьим выходом блока синхронизации, вторым входом блока элементов ИЛИ, первый и второй выходы которого соединены с первым и вторым управляющими входами первого мультиплексора, входы разрешения записи первого и второго сдвигающих регистров соединены с четвертым выходом блока синхронизации, пятый выход которого соединен с управляющими входами сумматора и вычитателя и входами разрешения записи третьего и четвертого регистров, первый и второй управляющие входы второго мультипликсора соединены соответственно с шестым и седьмым выходами блока синхронизации и третьим и четвертым входами блока элементов ИЛИ, третий и четвертый выходы которого соединены с первым и вторым управляющими входами соответственно блока оперативной памяти, входы управления сдвигом первого и второго сдвигающих регистров соединены с восьмым выходом блока синхронизации, шестой выход которого соединен со счетным входом счетчика адреса, вход признака кода операции устройства соединен с одноименным входом блока синхронизации.

Авторы

Даты

1994-04-30—Публикация

1989-08-17—Подача