Изобретение относится к области автоматики и вычислительной техники и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП с программным управлением, допускающих наращивание при расширении числа выполняемых функций.

Цель изобретения - повышение надежности и расширение области применения устройства.

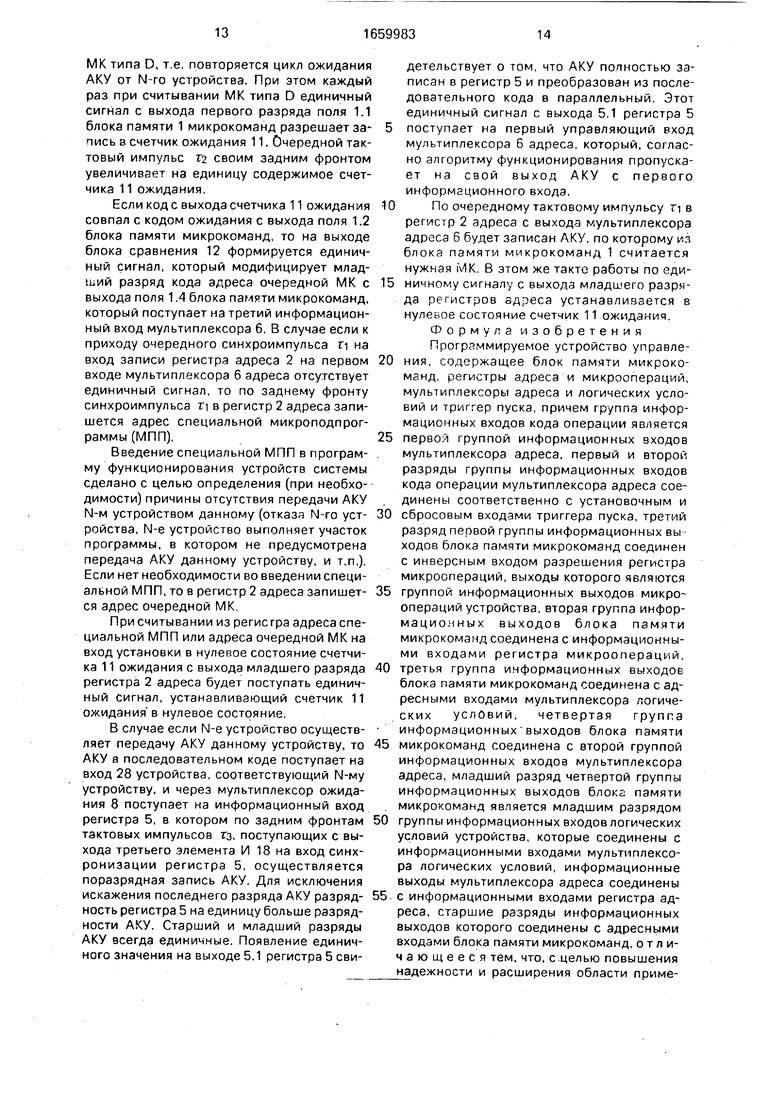

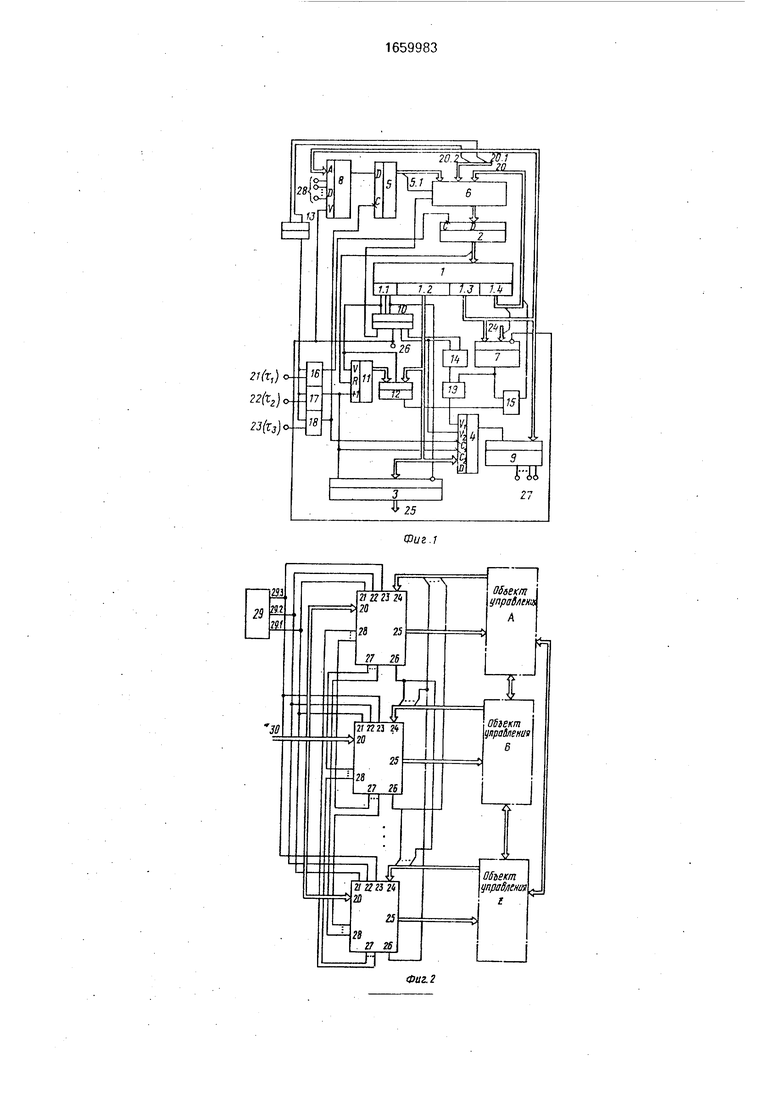

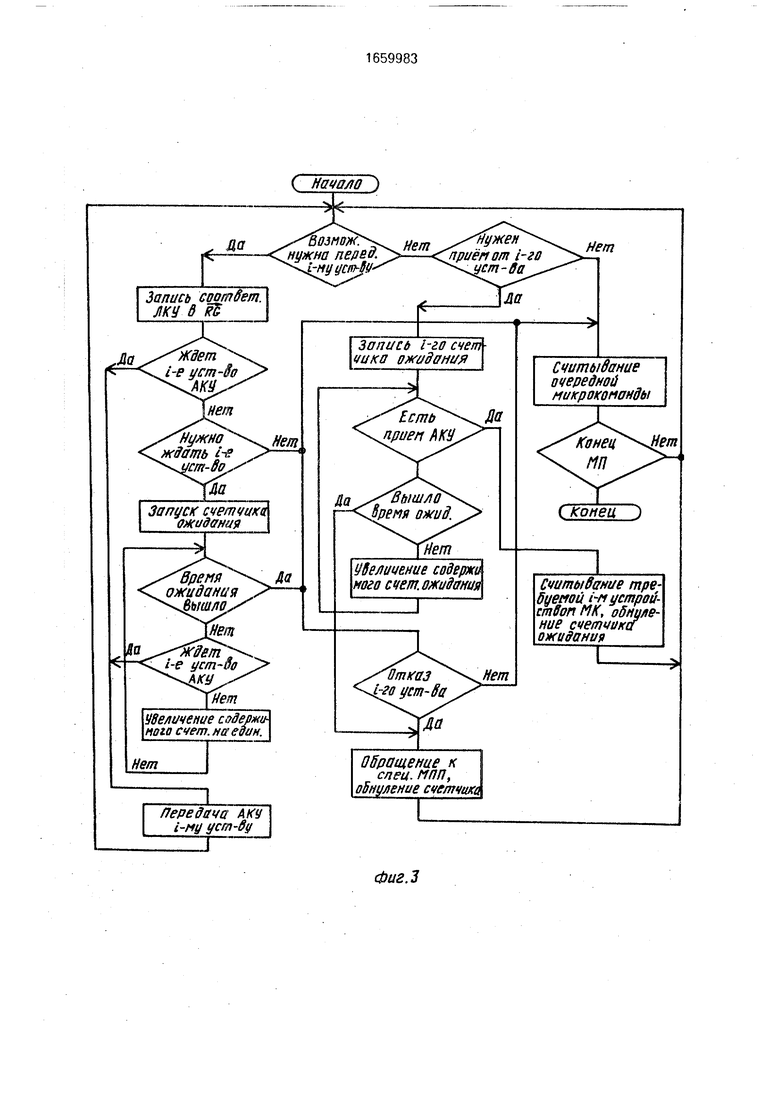

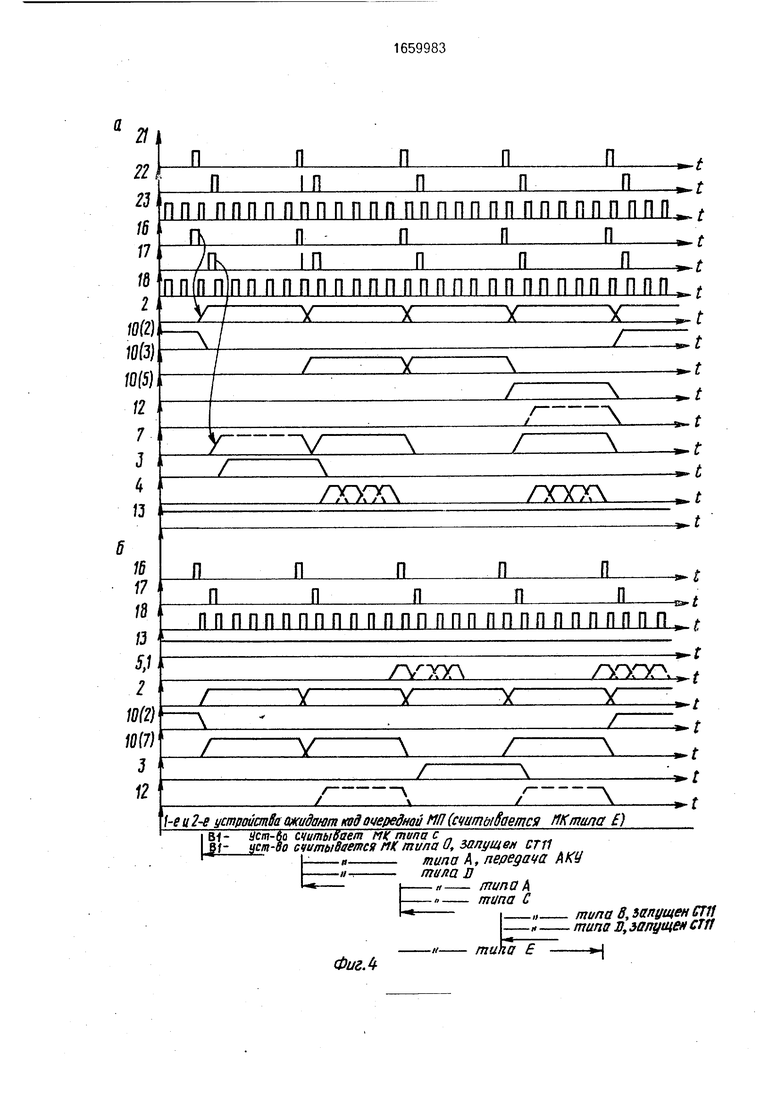

На фиг. 1 представлена функциональная схема программируемого устройства управления; на фиг.2 - функциональная схема отказоустойчивой системы управления, построенной на базе программируемых устройств управления; на фиг.З - блок-схема алгоритма функционирования программируемого устройства управления; на фиг.4 представлены временные диаграммы работы двух программируемых устройств управления распределенной отказоустойчивой системы управления.

Устройство (фиг.1) содержит блок 1 памяти микрокоманд, регистр адреса 2, регистр микроопераций 3, регистр сдвига передачи 4, регистр сдвига ожидания 5, мультиплексор адреса 6, мультиплексор логических условий 7, мультиплексор ожидания 8, демультиплексор 9 передачи, дешифратор 10 признака, счетчик 11 ожидания, блок 12 сравнения, триггер 13 пуска, первый 14 и второй 15 элементы ИЛИ, первый 16 - четвертый 19 элементы И, информационные входы 20 кода операции, первый

О

ел ю ю

00

и

21 - третий 23 входы синхронизации, информационные входы 24 логических условий, информационные выходы 25 микроопераций, управляющий выход состояния 26, информационные выходы передачи 27, информационные входы ожидания 28, генератор 29 тактовых импульсов.

Назначение основных функциональных элементов программируемого устройства управления.

Блок 1 памяти микрокоманд предназначен для хранения кодов МК и имеет четыре выхода. С выхода 1.1 поля признака МК считывается код признака МК, который декодируется дешифратором 10 признака. С выхода поля 1.2 в режиме управления считывается код микроопераций. В режиме передачи АКУ с выхода 1.2 считывается АКУ, который записывается в регистр сдвига 4 передачи, или код ожидания, который поступает на второй информационный вход блока сравнения 12. В.режиме ожидания АКУ с выхода 1.2 считывается только код ожидания.

С выхода поля 1.3 считывается код логических условий, управляющий мультиплексором 7 логических условий. В режиме передачи (ожидания) АКУ L-му (от N-ro) модулю с выхода поля 1.3 считывается код L-ro (N-ro) модуля, С выхода поля 1.4 адреса-считывается адрес очередной МК в МП, младший разряд которого в дальнейшем может модифицироваться.

Регистр 2 адреса предназначен для хранения адреса очередной МК во время считывания ее из блока памяти 1 микрокоманд. Этот адрес поступает на информационные входы регистра 2 адреса с выхода мультиплексора 6 адреса. Запись в регистр 2 осуществляется по заднему фронту тактового импульса с выхода элемента И 16, который формирует его как конъюнкцию тактового импульса с выхода 29.1 генератора 29 тактовых импульсов (фиг.4) и сигнала с выхода триггера 13 пуска.

Регистр 3 микроопераций предназначен для хранения в режиме управления сигналов микроопераций, поступающих на информационные входы с выхода поля 1.2 микроопераций блока памяти 1 микрокоманд. Запись микроопераций в регистр 3 микроопераций осуществляется по заднему фронту тактового импульса, поступающего на вход синхронизации регистра 3 микроопераций с выхода элемента И 17. Этот импульс формируется как конъюнкция тактового импульса со второго выхода 29.2 генератора 29 тактовых импульсов и сигнала с выхода триггера 13 пуска. Кроме того, для записи в регистр 3 необходимо, чтобы

на инверсном управляющем входе регистра 3 отсутствовал единичный сигнал с выхода третьего разряда поля 1.1 блока памяти 1 микрокоманд. С выхода регистра 3 код микроопераций поступает на выходы 25 устройства.

Регистр 4 сдвига передачи предназначен для хранения в режиме передачи АКУ адресного кода управления, поступающего

0 с выходов поля 1.2 блока памяти 1 микрокоманд. Запись АКУ в регистр 4 сдвига передачи осуществляется по заднему фронту тактового импульса, поступающего на второй вход синхронизации регистра 4 сдвига

5 передачи с выхода элемента И 17, Кроме того, для записи АКУ в регистр 4 необходимо, чтобы на втором управляющем входе регистра 4 присутствовал единичный сигнал с третьего выхода дешифратора 10. Регистр

0 4 по заднему фронту тактового импульса, поступающего на первый вход синхронизации с выхода третьего элемента И 18, сдвигает информацию на один разряд вправо. Таким образом, АКУ преобразуется из па5 раллельного кода в последовательный. Для преобразования АКУ в последовательный код необходимо, чтобы на первом управляющем входе присутствовал единичный сигнал с выхода элемента И 19.

0 АКУ поразрядно поступает на информационный вход регистра 5 с выхода мультиплексора 8. Запись очередного разряда АКУ в регистр 5 осуществляется по заднему фронту тактового импульса с выхода эле5 мента И 18, этим же синхроимпульсом с выхода элемента И 18 вся информация, записанная в регистре 5, сдвигается вправо на один разряд.

Мультиплексор адреса осуществляет

0 передачу на свой выход со своего первого, второго, третьего информационных входов соответственно либо АКУ (АКу) с выхода регистра 5, либо кода новой операции (Акоп) с информационного входа 20 кода операций,

5 либо адреса очередной МК (Ао) с выхода поля 1.4 адреса блока памяти 1 микрокоманд и элемента ИЛИ 15. На первый и второй адресные входы мультиплексора 6 поступают соответственно: сигнал переда0 чи АКУ (yi) с выхода 5.1 регистра 5, сигнал микрооперации ожидания кода очередной МП (у2) со второго выхода дешифратора 10 состояний. Функция, реализуемая мультиплексором 5 адреса, описывается выраже5 нием

Авых У1 АКу + У2 Акоп + У1 У2 Ао.

Мультиплексор 7 логических условий осуществляет передачу на выход со своих информационных входов значения логического условия со входа 24 логических уеловий (в случае считывания МК, ветвление младшего разряда с выхода поля 1.4 адреса блока памяти 1 микрокоманд). Мультиплексор 7 логических условий управляется кодом логических условий (в линейных МК он нулевой), поступающим с выхода поля 1.3 блока памяти 1 микрокоманд. Кроме того, на выходе мультиплексора 7 формируется нулевой сигнал в случае наличия на его инверсном управляющем входе единичного сигнала с седьмого выхода дешифратора 10.

Мультиплексор 8 осуществляет передачу на свой выход со своего информационного входа АКУ со входа 28 ожидания модуля. Мультиплексор 8 управляется кодом модуля, поступающим с выхода поля 1.3 блока памяти 1 микрокоманд. Кроме того, на выходе мультиплексора 8 формируется нулевой сигнал в случае отсутствия единичного сигнала с седьмого выхода дешифратора 10 на управляющем входе мультиплексора 8.

Демультиплексор 9 передачи осуществляет передачу на один из своих выходов со своего информационного входа АКУ с выхода регистра 4. Демультиплексор 9 управляется кодом, поступающим с выхода поля 1.3 блока памяти 1 микрокоманд.

Дешифратор 10 предназначен для преобразования трехразрядного кода с выхода поля 1.1 блока памяти 1 микрокоманд в унитарный код управления. Со второго выхода дешифратора 10 считывается сигнал ожидания кода очередной МП, управляющий работой мультиплексора 6. С третьего выхода считывается сигнал микрооперации передачи АКУ, по которому осуществляется запись АКУ в регистр 4. С пятого выхода считывается сигнал ожидания передачи АКУ. На седьмом выходе дешифратора 10 формируется сигнал ожидания АКУ. Этот сигнал поступает на выход 26.

Счетчик 11 предназначен для подсчета числа тактов, в течение которых данный модуль ожидает либо L-й модуль для передачи ему АКУ, либо модуль для приема от него АКУ. Счетчик 11 увеличивает свое содержимое на единицу по заднему фронту тактового импульса, поступающего на счетный вход счетчика 11с выхода второго элемента И 17. При наличии на управляющем входе счетчика 11 сигнала с выхода первого разряда поля 1.1 блока памяти 1 микрокоманд счетчик 11 устанавливается в исходное состояние единичным сигналом с выхода младшего разряда регистра 2 адреса.

Блок сравнения 12 предназначен для сравнения в режимах передачи и ожидания АКУ кода ожидания с выхода поля 1.2 блока памяти 1 микрокоманд и числа тактов ожидания с выхода счетчика 11 при наличии на управляющем входе блока сравнения 12 единичного сигнала с выхода первого раз- ряда поля 1.1 блока 1 памяти микрокоманд. 5Триггер 13 пуска управляет синхронизацией модуля. Он устанавливается в единичное состояние сигналом пуска со входа 20.1 устройства. Единичный сигнал с выхода триггера 13 поступает на первые входы эле10 ментов И 16, 18, разрешая прохождение через них тактовых импульсов с соответствующих выходов генератора 29.

Триггер 13 пуска устанавливается в нулевое (исходное) состояние при поступлен5 ни на его R-вход единичного сигнала с входа 20.2 устройства.

Устройство работает следующим обря- зом.

В исходном состоянии генератор 29 вы0 рабатывает на выходах 29.1, 29.2 и 29.3 последовательности тактовых импульсов, причем период следования импульсов с выходов 29.1 и 29.2 в k раз больше периода следования импульсов с выхода 29.3 (фиг.4).

5В исходном состоянии все элементы устройства находятся в режиме ожидания кода операции программного уровня от устройства управления верхнего уровня. При этом, все элементы памяти установле0 ны в ноль. Из блока памяти считывается содержимое нулевой ячейки (с нулевым адресом) в соответствии с таблицей - это МК типа Е. В ее поле 1.1 признака записан код (010), который декодируется дешифратором

5 10 признака как сигнал ожидания кода очередной МП. Этот единичный сигнал поступает на второй управляющий вход мультиплексора 6 адреса, который, согласно описанному алгоритму работы, пропу0 екает со своего выхода на информационный вход регистра 2 адреса код операции со входа 20 кодз операции модуля. В полях 1.2, 1.3, 1.4 нулевой ячейки записаны нулевые коды. При этом мультиплексор 7 логических

5 условий по нулевому коду логических условий с выхода 1.3 блока памяти 1 микрокоманд пропускает на свой выход значение младшего разряда с выхода поля 1.4 адреса блока 1 памяти микрокоманд. Нулевой ад0 рее постоянно поступает на третий информационный вход мультиплексора 6 адреса. В таком исходном состоянии управляющая структура (фиг.2) будет находиться до поступления кода МП от устройства управ5 ления верхнего уровня на вход 20.

Каждое устройство может работать в следующих режимах.

1. Режим ожидания кода очередной МП. 2. Режим управления. 3. Режим переачи АКУ. 4. Режим ожидания АКУ.

Переход модуля из исходного состояния в режим ожидания кода очередной МП осуществляется по сигналу Пуск, поступающему на вход 20.1 пуска устройства. Со входа 20.1 сигнал Пуск поступает на S- вход триггера 13 пуска. Единичный сигнал с прямого выхода триггера 13 пуска открывает первый 16, второй 17 и третий 18 элементы И, разрешая прохождение тактовых импульсов соответственно с первого 21, второго 22 и третьего 23 входов устройства. Если к моменту появления на синхров- ходе регистра 2 адреса рассматриваемого устройства заднего фронта первого тактового импульса с выхода первого элемента И 16 на входе 20 код операции еще не появился, то в регистр 2 припишется нулевой адрес и из блока памяти 1 микрокоманд будет снова считываться МК типа Е. Так как в ее поле 1.2 микроопераций записан нулевой код, то по заднему фронту тактового импульса с выхода второго элемента И 17 регистр 3 микроопераций состояния не изменит. Со второго выхода дешифратора 10 по-прежнему будет считываться единичный сигнал ожидания кода очередной МП. Таким образом, устройство будет сколь угодно долго ожидать код МП на своем входе 20.

При появлении кода МП на входах 20 устройства этот код через мультиплексор 6 адреса записывается по заднему фронту г 1 в регистр 2 адреса и модуль переходит в режим управления. Из блока памяти 1 микрокоманд считывается первая МК нужной МП.

По заднему фронту тактового импульса Г2 с выхода второго элемента И 17 в регистр 3 микроопераций записывается микроопе- рационный код первой МК микропрограммы (в табл. МКтипаС).

По заднему фронту очередного тактового импульса с выхода первого элемента И 16 в регистр 2 с выхода мультиплексора 6 адреса записывается адрес очередной МК микропрограммы. Этот адрес поступает на третий информационный вход мультиплексора 6 адреса со старших разрядов выхода поля 1.4 блока памяти микрокоманд 1 (немодифицируемая часть) и выхода элемента ИЛИ 15 (модифицируемая часть).

В данном режиме из блока памяти 1 микрокоманд считывается либо линейная МК, либо МК ветвления. В линейной МК значение младшего разряда адреса очередной МК в МП определяется значением младшего разряда поля 1.4 адреса блока памяти

1 микрокоманд. В поле 1.3 логических условий линейных МК записан нулевой код. По этому коду мультиплексор 7 логических условий пропускает на свой выход, согласно

алгоритму своей работы, значение сигнала с младшего разряда выхода поля 1.4 блока памяти микрокоманд 1. В МК ветвления в поле 1.3 блока памяти микрокоманд 1 записан код логического условия, значение кото0 рого анализируется при формировании адреса очередной МК. По этому коду мультиплексор 7 пропускает со входа 24 логических условий устройства на свой выход значение нужного логического условия. В

5 режиме управления на выходе блока сравнения 12 единичный сигнал не появляется. Таким образом, в МК ветвления младший разряд адреса очередной МК в МП будет полностью определяться значением сигна0 ла на выходе мультиплексора 7 логических условий. По записанному в регистр 2 адресу из блока памяти 1 микрокоманд считывается очередная линейная МК или МК ветвления. Аналогичным образом устройство

5 реализует в требуемой последовательности МК выполняемой МП (операции).

Из режима управления устройство может перейти в любой другой режим.

При переходе в режим ожидания кода

0 очередной МП в поле 1.2 кода логических условий и поле 1.4 адреса формата последней МК выполнявшейся МП записываются нулевой код и в следующем такте из блока памяти 1 микрокоманд считывается нулевая

5 МК (МК типа Е), т.е. устройство переходит в описанное ранее состояние ожидания кода очередной МП. При необходимости передать информацию другому устройству системы рассматриваемое устройство из

0 режима управления переходит в режим передачи АКУ.

По заднему фронту очередного тактового импульса с выхода элемента И 16 (фиг.4) в регистр адреса 2 записывается адрес МК

5 типа А. На третьем выходе дешифратора 10 признака формируется единичный сигнал, который поступает на второй управляющий вход регистра 4 сдвига передачи, разрешая в него запись АКУ с выхода поля 1.2 блока

0 памяти 1 микрокоманд. Этот же сигнал с третьего выхода дешифратора 10 признака через первый элемент ИЛИ 14 поступает на первый вход четвертого элемента И 19. На адресный вход мультиплексора 7 логмче5 ских условий поступает код логического условия L-ro модуля. В случае если L-й модуль находится в состоянии ожидания АКУ, то на выходе мультиплексора 7 логических условий формируется единичный сигнал, который поступает на второй вход четвертого

элемента И 19. Единичный сигнал с выхода четвертого элемента И 19 поступает на первый управляющий вход регистра 4 сдвига передачи и разрешает преобразование AKY из параллельного кода в последовательный. По заднему фронту каждого тактового импульса с выхода третьего элемента И 18 происходит сдвиг информации, записанной в регистре 4 сдвига передачи, на един разряд. Таким образом, до поступления очередного тактового импульса с выхода первого элемента И 16 АКУ преобразуется из параллельного кода в последовательный.

АКУ в последовательном коде поступает на информационный вход демультиплексо- ра передачи 9 и проходит на выход, который соответствует коду L-ro модуля, поступающему на адресный вход демультиплексора передачи 9 с выхода поля 1.3 логических условий блока памяти 1 микрокоманд.

Также единичный сигнал с выхода мультиплексора 7 логических условий модифицирует младший разряд кода адреса поля 1.4 блока памяти 1 микрокоманд, который поступает на третий вход мультиплексора 6 адреса. Кроме того, единичный сигнал с выхода третьего разряда поля 1.1 блока памяти микрокоманд поступает на инверсный управляющий вход регистра 3 микрооперации. Поэтому АКУ, записанный в поле 1.2 блока памяти микрокоманд 1, в МК типа А не будет записан в регистр 3 микроопераций. В случае, если 1-й модуль не готов к приему АКУ, на выходе мультиплексора 7 логических условий формируется нулевой сигнал, который поступает на второй вход четвертого элемента И 19 и запрещает прохождение через него сигнала преобразования АКУ из параллельного кода в последовательный.

Нулевой сигнал с выхода мультиплексора 7 логических условий поступает на первый вход второго элемента ИЛИ 15. В МК типа А сигнал, поступающий на второй вход второго элемента ИЛИ 15, всегда нулевой, поэтому значение младшего разряда адреса очередной МК полностью определяется значением сигнала на первом входе второго элемента ИЛИ 15, следовательно, младший разряд кода адреса с выхода поля 1.4 адреса блока памяти 1 микрокоманд 11 не модифицируется. В результате на третьем входе мультиплексора адреса 6 сформирован адрес МК типа В, который по очередному тактовому импульсу с выхода первого элемента И 16 запишется в регистр 2 адреса с выхода мультиплексора 6.

В М К типа В на пятом выходе дешифратора 10 признака формируется единичный сигнал, который поступает через первый

элемент ИЛИ 14 на первый вход четвертого элемента И 19, единичный сигнал с выхода первого разряда поля 1.1 блока памяти микрокоманд 1 поступает на управляющие вхо- 5 ды счетчика 11 и блока сравнения 12. Этот сигнал разрешает запись в счетчик 11 ожидания и очередной тактовый импульс с выхода элемента-И 17 своим задним фронтом увеличивает на единицу содержимое счет10 чика 11. Код с выхода счетчика 11 поступает на первый информационный вход блока сравнения 12, на втором информационном входе которого присутствует код ожидания с выхода поля 1.2 блока памяти 1 микроко5 манд.

Если L-й модуль по-прежнему не перешел в режим ожидания АКУ, то на выходе мультиплексора 7 логических условий присутствует нулевой сигнал, который запре0 щает прохождение единичного сигнала через четвертый элемент И 19 и не разрешает преобразование АКУ в последовательный код в регистре 4 сдвига передачи. Также нулевой сигнал с выхода мультиплексора 7

5 логических условий поступает на первый вход второго элемента ИЛИ 15. Таким образом, значение младшего разряда кода адреса очередной МК с выхода поля 1.4 блока памяти 1 микрокоманд полностью зависит

0 от значения сигнала на выходе блока сравнения 12.

Если код с выхода счетчика 11 ожидания не совпадает с кодом ожидания с выхода поля 1.2 блока памяти 1 микрокоманд, то

5 блок сравнения 12 формирует на своем выходе нулевой сигнал, который поступает на второй вход первого элемента ИЛИ 15.

Младший разряд адреса очередной МК с выхода 1.4 блока памяти микрокоманд мо0 дифицирован не будет, и по очередному тактовому импульсу с выхода первого элемента И 16 в регистр 2 адреса будет опять записан адрес МК типа В, т.е. повторится ожидание L-ro модуля для передачи ему АКУ, При этом

5 каждый раз при считывании МК типа В единичный сигнал с выхода первого разряда поля 1.1 блока памяти микрокоманд 1 разрешает запись в счетчик 11 и очередной тактовый импульс с выхода элемента И 17

0 своим задним фронтом увеличивает на единицу содержимое счетчика ожидания 11. Считывание МК типа В будет продолжаться до тех пор, пока либо L-й модуль не перейдет в режим ожидания АКУ, либо код с выхо5 да счетчика 11 не совпадет с кодом ожидания на выходе поля 1.2 блока памяти 1 микрокоманд.

В первом случае, если L-й модуль перешел в режим ожидания АКУ, то на выходе мультиплексора 7 логических условий будет

сформирован единичный сигнал, который разрешит прохождение единичного сигнала с выхода первого элемента ИЛИ 14 и преобразование АКУ, записанного в регистр 4 сдвига передачи, в последовательный код. АКУ в последовательном коде с выхода регистра 4 сдвига передачи поступает на информационный вход демультиплексора передачи 9, который его пропускает на выход, соответствующий коду, поступающему с выхода поля 1.3 блока памяти 1 микрокоманд, на адресный вход демультиплексора 9 передачи.

Также единичный сигнал с выхода мультиплексора 7 логических условий модифицирует младший разряд кода адреса с выхода поля 1.4 блока памяти микрокоманд

Iи по очередному тактовому импульсу с выхода первого элемента И 16 в регистр 2 адреса запишется адрес очередной МК. Счетчик ожидания 11 обнуляется сигналом с выхода младшего разряда регистра 2 адреса.

В случае если L-й модуль не перешел в режим ожидания АКУ, а количество тактов ожидания L-ro модуля для передачи ему АКУ вышло, т.е. код с выхода счетчика ожидания

IIсовпал с кодом, записанным в поле 1.2 блока памяти 1 микрокоманд N-ro модуля, то на выходе блока сравнения 12 формируется единичный сигнал, который модифицирует младший разряд кода адреса очередной МК.

По очередному тактовому импульсу с выхода элемента И 16 в регистр 2 адреса будет записан код адреса очередной МК.

Счетчик ожидания 11 устанавливается в нулевое состояние единичным сигналом с выхода младшего разряда регистра 2 адреса.

При считывании МК типа В на выходе третьего разряда поля 11 блока памяти 1 микрокоманд присутствует единичный сигнал, который поступает на инверсный управляющий вход регистра 3 микроопераций и запрещает запись в регистр 3 микроопераций кода ожидания из поля 1.2 блока памяти 1 микрокоманд.

При необходимости получения информации от другого устройства системы, т.е перехода в режим ожидания АКУ, в поле 1.1 формата последней МК (таблица , МК типа D) выполнявшейся МП записывается код (III), по которому дешифратор 10 формирует на своем седьмом выходе сигнал микрооперации ожидания АКУ.

Этот сигнал поступает на выход 26 состояния устройства и на соответствующие разряды входа 24 логических условий всех устройств системы. Кроме того, единичный сигнал с седьмого выхода дешифратора 10

признака поступает на управляющий вход мультиплексора 8 и разрешает осуществлять передачу на выход мультиплексора 8 АКУ в последовательном коде. Кодустройства, от которого ожидается АКУ, записан в поле 1.3 блока памяти 1 микрокоманд и поступает на адресный выход мультиплексора 8 ожидания.

Так же сигнал с седьмого выхода дешиф0 ратора 10 признака поступает на инверсный управляющий вход мультиплексора 7 логических условий и запрещает прохождение сигналов со входа 24 устройств и младшего разряда поля 1.4 блока памяти микроко5 манд по выходу мультиплексора 7 логических условий, т.е. на выходе мультиплексора 7 логических условий формируется нулевой сигнал, т,о,, в МКтипа D значение младшего разряда кода адреса очередной МК зависит

0 только от сигнала с выхода блока сравнения 12.

Единичный сигнал с выхода первого разряда поля 1.1 блока памяти 1 микрокоманд поступает на управляющие входы

5 счетчика ожидания 11 и блока сравнения 12 и разрешает запись в счетчик ожидания 11. Очередной тактовый импульс с выхода второго элемента И 17 своим задним фронтом увеличивает на единицу содержимое счет0 чика ожидания 11. Единичный сигнал с выхода третьего разряда поля 1.1 блока памяти микрокоманд запрещает запись в регистр 3 микроопераций кода ожидания, поступающего на информационный вход ре5 гистра 3 микроопераций с выхода поля 1.2 блока памяти 1 микрокоманд.

Количество тактов рабо.ты устройства, в течение которых оно ожидает АКУ,, определяет код ожидания, который записан в поле 1.2

0 МК типа 0, и поступает на второй информационный вход блока сравнения 12. На первый вход блока сравнения 12 поступает код с выхода счетчика 11 ожидания.

Если код с выхода счетчика 11 ожидания

5 не совпал с кодом с выхода поля 1.2 блока памяти 1 микрокоманд, то на выходе блока сравнения 12 присутствует нулевой сигнал, который не модифицирует младший разряд кода адреса с выхода поля 1.4 блока памяти

0 микрокоманд, который поступает на третий информационный вход мультиплексора адреса 6. В случае если к приходу очередного тактового импульса ri на вход синхронизации регистра 2 адреса на первом улрааляю5 щем входе мультиплексора 6 отсутствует единичный сигнал с выхода 5.1 регистра 5 (т.е. N-e устройство в данном такте работы не передало АКУ), то по заднему фронту п в регистр Г2 адреса опять запишется адрес

МК типа D, т.е. повторяется цикл ожидания АКУ от N-ro устройства. При этом каждый раз при считывании МК типа D единичный сигнал с выхода первого разряда поля 1.1 блока памяти 1 микрокоманд разрешает запись в счетчик ожидания 11. Очередной тактовый импульс Т2 своим задним фронтом увеличивает на единицу содержимое счетчика 11 ожидания.

Если код с выхода счетчика 11 ожидания совпал с кодом ожидания с выхода поля 1.2 блока памяти микрокоманд, то на выходе блока сравнения 12 формируется единичный сигнал, который модифицирует младший разряд кода адреса очередной МК с выхода поля 1.4 блока памяти микрокоманд, который поступает на третий информационный вход мультиплексора б. В случае если к приходу очередного синхроимпульса п на вход записи регистра адреса 2 на первом входе мультиплексора 6 адреса отсутствует единичный сигнал, то по заднему фронту синхроимпульса в регистр 2 адреса запишется адрес специальной микроподпрограммы (МПП).

Введение специальной МПП в программу функционирования устройств системы сделано с целью определения (при необходимости) причины отсутствия передачи АКУ N-м устройством данному (отказа N-ro устройства, N-e устройство выполняет участок программы, в котором не предусмотрена передача АКУ данному устройству, и т.п.). Если нет необходимости во введении специальной МПП, то в регистр 2 адреса запишется адрес очередной МК.

При считывании из регистра адреса специальной МПП или адреса очередной МК на вход установки в нулевое состояние счетчика 11 ожидания с выхода младшего разряда регистра 2 адреса будет поступать единичный сигнал, устанавливающий счетчик 11 ожидания в нулевое состояние.

В случае если N-e устройство осуществляет передачу АКУ данному устройству, то АКУ в последовательном коде поступает на вход 28 устройства, соответствующий N-му устройству, и через мультиплексор ожидания 8 поступает на информационный вход регистра 5, в котором по задним фронтам тактовых импульсов Гз, поступающих с выхода третьего элемента И 18 на вход синхронизации регистра 5, осуществляется поразрядная запись АКУ. Для исключения искажения последнего разряда АКУ разрядность регистра 5 на единицу больше разрядности АКУ. Старший и младший разряды АКУ всегда единичные. Появление единичного значения на выходе 5.1 регистра 5 свидетельствует о том, что АКУ полностью записан в регистр 5 и преобразован из последовательного кода в параллельный. Этот единичный сигнал с выхода 5.1 регистра 5 5 поступает на первый управляющий вход мультиплексора 6 адреса, который, согласно алгоритму функционирования пропускает на свой выход АКУ с первого информационного входа.

0По очередному тактовому импульсу TIB

регистр 2 адреса с выхода мультиплексора адреса 6 будет записан АКУ, по которому из блока памяти микрокоманд 1 считается нужная МК. В этом же такте работы по еди5 ничному сигналу с выхода младшего разряда регистров адреса устанавливается в нулевое состояние счетчик 11 ожидания. Формула изобретения Программируемое устройство управле0 ния, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий и триггер пуска, причем гр/ппа информационных входов кода операции является

5 первой группой информационных входов мультиплексора адреса, первый и второй разряды группы информационных входов кода операции мультиплексора адреса соединены соответственно с установочным и

0 сбросовым входами триггера пуска, третий разряд первой группы информационных вы ходов блока памяти микрокоманд соединен с инверсным входом разрешения регистра микроопераций, выходы которого являются

5 группой информационных выходов микроопераций устройства, вторая группа информационных выходов блока памяти микрокоманд соединена с информационными входами регистра микроопераций,

0 третья группа информационных выходов блока памяти микрокоманд соединена с адресными входами мультиплексора логических условий, четвертая группа информационных выходов блока памяти

5 микрокоманд соединена с второй группой информационных входов мультиплексора адреса, младший разряд четвертой группы информационных выходов блока памяти микрокоманд является младшим разрядом

0 группы информационных входов логических условий устройства, которые соединены с информационными входами мультиплексора логических условий, информационные выходы мультиплексора адреса соединены

5 с информационными входами регистра адреса, старшие разряды информационных выходов которого соединены с адресными входами блока памяти микрокоманд, отличающееся тем, что, с целью повышения надежности и расширения области применения устройства, в него дополнительно введены регистры сдвига передачи и сдвига ожидания, мультиплексор ожидания, де- мультиплексор передачи, дешифратор признака, счетчик ожидания, блок сравнения, первый и второй элементы ИЛИ, первый, второй, третий и четвертый элементы И, выход последнего соединен с первым входом разрешения регистра сдвига передачи, выход которого соединен с информационным входом демультиплексора передачи, выходы которого являются информационными выходами передачи устройства, первая группа информационных выходов блока памяти микрокоманд соединена с информаци- онными входами дешифратора признака, первый выход которого соединен с первым адресным входом мультиплексора адреса, первый разряд первой группы информационных выходов блока памяти микрокоманд соединен с информационными входами дешифратора признака, первый выход которого соединен с первым адресным входом мультиплексора адреса, первый разряд первой группы информационных выходов бло- ка памяти микрокоманд соединен с входами разрешения счетчика ожидания и блока сравнения, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с младшим разрядом второй группы информационных входов мультиплексора адреса, вторая группа информационных выхрдов блока памяти микрокоманд соединена с второй группой информационных входов блока сравнения и группой информационных входов регистра сдвига передачи, третья группа информационных выходов блока памяти микрокоманд соединена с адресными входами демультиплексора передачи и мультиплексора ожидания, выход которого соединен с информационным входом регистра сдвига ожидания, старшие разряды информационных выходов которого соединены с третьей группой информационных входов мультиплексора адреса, а младший разряд инфор- мационных выходов регистра сдвига ожидания соединен с вторым адресным входом мультиплексора адреса, первый, второй и третий входы синхронизации устройства соединены соответственно с первыми входами первого, второго и третьего элементов И, выход триггера пуска соединен с вторыми входами первого, второго и третьего элементов И, выход первого элемента И соединен с входом записи регистра адреса, младший разряд информационных выходов которого соединен с входом сброса счетчика ожидания, информационные выходы которого соединены с первой группой информационных входов блока сравнения, выход второго элемента И соединен с входом прямого счета счетчика ожидания, с входом записи регистра микроопераций и входом считывания регистра сдвига передачи, выход третьего элемента И соединен с входами записи регистра сдвига ожидания и регистра сдвига передачи, выход мультиплексора логических условий соединен с первым входом четвертого элемента И и вторым входом второго элемента ИЛИ, второй выход дешифратора признака соединен с входами разрешения мультиплексоров ожидания и логических условий и является управляющим выходом состояния устройства, третий выход дешифратора признака соединен с вторым входом разрешения регистра сдвига передача и первым входом первого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, четвертый выход дешифратора признака соединен с вторым входом первого элемента ИЛИ, информационные входы мультиплексора ожидания являются информационными входами ожидания устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП с программным управлением, допускающих наращивание при расширении числа выполняемых функций. Цель изобретения повышение надежности и расширение области применения устройства Поставленная цель достигается тем, что в известное устройство, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, триггер пуска, дополнительно введены регистры сдвига передачи и сдвига ожидания, мультиплексор ожидания, де- мультиплексор передачи, дешифратор признака, счетчик ожидания, блок сравнения, первый и второй элементы ИЛИ, первый - четвертый элементы И. Введение новых элементов позволяет на основе устройства обеспечить возможность построения наращиваемой гибкой распределенной управляющей системы, перестраиваемой при отказах, на основе конфигураций каждый с каждым. 4 ил , 1табл. (Л

Объект упрабшъ

А

С Начало j К

фиг.З

| Устройство программного управления | 1986 |

|

SU1334106A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-06-30—Публикация

1988-12-08—Подача