00

со со со

Изобретение относится к электросвязи и может использоваться в телемеханических системах, где требуется сжатие передаваемой и восстановление принимаемой информации.

Целью изобретения является повышение быстродействия устройства.

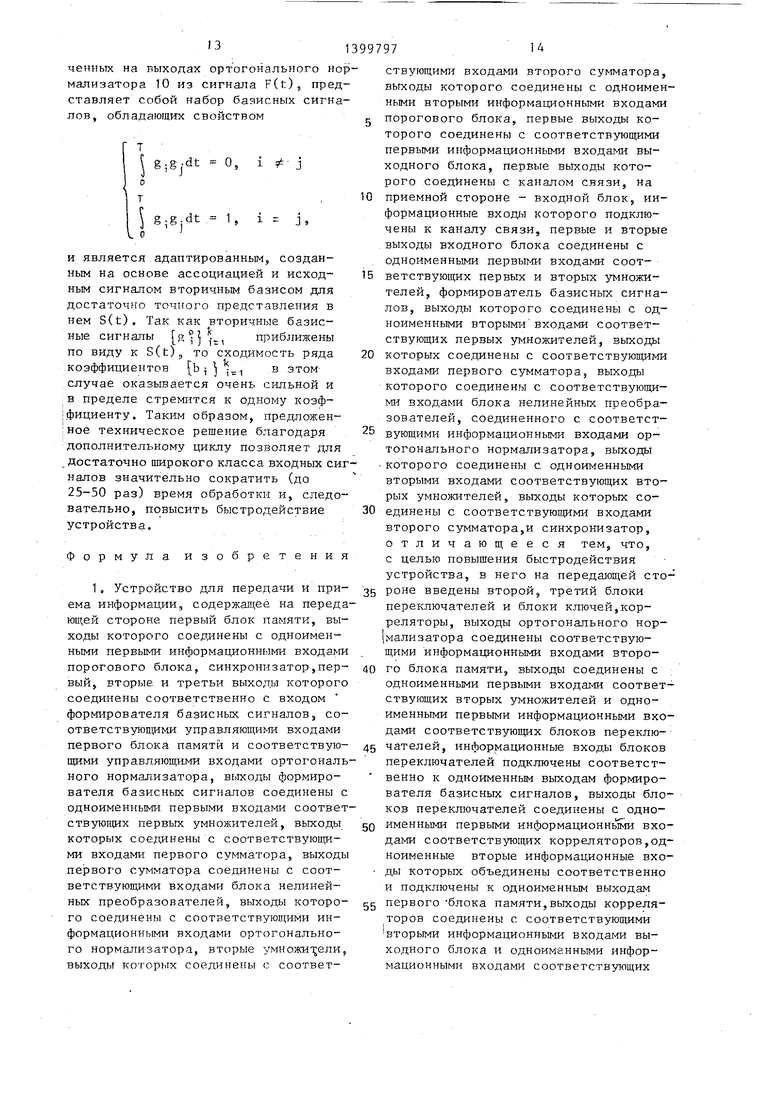

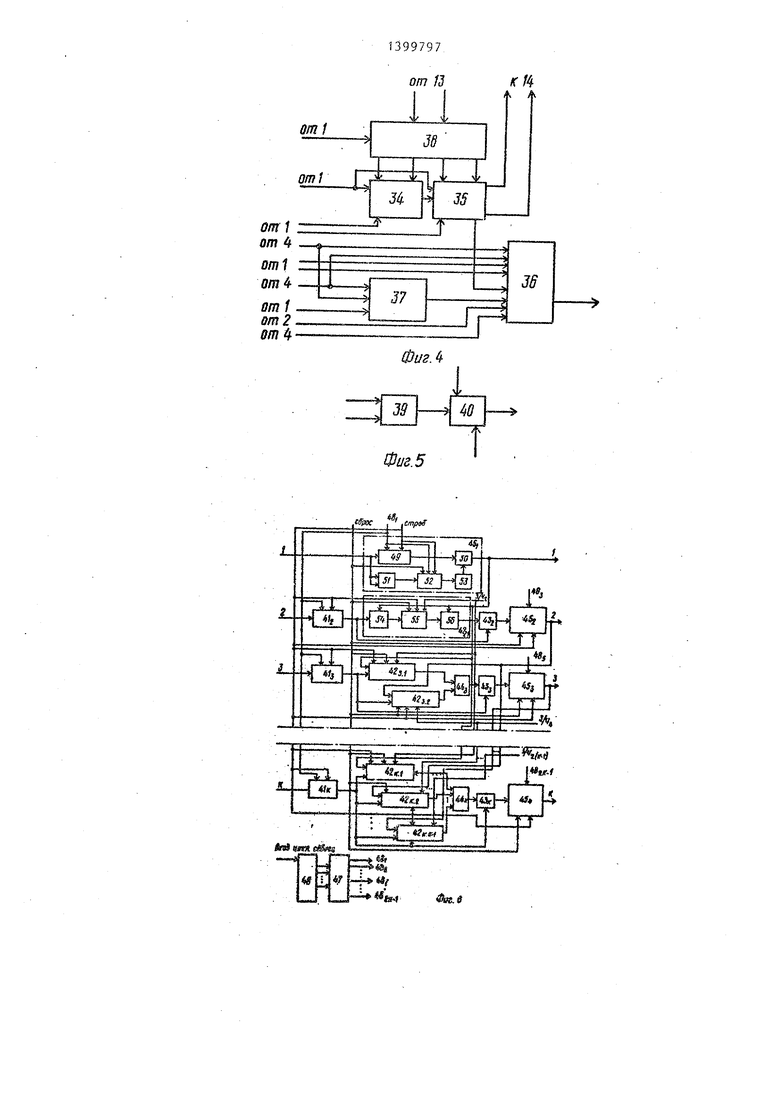

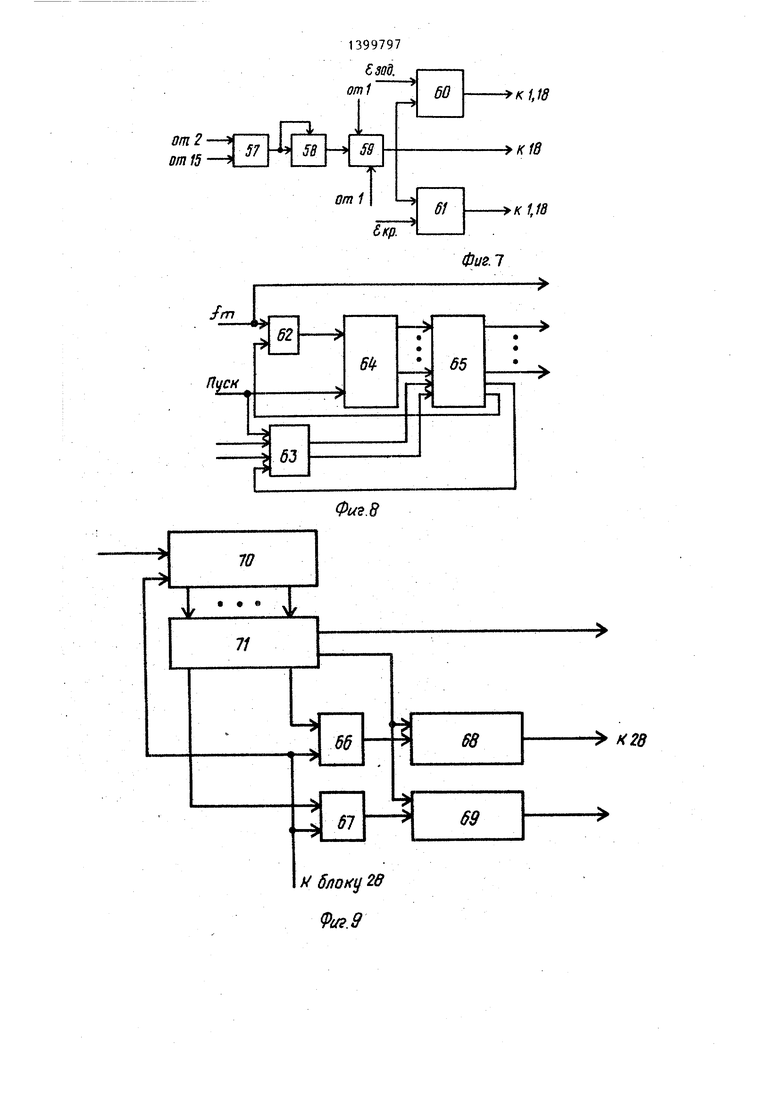

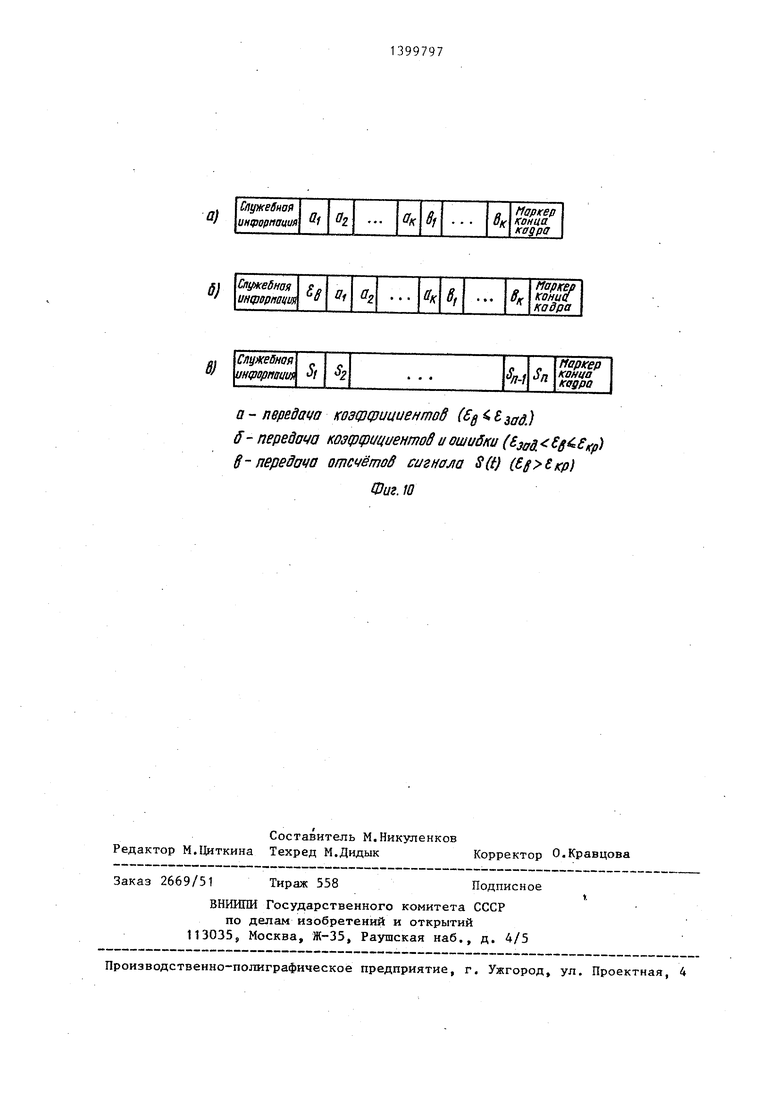

На фиг.1 представлена структурная схема передающей стороны устройства; на фиг.2 - структурная схема приемной стороны устройства; на фиг.З - функциональная схема входного блока; на фиг,4 - функциональная схема выходного блока;на фиг.З - функциональная схема коррелятора; на фиг.6 - функционапьная схема ортогонального нормализатора;на фиг.7 функциональная схема порогового блока на фиг.8 - функциональная схема синхронизатора; на фиг.9 -.функциональная схема дешифратора служебных посылок; на фиг.10 - форматы передаваемых информационных кадров.

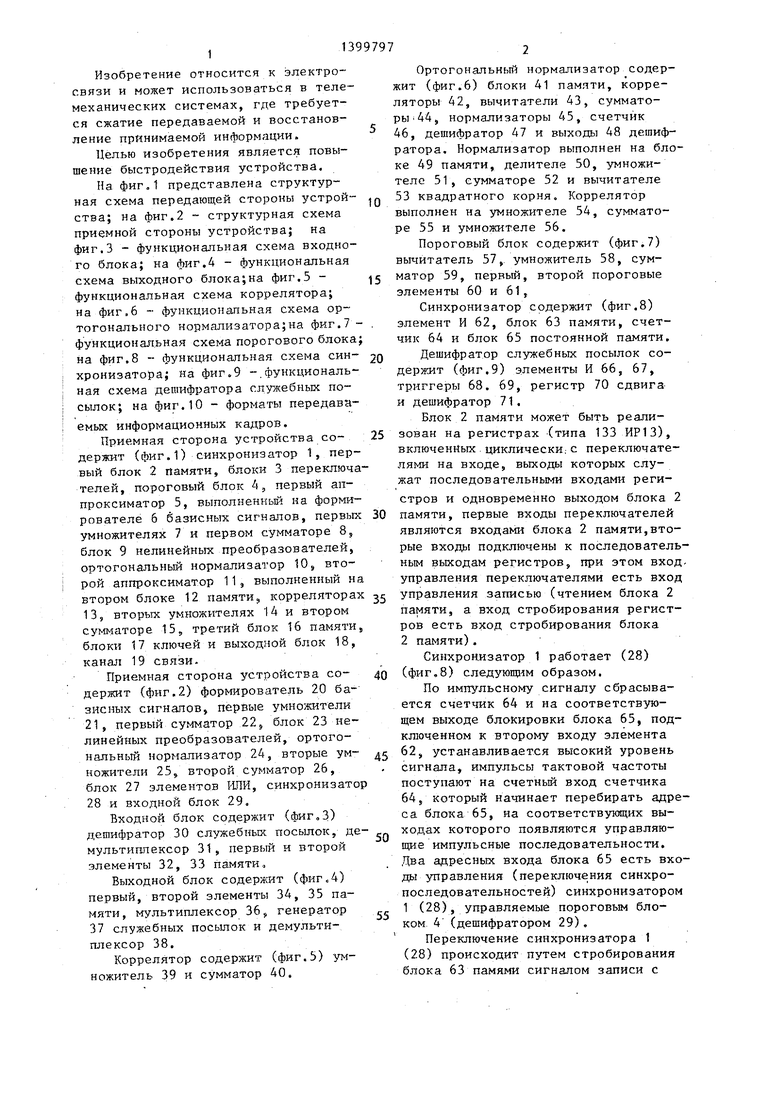

Приемная сторона устройства содержит (фиг.1) синхронизг1тор 1, первый блок 2 памяти, блоки 3 переключателей, пороговый блок АЗ первый ап- проксиматор 5, выполненный на формирователе 6 базисных сигналов, первых умножителях 7 и первом сумматоре 8, блок 9 нелинейных преобразователей, ортогональнью нормализатор 10, второй аппроксиматор 11, выполненный н втором блоке 12 памяти, коррелятора 13, вторъпс умножителях 14 и втором сумматоре 15, третий блок 16 памяти блоки 17 ключей и выходной блок 18, канал 19 связи.

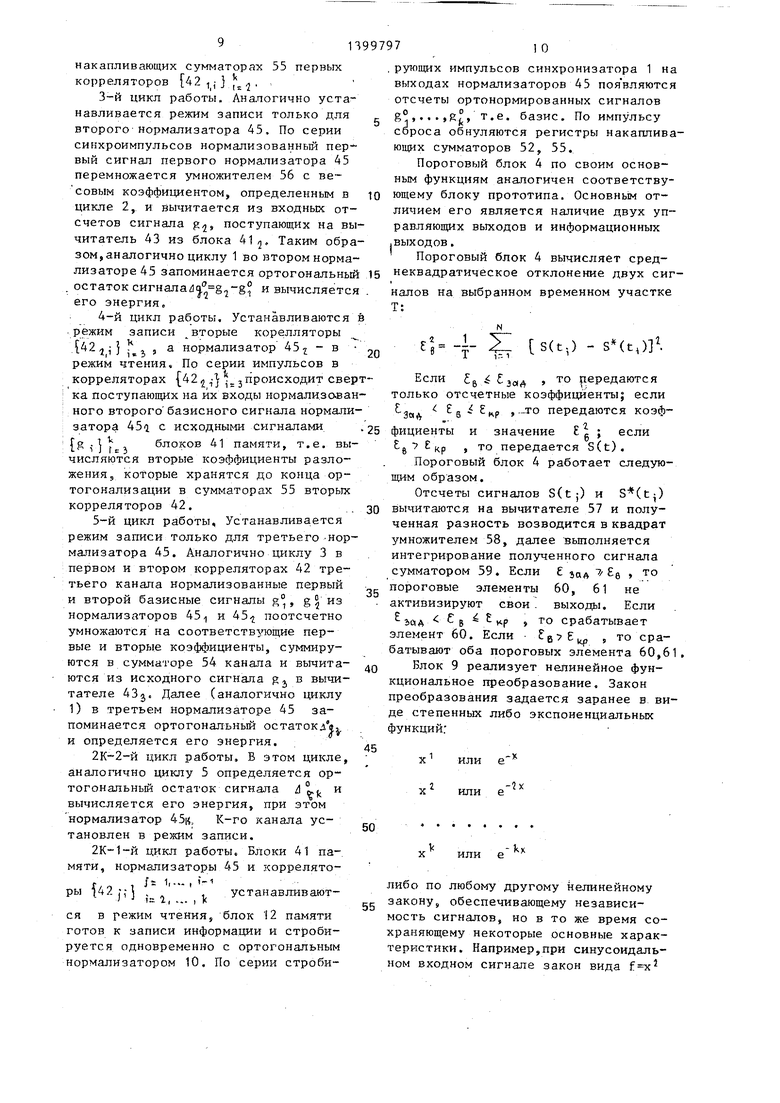

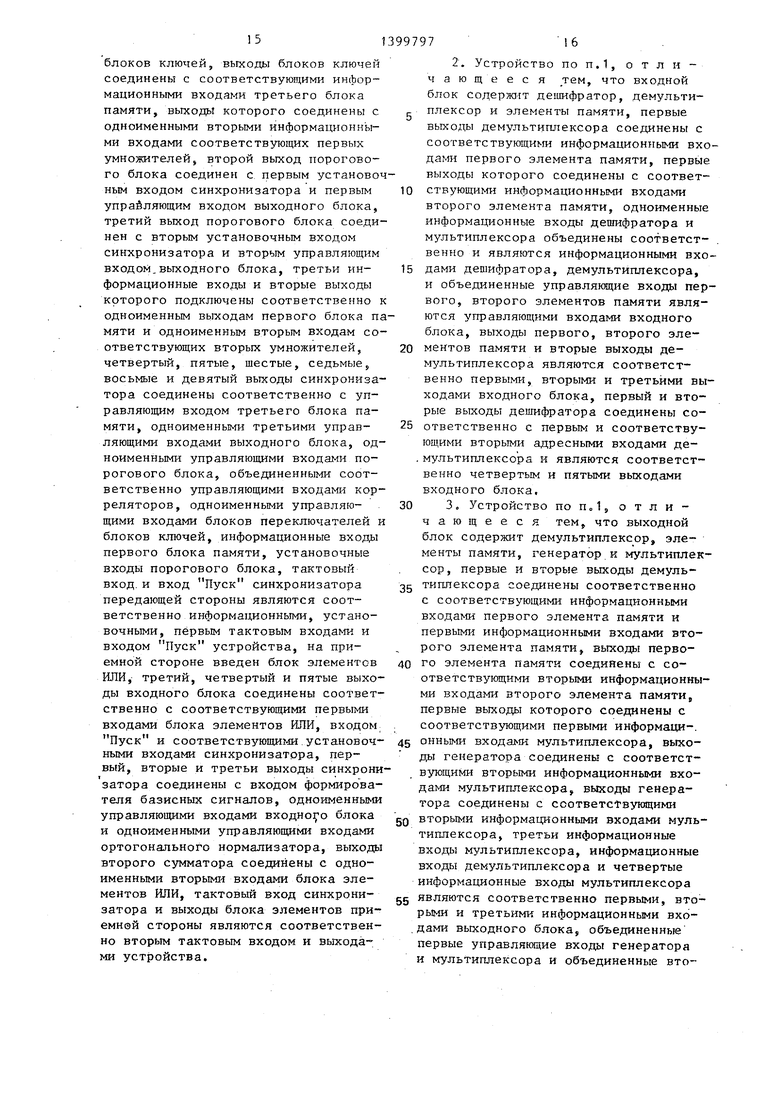

Приемная сторона устройства содержит {фиг.2) формирователь 20 базисных сигналов, первые умножители 21 , первый cy -rмaтop 225 блок 23 нелинейных Преобразователей, ортогональный нормализатор 24, вторые умножители 25, второй сумматор 26, блок 27 элементов 1 ШИ, синхронизато 28 и входной блок 29.

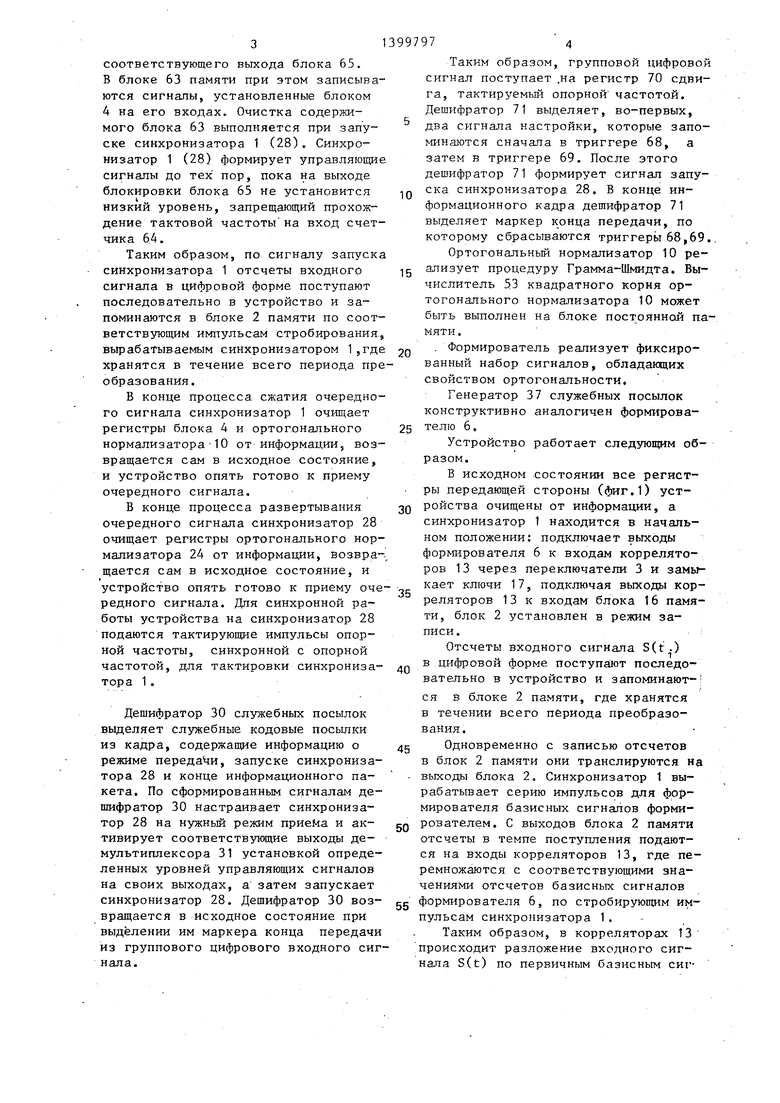

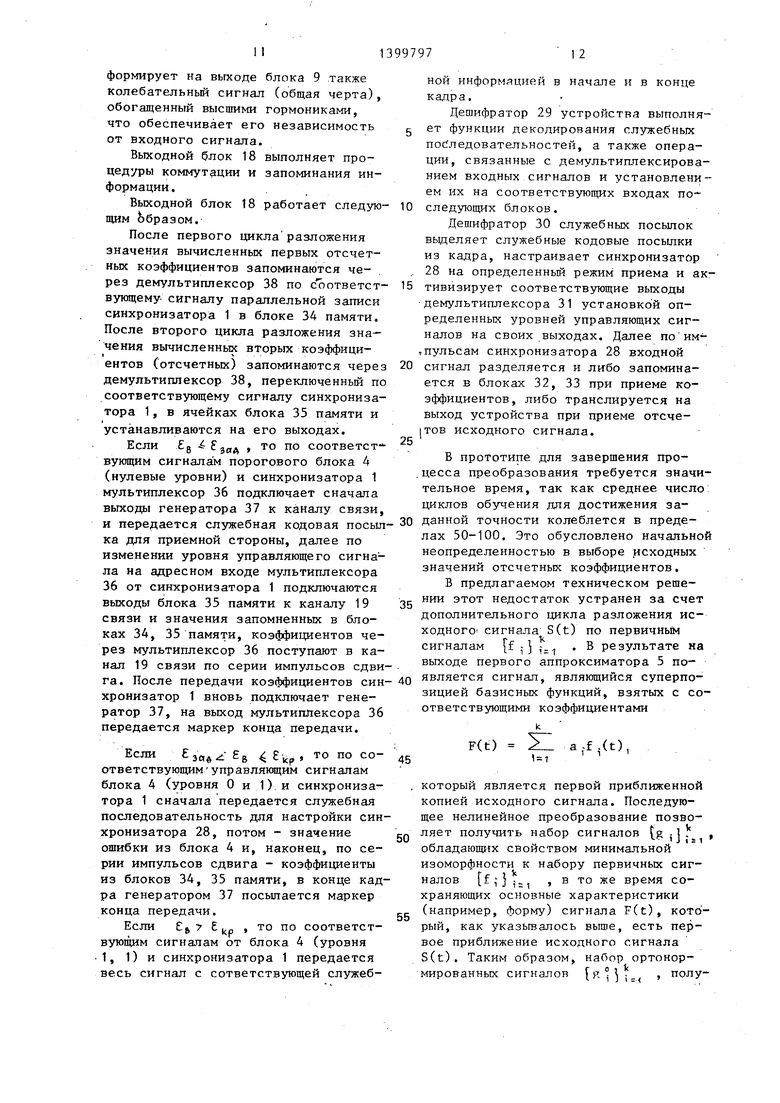

Входной блок содержит (фиг.З)

0

0

5

0

0

5

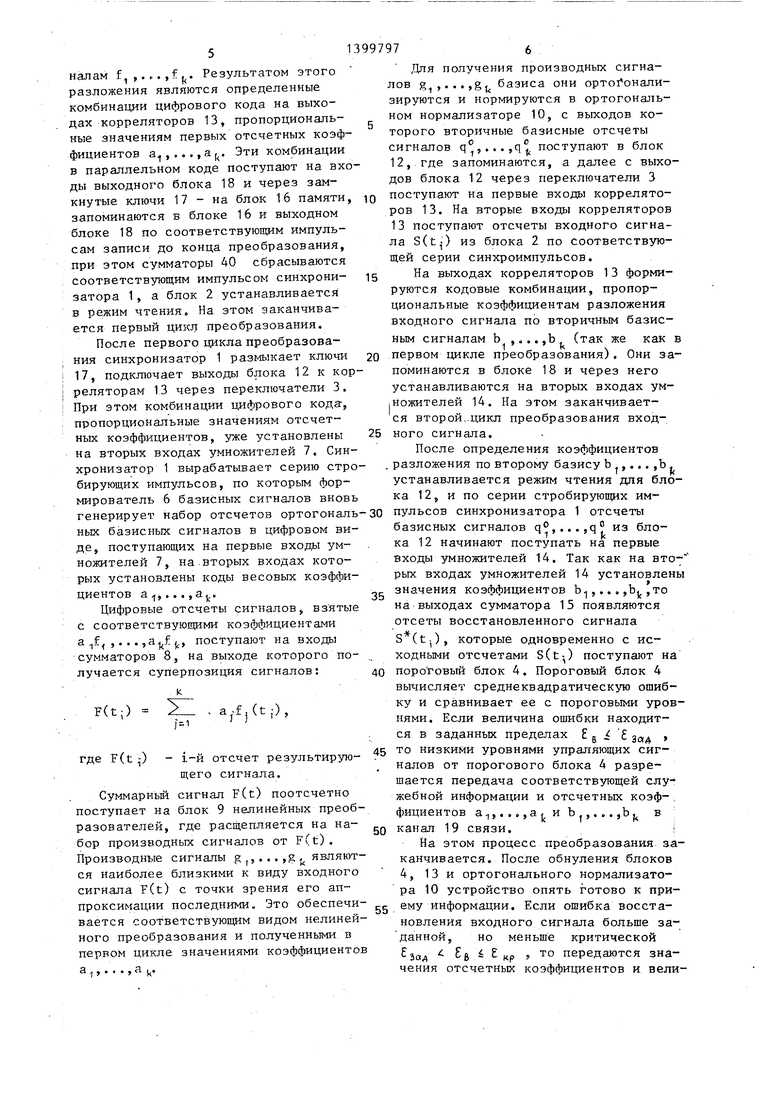

Ортогональный нормализатор содержит (фиг.6) блоки 41 памяти, корреляторы 42, вычитатели 43, сумматоры 44, нормализаторы 45, счетчик 46, дешифратор 47 и выходы 48 дешифратора. Нормализатор выполнен на блоке 49 памяти, делителе 50, умножителе 51, сумматоре 52 и вычитателе 53 квадратного корня. Коррелятор выполнен на умножителе 54, сумматоре 55 и умножителе 56.

Пороговый блок содержит (фиг.7) вычитатель 57,. умножитель 58, сумматор 59, первый, второй пороговые элементы 60 и 61,

Синхронизатор содержит (фиг.8) элемент И 62, блок 63 памяти, счетчик 64 и блок 65 постоянной памяти.

Дешифратор служебных посылок содержит (фиг,9) элементы И 66, 67, триггеры 68. 69, регистр 70 сдвига и Дешифратор 71.

Блок 2 памяти может быть реализован на регистрах (типа 133 ИР13), включенных циклически, с переключателями на входе, выходы которых служат последовательными входами регистров и одновременно выходом блока 2 памяти, первые входы переключателей являются входами блока 2 памяти,вторые входы подключены к последовательным выходам регистров, при этом вход, управления переключателями есть вход управления записью (чтением блока 2 памяти, а вход стробирования регистров есть вход стробирования блока 2 памяти).

Синхронизатор 1 работает (28) (фиг,8) следующим образом.

По импульсному сигналу сбрасывается счетчик 64 и на соответствующем выходе блокировки блока 65, подключенном к второму входу элемента 62, устанавливается высокий уровень сигнала, импульсы тактовой частоты поступают на счетньй вход счетчика 64, который начинает перебирать адреса блока 65, на соответствующих вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056244A1 |

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Устройство для ассоциативного сжатия информации | 1984 |

|

SU1170482A1 |

| Цифровой анализатор сигнала | 1988 |

|

SU1619297A1 |

| Устройство для вычисления азимутальной корреляционной функции | 1987 |

|

SU1509931A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Телеметрическая система со сжатием информации | 1989 |

|

SU1672502A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

Изобретение относится к электросвязи и может использоваться в телемеханических системах. Целью изобретения является повышение быстродействия устройства. Устройство осуществляет сжатие на передаияцей стороне передаваемой информации и восстанов ление на приемной стороне принима- .емой информации. Устройство содержит на передающей стороне синхронизатор 1, блоки 2, 12, 16 памяти, блоки переключателей, пороговый блок 4, формирователь 6 базисных сигналов, умножители , 14,-14,сумматоры 8, 15, блок 9 нелинейных преобразователей, ортогональный нормализатор 10, корреляторы , блоки l7 -17jj ключей и выходной блок 18, канал 19 связи,на приемной стороне - формирователь базисных сигналов, умножители, сумматоры, блок нелинейных преобразователей, ортогональный нормализатор, блок элементов ИЛИ, синхронизатор и входной блок. 4 з.п. ф-лы, 10 ип. (Л

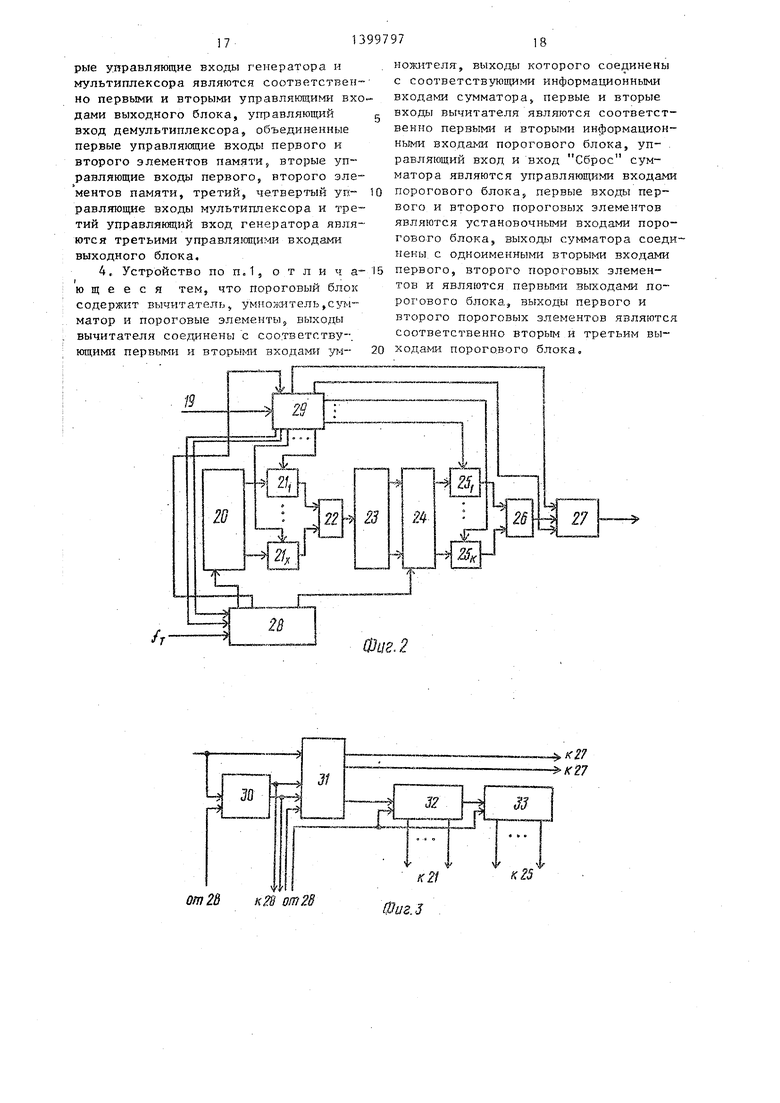

дешифратор 30 служебных посылок, де- ходах которого появляются управляюмультиплексор 31, первый и второй элементы 32, 33 памяти о

Выходной блок содержит (фиг.4) первый, второй элементы 34, 35 памяти, мультиплексор 36, генератор 37 служебных посылок и демульти- плексор 38,

Коррелятор содержит (фиг.5) умножитель 39 и сумматор 40,

55

щие импульсные последовательности, Два адресных входа блока 65 есть вх ды управления (переключения синхро- последовательностей) синхронизатором 1 (28), управляемые пороговым блоком 4 (дешифратором 29),

Переключение синхронизатора 1 (28) происходит путем стробирования блока 63 памями сигналом записи с

5

щие импульсные последовательности, Два адресных входа блока 65 есть входы управления (переключения синхро- последовательностей) синхронизатором 1 (28), управляемые пороговым блоком 4 (дешифратором 29),

Переключение синхронизатора 1 (28) происходит путем стробирования блока 63 памями сигналом записи с

3

соответствующего выхода блока 65. В блоке 63 памяти при этом записываются сигналы, установленные блоком 4 на его входах. Очистка содержимого блока 63 выполняется при запуске синхронизатора 1 (28). Синхронизатор 1 (28) формирует управляющие сигналы до тех пор, пока на выходе блокировки блока 65 не установится низкий уровень, запрещающий прохождение тактовой частоты на вход счетчика 64.

Таким образом, по сигналу запуска синхронизатора 1 отсчеты входного сигнала в цифровой форме поступают последовательно в устройство и запоминаются в блоке 2 памяти по соответствующим импульсам стробирования, вьфабатываемым синхронизатором 15где хранятся в течение всего периода преобразования.

В конце процесса сжатия очередного сигнала синхронизатор 1 очищает регистры блока 4 и ортогонального нормализатора 10 от информации, возвращается сам в исходное состояние, и устройство опять готово к приему очередного сигнала,

В конце процесса развертывания очередного сигнала синхронизатор 28 очищает регистры ортогонального нормализатора 24 от информации, возвращается сам в исходное состояние, и устройство опять готово к приему очередного сигнала. Для синхронной работы устройства на синхронизатор 28 подаются тактируюш;ие импульсы опорной частоты, синхронной с опорной частотой, для тактировки синхронизатора 1 .

Дешифратор 30 служебных посылок вьщеляет служебные кодовые посылки из кадра, содержащие информацию о режиме передали, запуске синхронизатора 28 и конце информационного пакета. По сформированным сигналам дешифратор 30 настраивает синхронизатор 28 на нужньш режим приема и активирует соответствующие выходы де- мультиплексора 31 установкой определенных уровней управляющих сигналов на своих выходах, а затем запускает синхронизатор 28. Дешифратор 30 возвращается в исходное состояние при выделении им маркера конца передачи из группового цифрового входного сигнала.

997974

Таким образом, групповой цифровой сигнал поступает .на регистр 70 сдвига, тактируемый опорной частотой. Дешифратор 71 выделяет, во-первых, два сигнала настройки, которые запоминаются сначала в триггере 68, а затем в триггере 69. После этого дешифратор 71 формирует сигнал запу- Q ска синхронизатора 28. В конце информационного кадра дещифратор 71 выделяет маркер конца передачи, по которому сбрасываются триггеры 68,69..

Ортогональньй нормализатор 10 ре- g ализует процедуру Грамма-Шмидта. Вычислитель 53 квадратного корня ортогонального нормализатора 10 может быть выполнен на блоке пост ояннай памяти.

. Формирователь реализует фиксированный набор сигналов, обладающих свойством ортогональности.

Генератор 37 служебных посылок конструктивно аналогичен формирова- 25 телю 6,

Устройство работает следующим образом.

В исходном состоянии все регистры передающей стороны (фиг.1) уст- 30 ройства очищены от информации, а синхронизатор 1 находится в начальном положении: подключает выходы формирователя 6 к входам корреляторов 13 через переключатели 3 и замыкает ключи 17, подключая выходы корреляторов 13 к входам блока 16 памяти, блок 2 установлен в режим записи .;

20

35

Отсчеты входного сигнала S(t.) в цифровой форме поступают последовательно в устройство и запоминают-: ся в блоке 2 памяти, где хранятся в течении всего периода преобразования .

Одновременно с записью отсчетов

в блок 2 памяти они транслируются на выходы блока 2, Синхронизатор 1 вырабатывает серию импульсов для формирователя базисных сигналов формирователем. С выходов блока 2 памяти отсчеты в темпе поступления подаются на входы корреляторов 13, где перемножаются с соответствующими значениями отсчетов базисных сигналов

формирователя 6, по стробирующим импульсам синхронизатора 1.

Таким образом, в корреляторах 13 происходит разложение входного сигнала S(t) по первичным базисным сигналам f, ,..,.,f. Результатом этого разложения являются определенные комбинации цифрового кода на выходах корреляторов 13, пропорциональные значениям первых отсчетных коэффициентов а,

а(.

Эти комбинации

Для получения производных сигналов g,...,gj базиса они ортот онали- зируются и нормируются в ортогональном нормализаторе 10, с выходов которого вторичные базисные отсчеты сигналов

Ч%

в параллельном коде поступают на входы выходного блока 18 и через замкнутые ключи 17 - на блок 16 памяти, запоминаются в блоке 16 и выходном блоке 18 по соответствующим импульсам записи до конца преобразования, при этом сумматоры АО сбрасываются соответствующим импульсом синхронизатора 1, а блок 2 устанавливается в режим чтения. На этом заканчивается первый цикл преобразования.

После первого цикла преобразования синхронизатор 1 размыкает ключи 17, подключает выходы блока 12 к корреляторам 1.3 через переключатели 3. При этом комбинации цифрового кода, пропорциональные значениям отсчетных коэффициентов, уже установлены на вторых входах умножителей 7. Син,q поступают в блок

12, где запоминаются, а далее с выходов блока 12 через переключатели 3

Q поступают на первые входы корреляторов 13. На вторые входы корреляторов 13 поступают отсчеты входного сигнала S(t,-) из блока 2 по соответствующей серии синхроимпульсов.

15 На выходах корреляторов 13 формируются кодовые комбинации, пропорциональные коэффициентам разложения входного сигнала по вторичным базисным сигналам b ,...,b (так же как в

20 первом цикле преобразования). Они запоминаются в блоке 18 и через него устанавливаются на вторых входах ум- |Ножителей 14. На этом заканчивается второй,.цикл преобразования вход25 ного сигнала.

После определения коэффициентов

хронизатор 1 вырабатывает серию стро- . разложения по второму базису Ъ...,Ь,

бирующих импульсов, по которым формирователь 6 базисных сигналов вновь генерирует набор отсчетов ортогонапь-30 ных базисных сигналов в цифровом виде, поступающих на первые входд умножителей 7, на.вторых входах которых установлены коды весовых коэффиустанавливается режим чтения для блока 12, и по серии стробирующих импульсов синхронизатора 1 отсчеты базисных сигналов q°,...,q° из блока 12 начинают поступать на первые входы умножителей 14. Так как на вто рых входах умножителей 14 установлен

циентов а ,

ЧЦифровые отсчеты сигналов, вз ятые с соответствующими коэффициентами а f, ,. .. , , поступают на входы сумматоров 8, на выходе которого получается суперпозиция сигналов:

к F(t;) XI. - a,.f, (t j) ,

fzLl

где F(t -) - i-й отсчет результирующего сигнала,

Суммарньй сигнал F(t) поотсчетно поступает на блок 9 нелинейных преобразователей, где расщепляется на набор производных сигналов от F(t). Производные сигналы g ,,. .. ,g - являются наиболее близкими к виду входного сигнала F(t) с точки зрения его аппроксимации последними. Это обеспечивается соответствующим видом нелинейного преобразования и полученными в первом цикле значениями коэффициентов а .,,.-, а ((

Для получения производных сигналов g,...,gj базиса они ортот онали- зируются и нормируются в ортогональном нормализаторе 10, с выходов которого вторичные базисные отсчеты сигналов

Ч%

,q поступают в блок

12, где запоминаются, а далее с выходов блока 12 через переключатели 3

поступают на первые входы корреляторов 13. На вторые входы корреляторов 13 поступают отсчеты входного сигнала S(t,-) из блока 2 по соответствующей серии синхроимпульсов.

На выходах корреляторов 13 формируются кодовые комбинации, пропорциональные коэффициентам разложения входного сигнала по вторичным базисным сигналам b ,...,b (так же как в

первом цикле преобразования). Они запоминаются в блоке 18 и через него устанавливаются на вторых входах ум- |Ножителей 14. На этом заканчивается второй,.цикл преобразования входного сигнала.

После определения коэффициентов

разложения по второму базису Ъ...,Ь,

устанавливается режим чтения для блока 12, и по серии стробирующих импульсов синхронизатора 1 отсчеты базисных сигналов q°,...,q° из блока 12 начинают поступать на первые входы умножителей 14. Так как на вто- рых входах умножителей 14 установлены

значения коэффициентов b,...,b. ,то на выходах сумматора 15 появляются отсеты восстановленного сигнала S (t;), которые одновременно с исходными отсчетами S(t-,) поступают на

пороговый блок 4. Пороговый блок 4 вычисляет среднеKBадратическую ошибку и сравнивает ее с пороговыми уровнями. Если величина ошибки находится в заданных пределах зад

то низкими уровнями упрапнющих сигналов от порогового блока 4 разрешается передача соответствующей служебной информации и отсчетных коэффициентов а

0

1 « I;

И b ...,Ь,

5

канал 19 связи.

На этом процесс преобразования заканчивается. После обнуления блоков 4, 13 и ортогонального нормализатора 10 устройство опять готово к приему информации. Если ошибка восстановления входного сигнала больше заданной, но меньше критической Зад б кр г° передаются значения отсчетных коэффициентов к вели7

чина ошибки. Если ошибка восстановления исходного сигнала превышает критическую величину, то входной сигнал передается полностью в какал 19 связи.

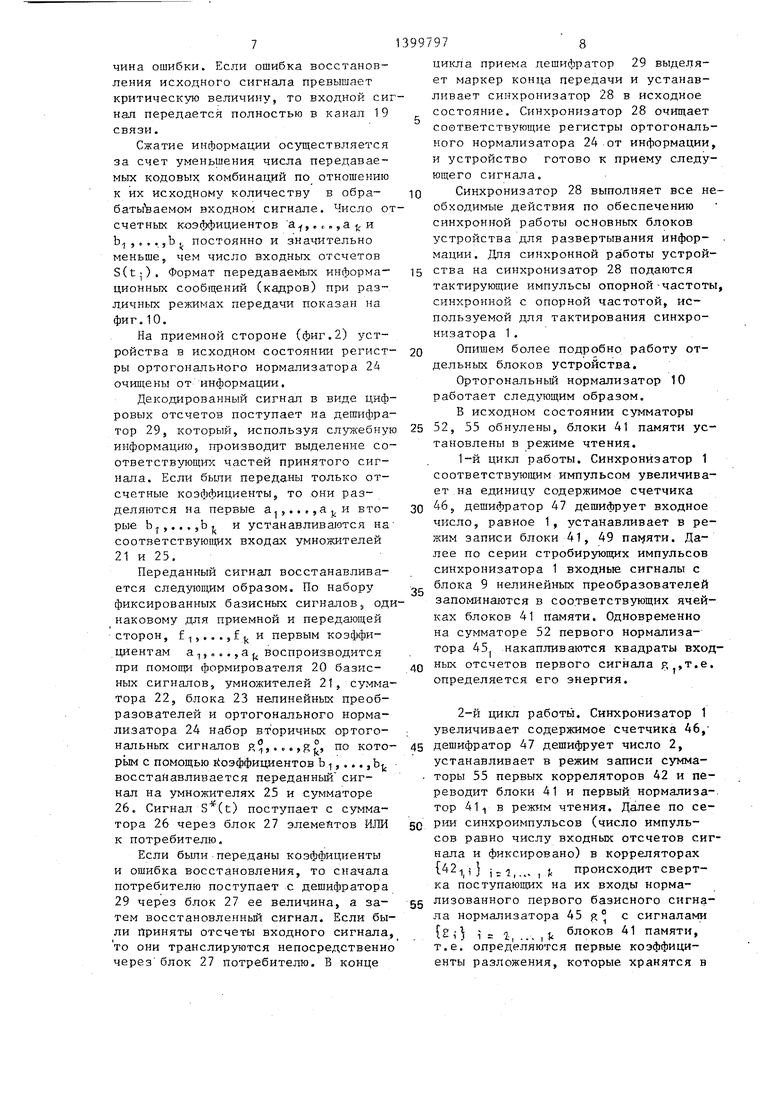

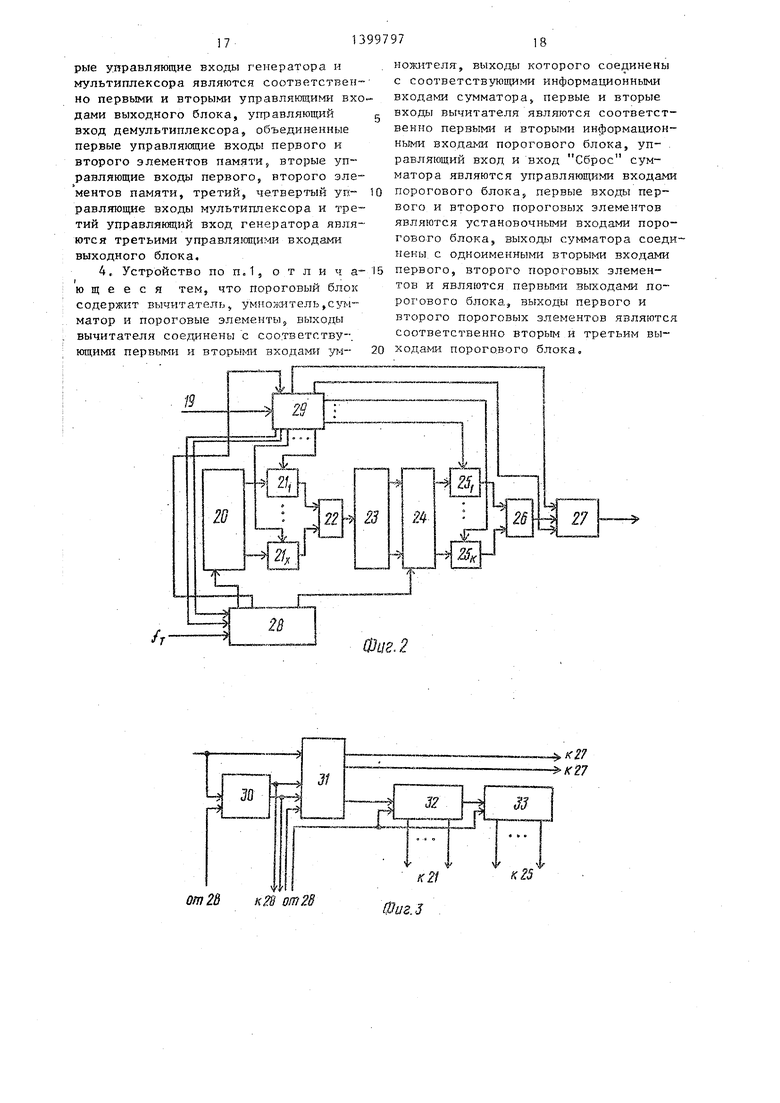

Сжатие информации осуществляется за счет уменьшения числа передаваемых кодовых комбинаций по отношению к их исходному количеству в обрабатываемом входном сигнале. Число от счетных коэффициентов а,.„., b,,,.5b, постоянно и значительно меньшеJ чем число входных отсчетов S(t ). Формат передаваемых информационных сообщений (кадров) при различных режимах передачи показан на фиг.10.

На приемной стороне (фиг.2) устройства в исходном состоянии регистры ортогонального нормализатора 24 очия1;ены от информации.

Декодированный сигнал в виде цифровых отсчетов поступает на дешифратор 29, который, используя служебную информацию, производит выделение соответствующих частей принятого сигнала. Если были переданы только от- счетные коэффициенты, то .они разделяются на первые a.,..,, вторые b,,..,b, и устанавливаются на соответствующих входах умножителей 21 и 25,

Переданный сигнал восстанавливается следутащим образом. По набору фиксированных базисных сигналов,, одинаковому для приемной и передающей сторон, f,...,f и первым коэффициентам а,,, .. ,а воспроизводится при помощи формирователя 20 базисных сигналов, умножителей 21, сумматора 22, блока 23 нелинейных преобразователей и ортогонального нормализатора 24 набор вторичных ортогональных сигналов R,.o.,gf, по кото- рь1м с помощью Коэффициентов Ь/,, ... ,bi. восстанавливается переданный сигнал на умножителях 25 и cy шaтope 26. Сигнал S (t) поступает с сумматора 26 через блок 27 элемейтов ИЛИ к потребителю.

Если бьши переданы коэффициенты и ошибка восстановления, то сначала потребителю поступает с дешифратора 29 через блок 27 ее величина, а затем восстановленньй сигнал. Если были Приняты отсчеты входного сигнала, то они транслируются непосредственно через блок 27 потребителю. В конце

997978

цикла приема дешифратор 29 выделяет маркер конца передачи и устанавливает синхронизатор 28 в исходное состояние. Синхронизатор 28 очищает соответствующие регистры ортогонального нормализатора 24 от информации, и устройство готово к приему следующего сигнала,

10 Синхронизатор 28 выполняет все необходимые действия по обеспечению синхронной работы основньпс блоков устройства для развертывания информации. Для синхронной работы устрой15 ства на синхронизатор 28 подаются

тактирующие импульсы опорной-частоты, синхронной с опорной частотой, используемой для тактирования синхронизатора 1 .

20 Опишем более подробно работу отдельных блоков устройства.

Ортогональньм нормализатор 10 работает следующим образом,

В исходном состоянии сумматоры

25 52, 55 обнулены, блоки 41 памяти установлены в режиме чтения.

1-й цикл работы. Синхронизатор 1 соответствующим импульсом увеличивает на единицу содержимое счетчика

30 , дешифратор 47 дешифрует входное число, равное 1, устанавливает в режим записи блоки 41, 49 . Далее по серии стробирующих импульсов синхронизатора 1 входные сигналы с блока 9 нелинейных преобразователей запоминаются в соответствующих ячейках блоков 41 памяти. Одновременно на сумматоре 52 первого нормализатора 45 накапливаются квадраты вход4Q ных отсчетов первого сигнала g .т.е. определяется его энергия.

2-й цикл работы. Синхронизатор 1 увеличивает содержимое счетчика 46, 45 дешифратор 47 дешифрует число 2,

устанавливает в режим записи сумма- . торы 55 первых корреляторов 42 и переводит блоки 41 и первый нормапиза-. тор 41 в режим чтения. Далее по се- 0 рии синхроимпульсов (число импульсов равно числу входных отсчетов сигнала и фиксировано) в корреляторах ,-} j:;,... , г, происходит сверт- ка поступаюш 1х на их входы норма- gg лизованного первого базисного сигнала нормализатора 45 g° с сигналами CSi} jt блоков 41 памяти, т.е. определяются первые коэффициенты разложения, которые хранятся в

35

накапливающих сумматорах 55 первых корреляторов . . .

3-й цикл работы, Анапогично устанавливается режим записи только для второго-нормализатора 45. По серии синхроимпульсов нормализованный первый сигнал первого нормализатора 45 перемножается умножителем 56 с ве- совым коэффициентом, определенным в цикле 2, и вычитается из входных отсчетов сигнала поступающих на вы- читатель 43 из блока 415. Таким образом, аналогично циклу 1 во втором норма10

рующих импульсов синхронизатора 1 на выходах нормализаторов 45 появляются отсчеты ортонормированных сигналов g° ,...,й, т.е. базис. По импульсу сброса обнуляются регистры накапливающих сумматоров 52, 55.

Пороговый блок 4 по своим основным функциям аналогичен соответствующему блоку прототипа. Основным отличием его является наличие двух управляющих выходов и информационных .выходов. Пороговый блок 4 вычисляет средлизаторе 45 запоминается ортогональный 15 неквадратическое отклонение двух сигналов на выбранном временном участке

Т:

20

. остаток ciirnanauff e g и вычисляется . его энергия.

4-й цикл работы. Устанавливаются в режим записи вторые корелляторы jlj 9 нормализатор 45 - в режим чтения. По серии импульсов в корреляторах { 2 проискор,ит сверт- ка поступающих на их входы нормализованного второго базисного сигнала нормали45 с исходными сигналами. .25 блоков 41 памяти, т.е. вызатора

7 т f 1 .XУ 1 lldl А i J

числяются вторые коэффициенты разло1

т

N

s(t.,) - s(t,)l

1

Если i. i

ЗОА

то передаются

только отсчетные коэффициенты; если

Зад

фициенты Е

g цр ,-ТО передаются коэфи значение g ; , то передается S(t).

если

кр

Пороговый блок 4 работает следующим образом.

тогонализации в сумматорах 55 вторых корреляторов 42.

5-й цикл работы. Устанавливается режим записи только для третьего -нормализатора 45. Аналогично циклу 3 в первом и втором корреляторах 42 третьего канахга нормализованные первый и второй базисные сигналы g°, g § из нормализаторов 45 и 45 поотсчетно умножаются на соответствующие первые и вторые коэффициенты, суммируются в сумматоре 54 канала и вычитаются из исходного сигнала gj в вычи- тателе 43j. Далее (аналогично циклу 1) в третьем нормализаторе 45 запоминается ортогональньш остатокд аг и определяется его энергия.

2К-2-Й цикл работы. В этом цикле аналогично циклу 5 определяется ортогональньш остаток сигнала Л i. и вычисляется его энергия, при этом нормализатор 45й. К-го канала установлен в режим записи.

2К-1-Й цикл работы. Блоки 41 па-, мяти, нормализаторы 45 и коррелято/i 1,... , r-i

, устанавливают- 7., ... I к

ся в режим чтения, блок 12 памяти готов к записи информации и строби- руется одновременно с ортогональным нормализатором 10. По серии стробиры i42j,-} I

рующих импульсов синхронизатора 1 на выходах нормализаторов 45 появляются отсчеты ортонормированных сигналов g° ,...,й, т.е. базис. По импульсу сброса обнуляются регистры накапливающих сумматоров 52, 55.

Пороговый блок 4 по своим основным функциям аналогичен соответствующему блоку прототипа. Основным отличием его является наличие двух управляющих выходов и информационных .выходов. Пороговый блок 4 вычисляет сред

1

т

N

s(t.,) - s(t,)l

1

Если i. i

ЗОА

то передаются

только отсчетные коэффициенты; если

Зад

фициенты Е

g цр ,-ТО передаются коэфи значение g ; , то передается S(t).

если

кр

Пороговый блок 4 работает следующим образом.

Отсчеты сигналов S(t;) и S(t) вычитаются на вычитателе 57 и полученная разность возводится в квадрат умножителем 58, далее вьтолняется интегрирование полученного сигнала сумматором 59. Если зад 7/ЕВ , то

не Если

пороговые элементы 60, 61 активизируют свои . выходы.

0

зад

R Е

элемент 60.

кр Если

то срабатывает

-в fck S то срабатывают оба пороговых элемента 60,61.

Блок 9 реализует нелинейное функциональное преобразование. Закон преобразования задается заранее в виде степенных либо экспоненциальных

функций:

или

или

-5х

или

-Ях

либо по любому другому нелинейному закону, обеспечивающему независимость сигналов, но в то же время сохраняющему некоторые основные характеристики. Например,при синусоидальном входном сигнале закон вида

формирует на выходе блока 9 также колебательньй сигнал (общая черта), обогащенный высшими гормониками, что обеспечивает его независимость от входного сигнала.

Выходной блок 18 выполняет процедуры коммутации и запоминания информации ,

Выходной блок 18 работает следующим Ьбразом.

После первого цикла разложения значения вычисленных первых отсчет- ных коэффициентов запоминаются через демультиплексор 38 по сЪответст- вующему сигналу параллельной записи синхронизатора 1 в блоке 34 памяти. После второго цикла разложения зна- чения вычисленных вторых коэффициентов (отсчетных) запоминаются через демультиппексор 38, переключенньй по соответствующему сигналу синхронизатора 1, в ячейках блока 35 памяти и устанавливаются на его выходах.

Если g - п° соответст вующим сигналам порогового блока 4 (нулевые уровни) и синхронизатора 1 мультиплексор 36 подключает сначала выходы генератора 37 к каналу связи, и передается служебная кодовая посыпка для приемной стороны, далее по изменении уровня управляющего сигнала на адресном входе мультиплексора 36 от синхронизатора 1 подключаются выходы блока 35 памяти к каналу 19 связи и значения запомненных в блоках ЗА, 35 памяти, коэффициентов через мультиплексор 36 поступают в канал 19 связи по серии импульсов сдвига. После передачи коэффициентов синхронизатор 1 вновь подключает генератор 37, на выход мультиплексора 36 передается маркер конца передачи.

Если в 4 kp п° ° ответствующим управлякщим сигналам

блока 4 (уровня О и 1) и синхронизатора 1 сначала передается служебная последовательность для настройки синхронизатора 28, потом - значение ошибки из блока 4 и, наконец, по серии импульсов сдвига - коэффициенты из блоков 34, 35 памяти, в конце кадра генератором 37 посыпается маркер конца передачи.

Если j7 Ej,p , то по соответствующим сигналам от блока 4 (уровня 1, 1) и синхронизатора 1 передается весь сигнал с сответствующей служеб

ной информацией в начале и в конце кадра.

Дешифратор 29 устройства выполня- 5 ет функции декодирования служебных пос ледовательностей, а также операции, связанные с демультиплексированием входных сигналов и установлением их на соответствующих входах по 10 следующих блоков.

Дешифратор 30 служебных посыпок выделяет служебные кодовые посьшки из кадра, настраивает синхронизатор ,. 28 на определенный режим приема и ак- 15 тивизирует соответствующие выходы -демультиплексора 31 установкой определенных уровней управляющих сигналов на своих выходах. Далее по им- ,пульсам синхронизатора 28 входной 20 сигнал разделяется и либо запоминается в блоках 32, 33 при приеме коэффициентов, либо транслируется на выход устройства при приеме отсче- Iтов исходного сигнала.

25

6

В прототипе для завершения про- .цесса преобразования требуется значительное время, так как среднее число: циклов обучения для достижения за0 данной точности колеблется в пределах 50-100. Это обусловлено начальной неопределенностью в выборе исходных значений отсчетных коэффициентов,

В предлагаемом техническом решении этот недостаток устранен за счет дополнительного цикла разложения ис- ходного сигнала S(t) по первичньм сигналам f-} f. .В результате на выходе первого аппроксиматора 5 по-

0 является сигнал, являющийся суперпозицией базисных функций, взятых с соответствующими коэффициентами

k

F(t) ZI a-f (t),

, который является первой приближенной копией исходного сигнала. Последующее нелинейное преобразование позво- ,, ляет получить набор сигналов (g -, обладающих свойством минимальной изоморфности к набору первичных сигналов f, , в то же время сохраняющих основные характеристики (например, форму) сигнала F(t), который, как указывалось выше, есть первое приближение исходного сигнала S(t). Таким образом, набор ортонор- мированных сигналов ,° ; . полу5

на выходах ортогонального нормализатора 10 из сигнала FCt), представляет собой набор базисных сигналов, обладающих свойством

Т

;,gj.dt 0, i t- j

о Т

g-gjdt 1, i - j,

и является.адаптированным, созданным на основе ассоциацией и исход- ньм сигналом вторичным базисом для достаточно точного представления в нем S(t), Так как вторичные базисные сигналы й,-, приближены по виду к SCt), то сходимость ряда коэффициентов {Ь ; в этом- случае оказывается очень сильной и в пределе стремится к одному коэф- ;фнциенту. Таким образом, предложен- ;ное техническое решение благодаря дополнительному циклу позволяет для .Достаточно широкого класса входных сигналов значительно сократить (до 25-50 раз) время обработки и следовательно, повысить быстродействие устройства.

Формула изобретения

1, Устройство для передачи и приема информации, содержаддеё на передающей стороне первый блок памяти, выходы которого соединены с одноименными первыми информационными вxoдa ш порогового блока, синхронизатор,первый, вторые и третьи выходы которого соединены соответственно с входом формирователя базисных сигналов, со- ответствуюп ими управляющими входами первого блока памяти и соответствующими управляющими входами ортогонального нормал:изатора, выходы формирователя базисных сигналов соединены с одноименньпум первыми входами соответствующих первых умножителей, выходы которых соеданены с соответствующими входами первого сумматора, выходы первого сумматора соединены с соответствующими входами блока нелинейных преобразователей, выходы которого соединены с соответствуюпщми ин- формацион1-гымт-1 входами ортогонального нормализатора, вторые умножи : ели, выходы которых соединены с соответствующими входами второго cy fмaтopa, выходы которого соединены с одноименными вторыми информационными входами

порогового блока, первые выходы которого соединены с соответствующими первыми информационными входами выходного блока, первые выходы которого соединены с каналом связи, на приемной стороне - входной блок, информационные входгз которого подключены к каналу связи, первые и вторые выходы входного блока соединены с одноименными первыми входами соответствующих первых и вторых умножителей, формирователь базисных сигналов, выходы которого соединены с одноименными вторыми входами соответствующих первых умножителей, выходы

которых соединены с соответствуюш ми входами первого сумматора, выходы которого соединены с соответствующими входами блока нелинейных преобразователей, соединенного с соответствующими информационными входами ортогонального нормализатора, выходы которого соединены с одноименными вторыми входами соответствующих вторых умножителей, выходы которых соединены с соответствуюшдми входами второго сумматора,и синхронизатор, отличающееся тем, что, с целью повышения быстродействия устройства, в него на передающей стороне введены второй, третий блоки переключателей и блоки ключей,корреляторы, выходы ортогонального нор- мализатора соединены соответствующими информационными входами второго блока памяти, выходы соединены с одноименными первыми входат-ш соответствующих вторых умножителей и одноименными первыми информационными входами соответствуюш 1х блоков переклю-

чателей, информационные входы блоков Переключателей подключены соответст- венно к одноименным выходам формирователя базисных сигналов, выходы блоков переключателей соединены с одно-

именными первыми информационнь5.ш входами соответствующих корреляторов,одноименные вторые информационные вхо- ды которых объединены соответственно и подключены к одноименным выходам

первого блока памяти,выходы корреляторов соединены с соответствующими вторыми информационными входами выходного блока и одноименными информационными входами соответствующих

15

блоков ключей, выходы блоков ключей соединены с соответствующими информационными входами третьего блока

одноименными вторыми информационными входами соответствующих первых умножителей, второй выход цорогово- го блока соединен с первым установочным входом синхронизатора и первым упрайляющим входом выходного блока, третий выход порогового блока соединен с вторым установочным входом синхронизатора и вторым управляющим входом,выходного блока, третьи информационные входы и вторые выходы которого подключены соответственно к одноименным выходам первого блока памяти и одноименным вторым входам соответствующих вторых умножителей, четвертый, пятые, щестые, седьмые, восьмые и девятый выходы синхронизатора соединены соответственно с управляющим входом третьего блока памяти, одноименными третьими управляющими входами выходного блока, одноименными управляющими входами порогового блока, объединенным - соответственно управляющими входами корреляторов, одноименными управляющими входами блоков переключателей и блоков ключей, информационные входы первого блока памяти, установочные входы порогового блока, тактовый вход, и вход Пуск синхронизатора передающей стороны являются соответственно информационными, устано- вочньми, первым тактовым входами и входом Пуск устройства, на приемной стороне введен блок элементов ИЛИ, третий, четвертый и пятые выходы входного блока соединены соответственно с соответствующими первыми входами блока элементов ИЛИ, входом Пуск и соответствующими установоч- ньми входами синхронизатора, первый, вторые и третьи выходы синхрони затора соединены с входом формиро ва- теля базисных сигналов, одноименными управляющими входами входного блока и одноименными управляющими входами ортогонального нормализатора, выхода второго сумматора соединены с одноименными вторыми входами блока элементов ИЛИ, тактовый вход синхронизатора и выходы блока элементов приемной стороны являются соответственно вторым тактовым входом и выходами устройства.

1399797

16

5

0

5

ются управляющими входами входного блока, выходы первого, второго элементов памяти и вторые выходы демультиплексора являются соответственно первыми, вторыми и третьими выходами входного блока, первый и вторые выходы дешифратора соединены соответственно с первым и соответствующими вторыми адресными входами демультиплексора и являются соответственно четвертым и пятыми выходами входного блока,

3, Устройство по По1, отличающееся тем, что выходной блок содержит демультиплексор, элементы памяти, генератор,и мультиплексор, первые и вторые выходы демультиплексора соединены соответственно с соответствующими информационными входами первого элемента памяти и первыми информационными входами это

го элемента памяти соединены с соответствующими вторыми информационными входами второго элемента памяти, первые выходы которого соединены с соответствующими первыми информаци-.

онными входами мультиплексора, выходы генератора соединены с соответствующими вторыми информационными входами мультиплексора, выходы генератора соединены с cooтвeтctвyющимн

вторьми информационными входами мультиплексора, третьи информационные входы мультиплексора, информационные входы демультиплексора и четвертые информационные входы мультиплексора

являются соответственно первыми, вто- и третьими информационными вхо- дами вькодного блока, объединенные первые управлякндие входы генератора и мультиплексора и объединенные вторые управляющие входы генератора и мультиплексора являются соответствен- но первыми: и вторыми управляющими вхо дами выходного блока, управляющий вход демультиплексора, объединенные первые управляющие входы первого и второго элементов памяти, вторые управляющие входы первого, второго эле- ментов памяти, третий, четвертый уп- равляющие входы мультиплексора и третий управляющий вход, генератора являются третьими управляющими входами выходного блока.

4, Устройство по п,1, о т л и ч а- ю щ е е с я тем, что пороговый блок содержит вычитатель, умножитель, матор и пороговые элементы,, выходы вычитателя соединены с соответству-. ющими первыми и вторь ми входами yt-i-

от2д

K2S от 28

ножителя, выходы которого соединены с соответствуюп1 ми информационными входами сумматора, первые и вторые входы вычитателя являются соответственно первыми и вторыми информационными входами порогового блока, уп- . равляющий вход и вход Сброс сумматора являются управляющими входами порогового блока, первые входы первого и второго пороговых элементов являются установочными входами порогового блока, выходы сумматора соединены с одноименными вторыми входами первого, второго пороговых элементов и являются первьми выходами порогового блока, выходы первого и второго пороговых элементов являются соответственно вторым и третьим выходами порого.вого блока.

Фиг. 2

к 25

Фиг л

Фиг. 5

it

cSjxK .cm/af

РСИ- м -

ЙИ.

а - nepedava коэффициентоб (8g ад.

S - передача коэффициентов и ошибки (gi 6g ,fp)

S- передачи omsvemoS сигнала S(t) (.

Фиг. W

| Устройство для ассоциативного сжатия информации | 1983 |

|

SU1120390A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056244A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-29—Подача