Изобретение относится к области вычислительной техники и может найти применение при построении коммутационных средств мультипроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением и информационно-измерительных систем.

Известен модуль матричного коммутатора, содержащий три блока организации очередей сообщений, регистр идентификатора модуля, блок анализа очереди сообщений, мультиплексор, регистр, демультиплексор, триггер, блок синхронизации, два элемента сравнения, два дешифратора и элемент И (а.с. СССР 1575167, G 06 F 7/00, 15/16; опубл. 30.06.90, БИ 24).

Недостатком данного модуля являются ограниченные коммутационные возможности, что обусловлено наличием только двух входных и двух выходных каналов для подключения к соседним модулям в составе коммутатора.

Наиболее близким к предлагаемому модулю по технической сущности является устройство формирования маршрута сообщения в однородной вычислительной системе, содержащее группу блоков буферной памяти, три регистра, триггер, счетчик, блок сравнения, блок выбора направления, генератор тактовых импульсов, демультиплексор, мультиплексор, дешифратор, два элемента И, группу элементов И, три элемента ИЛИ, три одновибратора, два элемента задержки (а.с. СССР 1287172, G 06 F 15/16; опубл. 30.01.87, БИ 4).

Недостатком указанного устройства является узкая область применения ввиду значительного числа внешних входов и выходов, требуемых для организации его взаимодействия с другими аналогичными устройствами в составе соответствующей коммутационной сети (структуры).

Технической задачей, на решение которой направлено заявляемое изобретение, является расширение области применения устройства на основе минимизации числа внешних входов и выходов, требуемых для организации его взаимодействия с другими аналогичными устройствами (модулями) коммутационной структуры.

Техническая задача решается тем, что в модуль для ретрансляции сообщений в коммутационной структуре, содержащий группу блоков буферной памяти, блок сравнения, блок выбора направлений, регистр адреса, регистр данных, регистр приема, первый, второй и третий одновибраторы, мультиплексор, счетчик, дешифратор, генератор тактовых импульсов, первый, второй и третий элементы ИЛИ, триггер запуска, элемент И, причем информационные выходы блоков буферной памяти группы с первого по восьмой соединены с информационными входами мультиплексора с первого по восьмой соответственно, выход которого соединен с информационными входами регистра адреса и регистра данных, выход регистра адреса соединен с третьим информационным входом блока выбора направлений, выход блока сравнения соединен с вторым информационным входом блока выбора направлений, выходы состояния блоков буферной памяти группы с первого по восьмой соединены с входом первого элемента ИЛИ, выход которого соединен со входами второго и третьего одновибраторов, выход второго одновибратора соединен с входом установки триггера запуска, выходы дешифратора с первого по восьмой соединены с входами опроса блоков буферной памяти группы с первого по восьмой соответственно, выход счетчика соединен с входом дешифратора и адресным входом мультиплексора, выход второго элемента ИЛИ соединен с входом сброса счетчика, вход задания адреса модуля соединен с первым информационным входом блока выбора направлений, дополнительно введены блок буферной памяти, группа регистров, группа демультиплексоров, группа триггеров, группа элементов ИЛИ, четвертый элемент ИЛИ, триггер переключения каналов, группа триггеров управления приемом, группа коммутаторов, причем выход первого одновибратора соединен с входом синхронизации блока выбора направлений, старшие разряды информационных входов модуля с первого по восьмой соединены с информационными входами демультиплексоров группы с первого по восьмой соответственно, первые информационные выходы которых соединены с информационными входами соответствующих регистров группы, выходы которых соединены с входом блока сравнения, девятый выход дешифратора соединен с входом опроса блока буферной памяти, первые разряды информационных входов модуля с первого по восьмой соединены со вторыми входами элементов ИЛИ группы с первого по восьмой соответственно, вторые разряды информационных входов модуля с первого по восьмой соединены с первыми входами элементов ИЛИ группы с первого по восьмой соответственно и с входами синхронизации регистров группы с первого по восьмой соответственно, третьи разряды информационных входов модуля с первого по восьмой соединены с входами записи блоков буферной памяти группы с первого по восьмой соответственно, девятый информационный вход модуля соединен с информационным входом блока буферной памяти, вход стробирования модуля соединен с входом записи блока буферной памяти, выход состояния блока буферной памяти соединен с входом первого элемента ИЛИ, информационный выход блока буферной памяти соединен с девятым информационным входом мультиплексора, выходы всех элементов ИЛИ группы соединены со счетными входами соответствующих триггеров управления приемом группы, прямые выходы которых соединены с адресными входами соответствующих демультиплексоров группы, вторые информационные выходы которых соединены с информационными входами блоков буферной памяти группы с первого по восьмой соответственно, выходы коэффициентов загрузки которых соединены с первыми информационными входами коммутаторов группы с первого по восьмой соответственно, прямой выход триггера запуска соединен с входом запуска генератора тактовых импульсов, выход третьего одновибратора соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса триггера запуска, вход сброса модуля соединен с вторым входом третьего элемента ИЛИ, входами сброса триггеров группы, входами сброса регистров группы, входами сброса всех блоков буферной памяти, входом сброса триггера переключения каналов, входом сброса регистра приема, входами сброса регистра адреса и регистра данных, входами сброса всех триггеров управления приемом группы и с первым входом второго элемента ИЛИ, первый выход генератора тактовых импульсов соединен со счетным входом счетчика и с первыми разрядами информационных выходов модуля с первого по восьмой, второй выход генератора тактовых импульсов соединен с входом первого одновибратора, входами синхронизации регистра адреса и регистра данных, с вторым входом четвертого элемента ИЛИ и с вторыми разрядами информационных выходов модуля с первого по восьмой, выход четвертого элемента ИЛИ соединен со счетным входом триггера переключения каналов, третий выход генератора тактовых импульсов соединен со входами синхронизации всех блоков буферной памяти, с первым входом элемента И, с первым входом четвертого элемента ИЛИ, со счетными входами триггеров группы и с третьими разрядами информационных выходов модуля с первого по восьмой, выход элемента И соединен с вторым входом второго элемента ИЛИ, девятый выход дешифратора соединен с вторым входом элемента И, выход коэффициента загрузки блока буферной памяти соединен с десятым информационным выходом модуля, первый и второй информационные выходы блока выбора направлений соединены с входами установки с первого по восьмой и девятого триггеров группы соответственно, прямые выходы которых соединены с третьими управляющими входами коммутаторов группы с первого по восьмой и с входом синхронизации регистра приема соответственно, выходы регистра адреса и регистра данных соединены с вторыми информационными входами коммутаторов группы, выход регистра данных соединен с информационным входом регистра приема, выходы коммутаторов группы с первого по восьмой соединены со старшими разрядами информационных выходов модуля с первого по восьмой соответственно, выход регистра приема соединен с девятым информационным выходом модуля, прямой выход триггера переключения каналов соединен с первыми и вторыми управляющими входами коммутаторов группы с первого по восьмой.

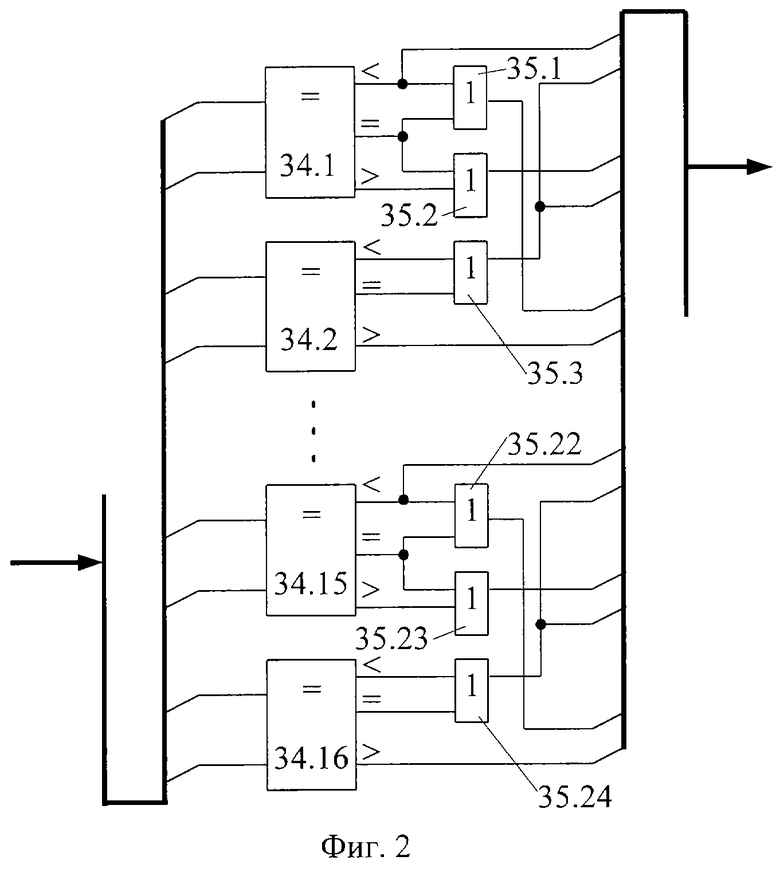

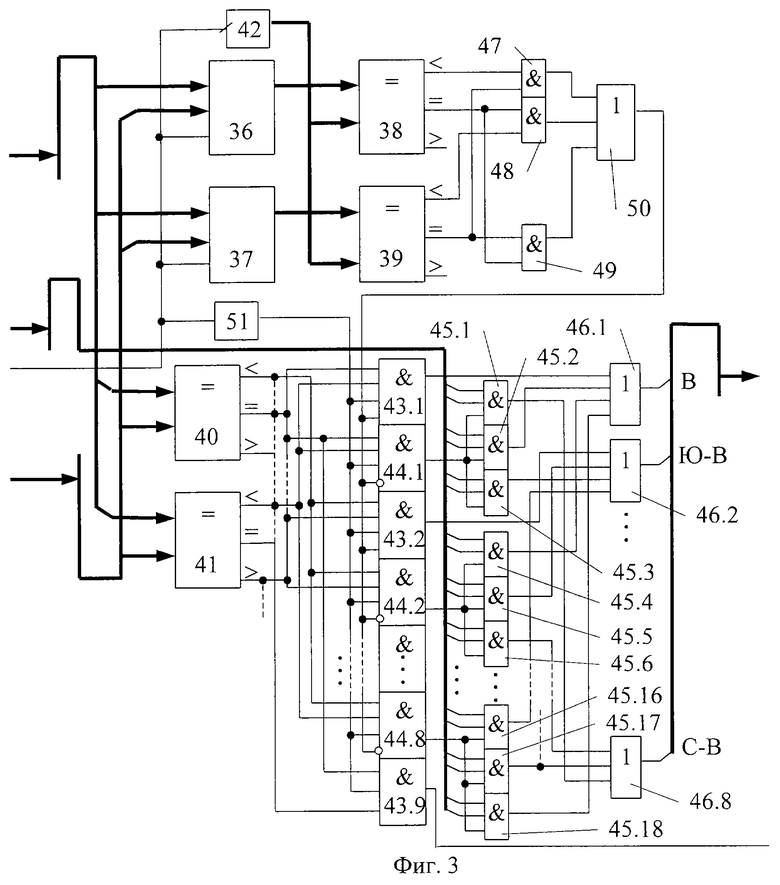

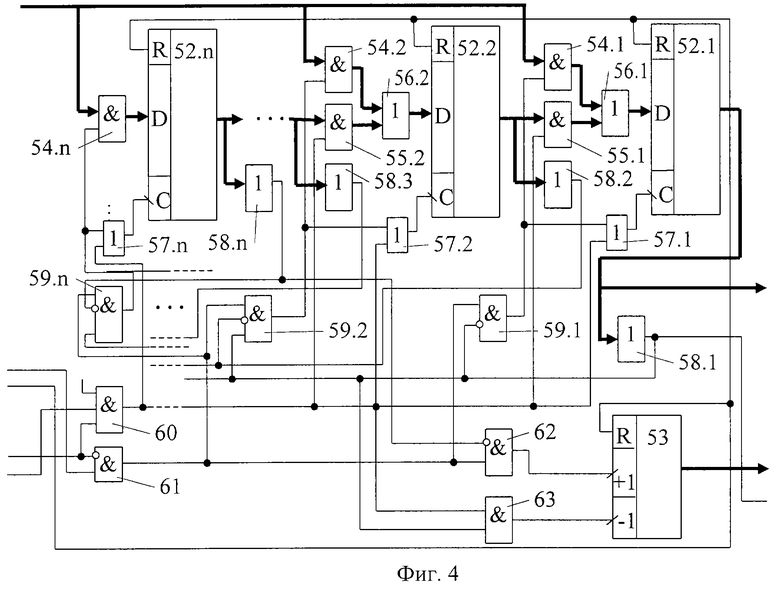

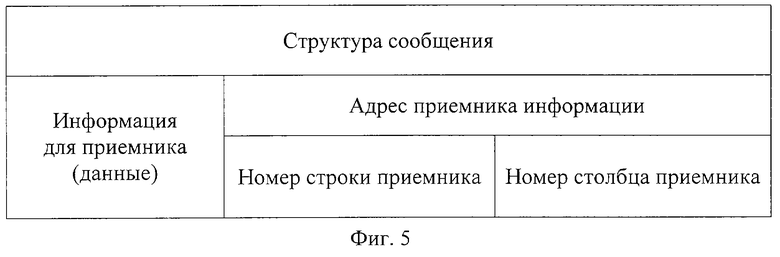

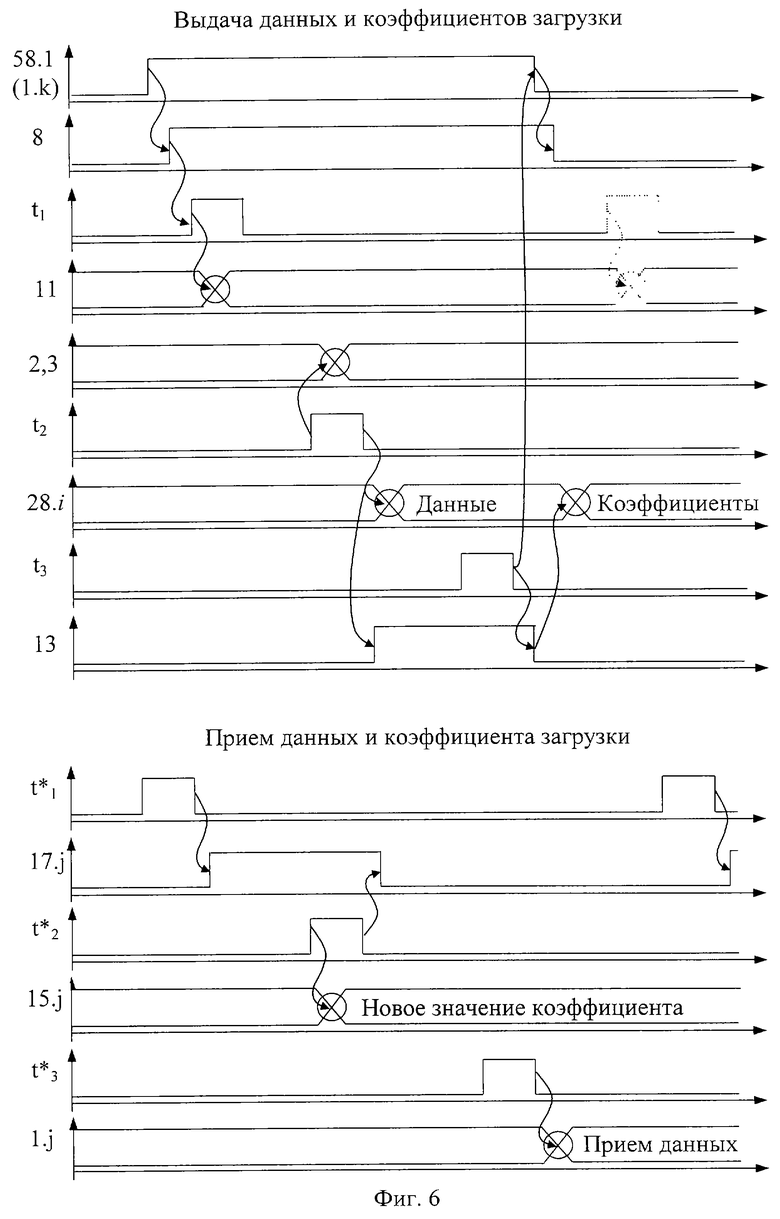

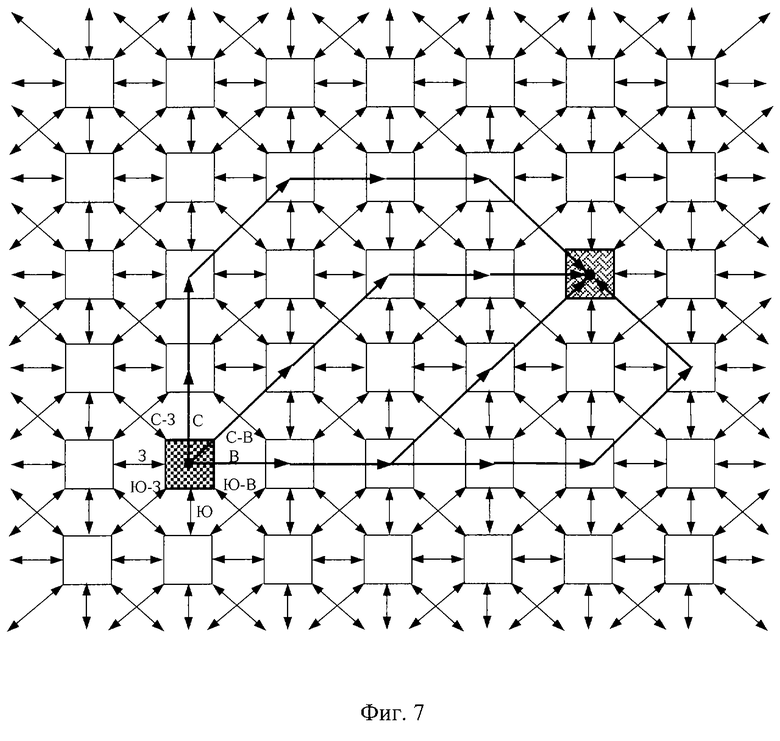

Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема модуля для ретрансляции сообщений в коммутационной структуре; на фиг.2 изображена функциональная схема блока сравнения; на фиг. 3 показана функциональная схема блока выбора направлений; на фиг.4 приведена функциональная схема блока буферной памяти, на фиг.5 дана структура сообщений; временные диаграммы на фиг.6 иллюстрируют работу модуля в двух режимах: выдачи данных/коэффициентов загрузки и приема данных/коэффициентов загрузки; на фиг. 7 проиллюстрирована коммутационная структура и пример возможных путей прохождения сообщений между произвольными ее модулями.

Общие особенности изобретения состоят в следующем. Данный модуль предназначен для совместного с другими аналогичными модулями функционирования в составе коммутационной структуры (сети). Сеть имеет матричную организацию, в которой каждый модуль связан по входам и по выходам с восемью соседними модулями сети. Каждый модуль сети обслуживает соответствующее операционное устройство (например, процессорный элемент), принимая от него информацию, подлежащую передаче другим операционным устройствам, и передавая ему информацию от других операционных устройств. Взаимодействие модулей сети осуществляется на основе обмена сообщениями через другие (транзитные) модули. Каждое сообщение включает информационную и адресную части (фиг.5). В информационной части сообщения размещается информация (данные), подлежащая передаче, а адресная часть содержит адресную информацию, которая определяет операционное устройство-приемник данных (номер строки и номер столбца) и порядок передачи сообщения через транзитные модули.

Выбор направления передачи пришедшей информации в предлагаемом модуле происходит, как и в прототипе, по следующим правилам. Адресная часть пришедшей информации сравнивается с адресом данного модуля по номерам строки и столбца. В результате определяется одно из девяти возможных направлений передачи (восемь направлений на соседние с ним модули, девятое - на обработку данному операционному устройству). Одновременно определяется наименее загруженное направление для восьми секторов передачи данных в соответствии с первоначально выбранным направлением. Например, для направления "Восток" (фиг. 7) анализируются на загрузку три направления этого сектора: "Юго-восток" ("Ю-В"), "Восток" ("В") и "Северо-восток" ("С-В"), для направления "Ю-В" анализируются направления "В", "Ю-В" и "Юг" ("Ю") и т.д. Алгоритм выбора минимально загруженного направления в каждом из восьми секторов на примере сектора направления "Восток" будет следующим. Пусть коэффициенты загрузки направлений этого сектора следующие: для направления "С-В" равно А, для направления "В" - В, для направления "Ю-В" - С (под коэффициентом загрузки направления понимается длина очереди в блоке буферной памяти, в соседнем модуле по соответствующему направлению). Если (В≤А) (В≤С)=1, то направлением передачи в этом секторе является "В", если (A<B)

(В≤С)=1, то направлением передачи в этом секторе является "В", если (A<B) (A≤C)=1, то направлением передачи является "С-В", если (С<А)

(A≤C)=1, то направлением передачи является "С-В", если (С<А) (А≤В)=1, то направлением передачи является "Ю-В". Эта информация модифицирует направление выбранного сектора передачи сообщения. Таким образом осуществляется выбор направления передачи сообщений по кратчайшему пути с минимальной задержкой (в связи с выбором минимально загруженных линий). Если разница между номерами строк и столбцов сравниваемых адресов не превышает единицы, то модификация направления передачи сообщения не производится.

(А≤В)=1, то направлением передачи является "Ю-В". Эта информация модифицирует направление выбранного сектора передачи сообщения. Таким образом осуществляется выбор направления передачи сообщений по кратчайшему пути с минимальной задержкой (в связи с выбором минимально загруженных линий). Если разница между номерами строк и столбцов сравниваемых адресов не превышает единицы, то модификация направления передачи сообщения не производится.

Ключевой особенностью изобретения является то, что информация о состоянии загруженности соседних модулей сети обновляется в каждом такте работы. Поэтому при определении направления выдачи сообщений модуль в любой момент времени обладает истинной информацией о загруженности входных очередей соседних с ним модулей и на основании этого осуществляет выдачу по оптимальному направлению. При этом предлагаемый модуль осуществляет передачу сообщений и коэффициентов загрузки по одним и тем же информационным линиям, что существенно повышает эффективность его использования в коммутационной сети по сравнению с прототипом, т.к. для связи с соседними модулями используется меньшее количество линий.

Модуль для ретрансляции сообщений в коммутационной структуре (фиг.1) включает группу блоков 1.1-1.8 буферной памяти и блок 1.9 буферной памяти, регистр 2 адреса, регистр 3 данных, регистр 4 приема, блок 5 сравнения, блок 6 выбора направлений, мультиплексор 7, триггер 8 запуска, генератор 9 тактовых импульсов, счетчик 10, дешифратор 11, группу коммутаторов 12.1-12.8, триггер 13 переключения каналов, группу триггеров 14.1-14.9, группу регистров 15.1-15.8, группу демультиплексоров 16.1-16.8, группу триггеров 17.1-17.8 управления приемом, элемент И 18, группу элементов ИЛИ 19.1-19.8, первый элемент ИЛИ 20, второй элемент ИЛИ 21, четвертый элемент ИЛИ 22, второй одновибратор 23, третий одновибратор 24, первый одновибратор 25, третий элемент ИЛИ 26, причем старшие разряды информационных входов 32.1-32.8 модуля соединены с информационными входами демультиплексоров 16.1-16.8 соответственно, первые информационные выходы которых подключены к информационным входам регистров 15.1-15.8 соответственно, выходы которых соединены с входом блока 5 сравнения, выход которого соединен с вторым информационным входом блока 6 выбора направлений, первые разряды информационных входов 32.1-32.8 модуля соединены с вторыми входами элементов ИЛИ 19.1-19.8 соответственно, выходы которых соединены со счетными входами триггеров 17.1-17.8 управления приемом соответственно, прямые выходы которых соединены с адресными входами демультиплексоров 16.1-16.8 соответственно, вторые информационные выходы которых соединены с информационными входами блоков 1.1-1.8 буферной памяти соответственно, вторые разряды информационных входов 32.1-32.8 модуля соединены с первыми входами элементов ИЛИ 19.1-19.8 соответственно и с входами синхронизации регистров 15.1-15.8 соответственно, третьи разряды информационных входов 32.1-32.8 модуля соединены с входами записи блоков 1.1-1.8 буферной памяти соответственно, информационный вход 30 модуля соединен с информационным входом блока 1.9 буферной памяти, стробирующий вход 31 модуля соединен с входом записи блока 1.9 буферной памяти, выходы состояния блоков 1.1-1.9 буферной памяти соединены с входом элемента ИЛИ 20, выход которого соединен с входами одновибраторов 23 и 24, выход одновибратора 23 соединен с входом установки триггера 8 запуска, выход одновибратора 24 соединен с первым входом элемента ИЛИ 26, выход которого соединен со входом сброса триггера 8 запуска, прямой выход которого соединен со входом запуска генератора 9 тактовых импульсов, первый выход которого соединен со счетным входом счетчика 10 и с первыми разрядами информационных выходов 28.1-28.8 модуля, второй выход генератора 9 тактовых импульсов соединен с входами синхронизации регистра 2 адреса и регистра 3 данных, с входом одновибратора 25, с вторыми разрядами информационных выходов 28.1-28.8 модуля и с вторым входом элемента ИЛИ 22, выход которого соединен со счетным входом триггера 13 переключения каналов, прямой выход которого соединен с первыми и вторыми управляющими входами коммутаторов 12.1-12.8, третий выход генератора 9 тактовых импульсов соединен с входами синхронизации блоков 1.1-1.9 буферной памяти, с первым входом элемента И 18, с первым входом элемента ИЛИ 22, со счетными входами триггеров 14.1-14.9 и с третьими разрядами информационных выходов 28.1-28.8 модуля, выход счетчика 10 соединен с входом дешифратора 11 и с адресным входом мультиплексора 7, выходы дешифратора 11 с первого по девятый соединены с входами опроса блоков 1.1-1.9 буферной памяти соответственно, девятый выход дешифратора 11 соединен с вторым входом элемента И 18, выходы коэффициентов загрузки блоков 1.1-1.8 буферной памяти соединены с первыми информационными входами коммутаторов 12.1-12.8 соответственно, выход коэффициента загрузки блока 1.9 буферной памяти соединен с информационным выходом 33 модуля, выход одновибратора 25 соединен с входом синхронизации блока 6 выбора направлений, первый и второй информационные выходы которого соединены с входами установки триггеров 14.1-14.8 и 14.9 соответственно, прямые выходы которых соединены с третьими управляющими входами коммутаторов 12.1-12.8 и с входом синхронизации регистра 4 приема соответственно, выход которого соединен с информационным выходом 28.9 модуля, выходы коммутаторов 12.1-12.8 соединены со старшими разрядами информационных выходов 28.1-28.8 модуля соответственно, выход мультиплексора 7 соединен с информационными входами регистра 2 адреса и регистра 3 данных, выход регистра 2 адреса соединен с третьим информационным входом блока 6 выбора направлений, выход регистра 2 адреса и выход регистра 3 данных соединены с вторыми информационными входами коммутаторов 12.1-12.8, выход регистра 3 данных соединен с информационным входом регистра 4 приема, вход 29 сброса модуля соединен с вторым входом элемента ИЛИ 26, с входами сброса триггеров 17.1-17.8 управления приемом, с входами сброса регистров 15.1-15.8, с входами сброса блоков 1.1-1.9 буферной памяти, с первым входом элемента ИЛИ 21, с входом сброса триггера 13 переключения каналов, с входом сброса регистра 4 приема, с входом сброса регистра 2 адреса, с входом сброса регистра 3 данных и с входами сброса триггеров 14.1-14.9, вход 27 задания адреса модуля соединен с первым информационным входом блока 6 выбора направлений, выход элемента И 18 соединен с вторым входом элемента ИЛИ 21, выход которого соединен с входом сброса счетчика 10, информационные выходы блоков 1.1-1.9 буферной памяти соединены с первого по девятый информационными входами мультиплексора 7 соответственно.

Назначение блоков и элементов модуля для ретрансляции сообщений в коммутационной структуре заключается в следующем.

Блоки 1.1-1.9 буферной памяти (фиг.4) служат для приема, хранения и выдачи данных (сообщений) в порядке поступления. Блоки 1.1-1.8 принимают данные от соседних модулей, а блок 1.9 - от операционного устройства.

Регистр 2 адреса и регистр 3 данных необходимы для хранения соответственно адреса приемника сообщения и информации для приемника (фиг.5) во время обработки сообщения.

Регистр 4 приема предназначен для фиксации информации, пришедшей обслуживаемому операционному устройству.

Блок 5 сравнения (фиг.2) вычисляет код, модифицирующий направление дальнейшей передачи сообщения, по значениям коэффициентов загрузки соседних модулей из регистров 15.1-15.8.

Блок 6 выбора направления (фиг.3) формирует код направления передачи сообщения с учетом загрузки соседних модулей.

Мультиплексор 7 используется для коммутации сообщений из ББП 1.1-1.9 на регистры 2 и 3.

Триггер 8 запуска управляет включением/выключением генератора 9 тактовых импульсов.

Генератор 9 тактовых импульсов вырабатывает три сдвинутые во времени последовательности тактовых импульсов t1, t2, t3, синхронизирующие работу элементов и блоков модуля.

Счетчик 10 служит для организации последовательного выбора ББП.

Дешифратор 11 предназначен для преобразования двоичного кода со счетчика 10 в соответствующий унитарный код выбора ББП.

Коммутаторы 12.1-12.8 обеспечивают попеременную выдачу данных и коэффициентов загрузки на выходы 28.1-28.8 модуля соответственно.

Триггер 13 переключения каналов требуется для управления коммутаторами 12.1-12.8.

Триггеры 14.1-14.9 необходимы для временной фиксации кода выбора направления с блока 6 выбора направлений.

Регистры 15.1-15.8 введены для буферизации коэффициентов загрузки, поступающих от соседних модулей.

Демультиплексоры 16.1-16.8 осуществляют коммутацию поступающей информации либо в ББП (если это данные), либо в регистры 15.1-15.8 (если это коэффициенты загрузки).

Триггеры 17.1-17.8 управления приемом управляют работой демультиплексоров 16.1-16.8 соответственно.

Элементы И 18 и ИЛИ 21 необходимы для формирования сигнала сброса счетчика 10.

Элементы ИЛИ 19.1-19.8 требуются для формирования импульсов управления для триггеров 17.1-17.8 соответственно.

Элементы ИЛИ 20, 26 и одновибраторы 23, 24 предназначены для формирования импульсов управления триггером 8 запуска.

Элемент ИЛИ 22 служит для формирования импульсов управления триггером 13 переключения каналов.

Одновибратор 25 необходим для генерации импульсов синхронизации работы блока 6 выбора направлений (фиг.3).

Блок 5 сравнения (фиг.2) содержит схемы 34.1-34.16 сравнения, элементы ИЛИ 35.1-35.24, причем вход блока сравнения соединен с первыми и вторыми входами схем 34.1-34.16 сравнения, первые выходы которых соединены с первыми входами элементов ИЛИ 35.1, 35.3, 35.4, 35.6, 35.7, 35.9, 35.10, 35.12, 35.13, 35.15, 35.16, 35.18, 35.19, 35.21, 35.22, 35.24 соответственно, вторые выходы схем 34.1-34.16 сравнения соединены с вторыми входами элементов ИЛИ 35.1, 35.3, 35.4, 35.6, 35.7, 35.9, 35.10, 35.12, 35.13, 35.15, 35.16, 35.18, 35.19, 35.21, 35.22, 35.24 соответственно, первые выходы схем 34.1, 34.3, 34.5, 34.7, 34.9, 34.11, 34.13, 34.15 сравнения соединены с выходом блока сравнения, вторые выходы схем 34.1, 34.3, 34.5, 34.7, 34.9, 34.11, 34.13, 34.15 сравнения соединены с первыми входами элементов ИЛИ 35.2, 35.5, 35.8, 35.11, 35.14, 35.17, 35.20, 35.23 соответственно, третьи выходы схем 34.1, 34.3, 34.5, 34.7, 34.9, 34.11, 34.13, 34.15 сравнения соединены с вторыми входами элементов ИЛИ 35.2, 35.5, 35.8, 35.11, 35.14, 35.17, 35.20, 35.23 соответственно, третьи выходы схем 34.2, 34.4, 34.6, 34.8, 34.10, 34.12, 34.14, 34.16 сравнения соединены с выходом блока сравнения, выходы элементов ИЛИ 35.1-35.24 соответствующим образом соединены с выходом блока сравнения.

Блок 6 выбора направлений (фиг.3) содержит вычитатели 36 и 37, схемы 38-41 сравнения, узел 42 памяти константы, первую группу элементов И 43.1-43.8, первый элемент И 43.9, вторую группу элементов И 44.1-44.8, группу блоков элементов И 45.1-45.18, группу элементов ИЛИ 46.1-46.8, второй 47, третий 48 и четвертый 49 элементы И, элемент ИЛИ 50, элемент 51 задержки, причем первый информационный вход блока выбора направлений соединен с первыми информационными входами вычитателей 36 и 37 и с первыми информационными входами схем 40 и 41 сравнения, второй информационный вход блока выбора направлений соединен с первыми и вторыми входами группы блоков элементов И 45.1-45.18, третий информационный вход блока выбора направлений соединен с вторыми информационными входами вычитателей 36 и 37 и с вторыми информационными входами схем 40 и 41 сравнения, вход синхронизации блока выбора направлений соединен со стробирующим входом узла 42 памяти константы, со стробирующими входами вычитателей 36 и 37, со стробирующим входом элемента 51 задержки, выход которого соединен с третьими входами первой группы элементов И 43.1-43.8, с третьими входами второй группы элементов И 44.1-44.8 и с вторым входом элемента И 43.9, выход узла 42 памяти константы соединен с вторыми информационными входами схем 38 и 39 сравнения, выходы вычитателей 36 и 37 соединены с первыми информационными входами схем 38 и 39 сравнения соответственно, первый выход схемы 38 сравнения соединен с первым входом элемента И 47, выход которого соединен с первым входом элемента ИЛИ 50, выход которого соединен с четвертыми входами первой группы элементов И 43.1-43.8 и с четвертыми входами второй группы элементов И 44.1-44.8, второй выход схемы 38 сравнения соединен с первым входом элемента И 48 и с вторым входом элемента И 49, выходы элементов И 48 и 49 соединены с вторым и третьим входами элемента ИЛИ 50 соответственно, первый выход схемы 39 сравнения соединен с вторым входом элемента И 48, второй выход схемы 39 сравнения соединен с вторым входом элемента И 47 и первым входом элемента И 49, выходы схем 40 и 41 сравнения соединены с первыми и вторыми входами первой группы элементов И 43.1-43.8, с первыми и вторыми входами второй группы элементов И 44.1-44.8 и с первым, третьим входами элемента И 43.9, выходы первой группы элементов И 43.1-43.8 соединены с первыми входами группы элементов ИЛИ 46.1-46.8 соответственно, выходы второй группы элементов И 44.1-44.8 соединены с третьими входами группы блоков элементов И 45.1-45.18 соответственно, выходы которых соответствующим образом соединены с входами группы элементов ИЛИ 46.1-46.8, выходы которых соединены с первым информационным выходом блока выбора направлений, выход элемента И 43.9 соединен с вторым информационным выходом блока выбора направлений.

Блок 1. i буферной памяти (ББП), i=1,2,...,9 (фиг.4), содержит регистры 52.1-52. n (где n - максимальная длина очереди сообщений), счетчик 53 загрузки, первую группу ключей 54.1-54.n, вторую группу ключей 55.1-55.n-1, группу блоков элементов ИЛИ 56.1-56.n-1, первую группу элементов ИЛИ 57.1-57-n, вторую группу элементов ИЛИ 58.1-58.n, группу элементов И 59.1-59.n, первый 60, второй 61, третий 62 и четвертый 63 элементы И, причем информационный вход блока буферной памяти соединен с первыми входами ключей 54.1-54. n, вход записи блока буферной памяти соединен с вторым входом элемента И 61, вход сброса блока буферной памяти соединен с входом сброса счетчика 53 загрузки и с входами сброса регистров 52.1-52.n, вход синхронизации блока буферной памяти соединен с третьим входом элемента И 60 и с первым входом элемента И 61, вход опроса блока буферной памяти соединен с вторым входом элемента И 60, выходы элементов И 59.1-59.n соединены с первыми входами элементов ИЛИ 57.1-57.n соответственно и с вторыми входами ключей 54.1-54.n соответственно, выходы ключей 54.1-54.n-1 соединены с первыми входами блоков элементов ИЛИ 56.1-56.n-1 соответственно, выходы которых соединены с информационными входами регистров 52.1-52.n-1 соответственно, выход ключа 54.n соединен с информационным входом регистра 52.n, информационные выходы регистров 52.2-52.n соединены с первыми входами ключей 55.1-55.n-1 соответственно и с входами элементов ИЛИ 58.2-58.n соответственно, информационный выход регистра 52.1 соединен с входом элемента ИЛИ 58.1 и с информационным выходом блока буферной памяти, выход элемента ИЛИ 58.1 соединен с выходом состояния блока буферной памяти, с первым входом элемента И 60 и с вторым входом элемента И 63, выходы элемента ИЛИ 58.k (k=1...n-1) подключены к соответствующим прямым входам элементов И 59.k+1-59.n, выход элемента ИЛИ 58.k подключен к инверсному входу элемента И 59.k, выход элемента И 60 соединен с вторыми входами элементов ИЛИ 57.1-57.n, с вторыми входами ключей 55.1-55. n-1 и с первым входом элемента И 63, выход которого соединен с вычитающим входом счетчика 53 загрузки, выходы элементов ИЛИ 57.1-57.n соединены с входами синхронизации регистров 52.1-52.n соответственно, выход элемента И 61 соединен с первыми входами элементов И 59.1-59.n и с вторым входом элемента И 62, выход элемента ИЛИ 58.n соединен с инверсным входом элемента И 59. n и с первым входом элемента И 62, выход которого соединен с суммирующим входом счетчика 53 загрузки, выход которого соединен с выходом коэффициента загрузки блока буферной памяти, выходы ключей 55.1-55.n-1 подключены к вторым входам блоков элементов ИЛИ 56.1-56.n-1 соответственно.

Рассмотрим работу предлагаемого модуля для ретрансляции сообщений в коммутационной структуре.

Работа модуля включает следующие этапы: а) исходное состояние; б) выдача данных и их прием; в) выдача коэффициентов загрузки и их прием. Рассмотрим последовательно каждый из них.

Исходное состояние.

Перед началом работы модуля на вход 29 сброса подается единичный импульс, который обнуляет все элементы памяти. На входах 32.1-32.8 модуля, на входе 31, на выходах 28.1-28.9 модуля в начальный момент присутствуют нулевые сигналы; генератор 9 тактовых импульсов выключен. На входе 27 модуля устанавливается код адреса (номер строки и номер столбца) данного модуля относительно других модулей в составе коммутационной сети.

Запуск модуля происходит при поступлении данных (сообщения) в один из ББП. Если данные передаются операционным устройством, то они записываются в ББП 1.9. В модуль они поступают через информационный вход 30. Синхронизация записи данных происходит по импульсу, проходящему через стробирующий вход 31 на вход записи ББП 1.9. Как только блок 1.9 примет данные, на его выходе состояния устанавливается единичный сигнал, который инициирует процесс выдачи данных. (Запись информации в ББП происходит аналогично прототипу и поэтому подробно не рассматривается.)

После записи данных в один из ББП на выходе элемента ИЛИ 20 возникает положительный перепад уровня сигнала, который обеспечивает установку триггера 8 и тем самым включает генератор 9 тактовых импульсов.

Выдача данных и их прием.

Режим выдачи данных инициируются только при условии наличия данных в одном из ББП 1.j (j=1...9).

Очередной импульс t1 попадает на счетный вход счетчика 10, тем самым устанавливая на его выходах код номера очередного ББП, начиная с ББП 1.1. Данный код настраивает мультиплексор 7 на передачу данных с выбранного ББП в регистры адреса 2 и данных 3. Также, данный код преобразуется дешифратором 11 таким образом, что на вход опроса выбранного ББП подается единичный сигнал, подготавливающий ББП к сдвигу данных. Одновременно импульс t1 через выход 28. j модуля передается в соседний модуль, который будет принимать данные, и настраивает его на прием (этот процесс подробно рассматривается ниже при описании режима приема данных).

По следующему тактовому импульсу t1 от генератора 9 осуществляется установка триггера 13 в единичное состояние, разрешающее передачу данных через коммутаторы 12.1, . . ., 12.8 на выходы 28.1,..., 28.9 модуля. Также по переднему фронту этого импульса осуществляется запись данных, выставленных выбранным ББП, в регистр 2 адреса и регистр 3 данных. По заднему фронту этого же импульса на выходе одновибратора 25 выдается единичный импульс, синхронизирующий работу блока 6 выбора направлений. Блок 6, используя адрес операционного устройства - приемника данных, адрес текущего модуля и коэффициенты загрузки соседних модулей, определяет оптимальное направление передачи данных (подробно работа блока 6 выбора направлений рассматривается в прототипе). Блок 6 устанавливает один из триггеров 14.1,..., 14.9 в единичное состояние и тем самым открывает соответствующий коммутатор 12.1,..., 12.8 или регистр приема 4 (если сообщение предназначено для текущего операционного устройства). По импульсу t2 на выходах одного из коммутаторов 12.1,. . . , 12.8 осуществляется выдача данных в выбранном направлении (в случае с текущим операционным устройством данные появляются на выходе регистра 4 приема и, следовательно, на выходе 28.9 модуля).

Очередной тактовый импульс t3 с генератора 9 подается на вход синхронизации ББП l. j (j=1,...,9) и задним фронтом синхронизирует сдвиг очереди данных выбранного ББП. Этот же импульс через выход 28.j модуля обеспечивает прием выданной информации соседним модулем.

По завершении выдачи сообщения из выбранного ББП, если на выходе элемента ИЛИ 20 все еще присутствует единичный сигнал (данные еще есть в ББП 1.1,. . . , 1.9), процесс обработки продолжается с подачи новой последовательности импульсов t1, t2, t3 генератором 9 тактовых импульсов. При завершении обработки всех поступивших данных на выходе элемента ИЛИ 20 установится нулевой сигнал, который поступит на одновибратор 24. Одновибратор 24 выдаст единичный импульс, сбрасывающий триггер 8 запуска в нулевое состояние, и тем самым приостановит работу генератора 9 тактовых импульсов.

Режим приема данных начинается с приходом импульса t2* от соседнего модуля сети (символ '*' означает, что импульс берется от генератора 9 соседнего модуля) на второй разряд одного из входов 32.1-32.8 модуля (фиг.1). Данный импульс поступает через элемент ИЛИ 19.j (j=1...8) на счетный вход триггера 17. j и задним фронтом переводит его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 17.j поступает на адресный вход демультиплексора 16.j, тем самым подготавливая его к передаче данных от соседнего модуля на информационный вход соответствующего блока буферной памяти. Далее на входе 32.j модуля устанавливаются данные от соседнего модуля, которые записываются в ББП 1.j. Синхронизация этого процесса осуществляется по заднему фронту импульса t3*, идущему также от соседнего модуля (процесс записи данных в ББП аналогичен прототипу). Если соседний модуль не выставляет данные, то в соответствующем ББП не происходит защелкивание информации по импульсу t3*.

Выдача коэффициентов загрузки и их прием.

Выдача коэффициентов загрузки происходит при нулевом состоянии триггера 13 (на интервале от заднего фронта импульса t3 до заднего фронта следующего импульса t2). Текущие коэффициенты загрузки - длины очередей сообщений - с блоков 1.1-1.8 через коммутаторы 12.1-12.8 проходят на выходы 28.1-28.8 модуля соответственно и затем поступают в соответствующие соседние модули. Их прием синхронизируется передним фронтом импульса t2 с генератора 9 текущего модуля. Выдача коэффициента загрузки ББП 1.9 осуществляется через информационный выход 33 модуля.

Прием коэффициента загрузки модулем осуществляется при приходе импульса t1* на первый разряд одного из входов 32.1-32.8 модуля (фиг.1). Импульс t1*, проходя через элемент ИЛИ 19.j (j=1,...,8), попадает на счетный вход триггера 17. j и задним фронтом переводит его в единичное состояние. Единичный сигнал с прямого выхода триггера 17.j попадает на адресный вход демультиплексора 16. j, тем самым подготавливая его к передаче коэффициента загрузки от соседнего модуля на информационный вход регистра 15.j. Второй импульс t2* от соседнего модуля попадает на вход синхронизации регистра 15.j и передним фронтом синхронизирует прием коэффициента загрузки в регистр 15.j. Таким образом, модуль в любой момент времени хранит истинную информацию о загруженности соседних модулей в регистрах 15.1-15.8 (реальные коэффициенты загрузки).

Временные диаграммы, иллюстрирующие работу модуля в описанных режимах, представлены на фиг.6.

Таким образом, как следует из описания, модуль для ретрансляции сообщений в коммутационной структуре обслуживает соответствующее операционное устройство, функционируя совместного с другими аналогичными модулями в составе коммутационной сети. Модуль принимает от операционного устройства информацию, подлежащую передаче другим операционным устройствам, и передает ему информацию от других операционных устройств. На основе введения дополнительного оборудования модуль осуществляет передачу сообщений и коэффициентов загрузки по одним и тем же информационным линиям, что сокращает количество взаимосвязей модулей в коммутационной сети. Модуль решает также задачу получения оперативной информации о загруженности соседних модулей на основе введения группы регистров 15. j, хранящих коэффициенты загрузки по всем направлениям передачи данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

Изобретение относится к вычислительной технике и применяется при построении коммутационных средств мультипроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением и информационно-измерительных систем. Технический результат заключается в расширение области применения устройства за счет минимизации числа внешних входов и выходов, требуемых для организации его взаимодействия с другими устройствами коммутационной структуры. Модуль содержит группу блоков буферной памяти, блок сравнения, блок выбора направлений, регистр адреса, регистр данных, регистр приема, три одновибратора, мультиплексор, счетчик, дешифратор, генератор тактовых импульсов, триггер запуска, элемент И, блок буферной памяти, группу регистров, группу демультиплексоров, группу триггеров, группу элементов ИЛИ, четыре элемента ИЛИ, триггер переключения каналов, группу триггеров управления приемом, группу коммутаторов. 7 ил.

Модуль для ретрансляции сообщений в коммутационной структуре, содержащий группу блоков буферной памяти, блок сравнения, блок выбора направлений, регистр адреса, регистр данных, регистр приема, первый, второй и третий одновибраторы, мультиплексор, счетчик, дешифратор, генератор тактовых импульсов, первый, второй и третий элементы ИЛИ, триггер запуска, элемент И, причем информационные выходы блоков буферной памяти группы с первого по восьмой соединены с информационными входами мультиплексора с первого по восьмой соответственно, выход которого соединен с информационными входами регистра адреса и регистра данных, выход регистра адреса соединен с третьим информационным входом блока выбора направлений, выход блока сравнения соединен с вторым информационным входом блока выбора направлений, выходы состояния блоков буферной памяти группы с первого по восьмой соединены с входом первого элемента ИЛИ, выход которого соединен со входами второго и третьего одновибраторов, выход второго одновибратора соединен с входом установки триггера запуска, выходы дешифратора с первого по восьмой соединены с входами опроса блоков буферной памяти группы с первого по восьмой соответственно, выход счетчика соединен с входом дешифратора и адресным входом мультиплексора, выход второго элемента ИЛИ соединен с входом сброса счетчика, вход задания адреса модуля соединен с первым информационным входом блока выбора направлений, отличающийся тем, что в него дополнительно введены блок буферной памяти, группа регистров, группа демультиплексоров, группа триггеров, группа элементов ИЛИ, четвертый элемент ИЛИ, триггер переключения каналов, группа триггеров управления приемом, группа коммутаторов, причем выход первого одновибратора соединен с входом синхронизации блока выбора направлений, старшие разряды информационных входов модуля с первого по восьмой соединены с информационными входами демультиплексоров группы с первого по восьмой соответственно, первые информационные выходы которых соединены с информационными входами соответствующих регистров группы, выходы которых соединены с входом блока сравнения, девятый выход дешифратора соединен с входом опроса блока буферной памяти, первые разряды информационных входов модуля с первого по восьмой соединены со вторыми входами элементов ИЛИ группы с первого по восьмой соответственно, вторые разряды информационных входов модуля с первого по восьмой соединены с первыми входами элементов ИЛИ группы с первого по восьмой соответственно и с входами синхронизации регистров группы с первого по восьмой соответственно, третьи разряды информационных входов модуля с первого по восьмой соединены с входами записи блоков буферной памяти группы с первого по восьмой соответственно, девятый информационный вход модуля соединен с информационным входом блока буферной памяти, вход стробирования модуля соединен с входом записи блока буферной памяти, выход состояния блока буферной памяти соединен с входом первого элемента ИЛИ, информационный выход блока буферной памяти соединен с девятым информационным входом мультиплексора, выходы всех элементов ИЛИ группы соединены со счетными входами соответствующих триггеров управления приемом группы, прямые выходы которых соединены с адресными входами соответствующих демультиплексоров группы, вторые информационные выходы которых соединены с информационными входами блоков буферной памяти группы с первого по восьмой соответственно, выходы коэффициентов загрузки которых соединены с первыми информационными входами коммутаторов группы с первого по восьмой соответственно, прямой выход триггера запуска соединен с входом запуска генератора тактовых импульсов, выход третьего одновибратора соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса триггера запуска, вход сброса модуля соединен с вторым входом третьего элемента ИЛИ, входами сброса триггеров группы, входами сброса регистров группы, входами сброса всех блоков буферной памяти, входом сброса триггера переключения каналов, входом сброса регистра приема, входами сброса регистра адреса и регистра данных, входами сброса всех триггеров управления приемом группы и с первым входом второго элемента ИЛИ, первый выход генератора тактовых импульсов соединен со счетным входом счетчика и с первыми разрядами информационных выходов модуля с первого по восьмой, второй выход генератора тактовых импульсов соединен с входом первого одновибратора, входами синхронизации регистра адреса и регистра данных, с вторым входом четвертого элемента ИЛИ и с вторыми разрядами информационных выходов модуля с первого по восьмой, выход четвертого элемента ИЛИ соединен со счетным входом триггера переключения каналов, третий выход генератора тактовых импульсов соединен со входами синхронизации всех блоков буферной памяти, с первым входом элемента И, с первым входом четвертого элемента ИЛИ, со счетными входами триггеров группы и с третьими разрядами информационных выходов модуля с первого по восьмой, выход элемента И соединен с вторым входом второго элемента ИЛИ, девятый выход дешифратора соединен с вторым входом элемента И, выход коэффициента загрузки блока буферной памяти соединен с десятым информационным выходом модуля, первый и второй информационные выходы блока выбора направлений соединены с входами установки с первого по восьмой и девятого триггеров группы соответственно, прямые выходы которых соединены с третьими управляющими входами коммутаторов группы с первого по восьмой и с входом синхронизации регистра приема соответственно, выходы регистра адреса и регистра данных соединены с вторыми информационными входами коммутаторов группы, выход регистра данных соединен с информационным входом регистра приема, выходы коммутаторов группы с первого по восьмой соединены со старшими разрядами информационных выходов модуля с первого по восьмой соответственно, выход регистра приема соединен с девятым информационным выходом модуля, прямой выход триггера переключения каналов соединен с первыми и вторыми управляющими входами коммутаторов группы с первого по восьмой.

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| US 5151996 А, 29.09.1992. | |||

Авторы

Даты

2004-01-20—Публикация

2002-04-08—Подача