Изобретение относится к импульсной технике и может использоваться в вычислительных устройствах и системах передачи информации.

Известны преобразователи униполярного кода в фазоманипулированный код, содержащие приемник униполярного кода, тактовый генератор, счетный триггер и сумматор по модулю два, входы которого подключены к выходам приемника униполярного и счетного триггера.

Известны преобразователи униполярного кода в код Манчестер-11, содержащие источник входной информации с прямым и инверсным выходами, тактовый генератор с прямым и инверсным выходами, два элемента И и триггер.

Наиболее близок к предлагаемому техническому решению преобразователь униполярного кода в дельта-код в составе известного дельта-сигма-модулятора, содержащий первый и второй элементы ИЛИ, элемент И и IK-триггер, С-вход которого является тактовым входом преобразователя, причем инверсный выход первого элемента ИЛИ соединен с первым входом элемента И I- и К-входами триггера, выход которого подключен к второму входу элемента И, выход которого соединен с входом второго элемента ИЛИ, выход которого является выходом преобразователя.

Известное устройство осуществляет преобразование униполярного кода NRZ 1 по первому информационному входу, соответствующему величине кода положительного знака, и униполярного кода NRZ 2 по второму информационному входу, соответствующему величине кода отрицательного знака.

Целью изобретения является расширение области применения преобразователя за счет формирования дельта-кода из кода "знак" по первому информационному входу и униполярного кода NRZ по второму информационному входу, соответствующему величине входного кода.

Цель достигается тем, что в преобразователь униполярного кода в дельта-код, содержащий первый и второй элементы ИЛИ, элемент И и IK-триггер, С-вход которого является тактовым входом преобразователя, причем инверсный выход первого элемента ИЛИ соединен с первым входом элемента И и I- и К-входами триггера, выход которого подключен к второму входу элемента И, вход второго элемента ИЛИ подключен к выходу элемента И, а выход образует выходную шину преобразователя, введены три элемента И, при этом объединенные первые входы первого и третьего элементов И образуют первый информационный вход преобразователя, первый вход второго элемента И образует второй информационный вход преобразователя, входы первого элемента ИЛИ подключены к выходам первого и второго элементов И, второй вход третьего элемента И подключен к прямому выходу первого элемента ИЛИ, а выход - к второму входу второго элемента ИЛИ, причем второй вход первого элемента И подключен к шине, эквивалентной второму инверсному информационному входу преобразователя, а второй вход второго элемента И подключен к шине, эквивалентной первому инверсному информационному входу преобразователя.

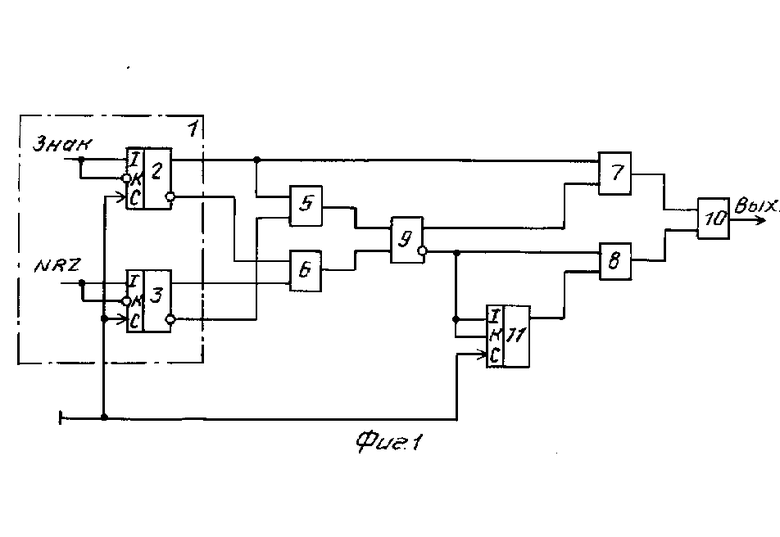

На фиг. 1 представлена функциональная схема преобразователя.

Источником входного кода преобразователя является приемник 1 входного кода, представленный первым 2 и вторым 3 триггерами. Источником тактовых импульсов преобразователя является тактовая шина 4. Преобразователь содержит первый 5, второй 6, третий 7 и четвертый 8 элементы И, первый 9 и второй 10 элементы ИЛИ и триггер 11.

На фиг. 2 представлены временные диаграммы работы преобразователя, где а - физическая величина преобразуемого кода, б - импульсы тактовой частоты на шине 4, в - входной код "знак" по шине знака преобразуемого кода, г - входной униполярный код NRZ по информационной входной шине преобразуемого кода, д - импульсы на прямом выходе первого элемента ИЛИ 9, ж - импульсы на прямом выходе триггера 11, з - выходные импульсы преобразователя на выходе второго элемента ИЛИ 10.

Преобразователь работает следующим образом.

Преобразуемый входной код поступает по шине "знак" на выходе триггера 2, два состояния которого определяют соответствующий знак преобразуемого кода, и по шине униполярного кода типа NRZ, на выходе триггера 3, определяющего величину кода. Источником такого кода может быть, например, аналого-цифровой дельта-сигма-преобразователь. Входной код на выходе триггера 3 представлен прямым униполярным кодом для кода положительного знака и инверсным униполярным кодом для кода отрицательного знака (см. фиг. 2а, в, г). Элемент ИЛИ 9 выполняет функцию неравнозначности сигналов по первому и второму входам преобразователя. Триггер 11 работает в счетном режиме в моменты времени, когда на инверсном выходе элемента ИЛИ 9 появляются сигналы лог. "1", при этом он является делителем на два частоты тактового генератора. В другие моменты времени триггер 11 находится в устойчивом состоянии. Выходной дельта-код на выходе элемента ИЛИ 10 формируется путем логического суммирования импульсов с выходов элементов И 7 и 8. При нулевом входном коде на выход преобразователя поступают импульсы половинной тактовой частоты. При максимальном входном коде положительного знака выходной дельта-код соответствует лог. "0", а при максимальном входном коде отрицательного знака выходной дельта-код соответствует лог. "1". Во всех случаях различных состояний входных триггеров 2 и 3 разность временных интервалов в состояниях лог. "0" и лог. "1" выходного дельта-кода за любой интервал времени пропорциональна величине и знаку входного униполярного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Преобразователь униполярного кода | 1988 |

|

SU1548847A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2029431C1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| Преобразователь кода в суммарный интервал времени | 1983 |

|

SU1106012A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

Изобретение относится к имплуьсной технике и может использоваться в вычислительных устройствах и системах передачи информации. Цель изобретения - расширение области применения. Источником входного кода преобразователя являются выходы блока 1, выполненного на триггерах 2 и 3. Источником тактовых импульсов преобразователя является тактовая шина 4. Преобразователь содержит первый 5, второй 6, третий 7 и четвертый 8 элементы И, первый 9 и второй 10 элементы ИЛИ и JK-триггер 11. Преобразуемый входной код представлен шиной "знак" на выходе триггера 2, два состояния которого определяют соответствующий знак преобразуемого кода, и второй шиной униполярного кода NRZ на выходе триггера 3, состояния которого определяют величину кода. При максимальном входном коде положительного знака выходной дельта-код соответствует лог. "0", а при максимальном входном коде отрицательного знака выходной дельта-код соответствует лог. "1". При нулевом входном коде на ыходе преобразователя присутствуют импульсы половинной частоты тактового генератора. Во всех случаях различных состояний входных триггеров 2 и 3 разность временных интервалов в состоянии лог. "0" и лог. "1" выходного дельта-кода за любой интервал времени пропорциональна величине и знаку входного униполярного кода. 2 ил.

ПРЕОБРАЗОВАТЕЛЬ УНИПОЛЯРНОГО КОДА В ДЕЛЬТА-КОД, содержащий первый и второй элементы ИЛИ, элемент И и JK-триггер, C-вход которого является тактовой шиной, инверсный выход первого элемента ИЛИ соединен с первым входом элемента И и J- и K-входами JK-триггера, выход которого подключен к второму входу элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является выходной шиной, отличающийся тем, что, с целью расширения области применения за счет повышения информативности выходных параметров, в него введены дополнительные первый, второй и третий элементы И, первые входы первого и третьего из которых объединены и являются первой входной шиной знака преобразуемого кода, первый вход второго элемента И является первой информационной входной шиной преобразуемого кода, входы первого элемента ИЛИ подключены к выходам первого и второго элементов И, второй вход третьего элемента И подключен к прямому выходу первого элемента ИЛИ, а выход - к второму входу второго элемента ИЛИ, причем второй вход первого элемента И является второй информационной входной шиной преобразуемого кода, а второй вход второго элемента И является второй входной шиной знака преобразуемого кода.

Авторы

Даты

1994-04-30—Публикация

1990-05-11—Подача