Изобретение относится к импульсной технике и может найти применение в цифровых системах передачи.

Известен преобразователь кода, содержащий блоки памяти, счетчики, элементы И, элементы НЕ, блоки сравнения, генераторы кодовых слов, триггеры и блок управления декодированием [1].

Недостаток известного преобразователя кода состоит в значительной сложности его конструкции.

Наиболее близким по технической сущности к предлагаемому преобразователю кода является преобразователь кода, содержащий регистр, подключенный выходом второго разряда к выходной шине, первый триггер, соединенный инверсным выходом с первым входом первого элемента И, второй триггер, подключенный прямым выходом к первому входу второго элемента И, третий триггер, соединенный прямым выходом с первым входом третьего элемента И, формирователь импульсов, четвертый, пятый и шестой элементы И, перевый и второй элементы НЕ, входную шину информации, входную шину тактовых импульсов и входную шину начальной установки [2].

Недостаток такого преобразователя кода состоит в том, что он не позволяет обеспечить требуемое быстродействие. Известный преобразователь кода не позволяет также обеспечить достаточно высокую помехоустойчивость, преобразование заданного кода, достаточно высокую достоверность преобразованного кода и потребляет значительное количество энергии для обеспечения достаточно высокого быстродействия.

Целью изобретения является повышение быстродействия преобразователя кода.

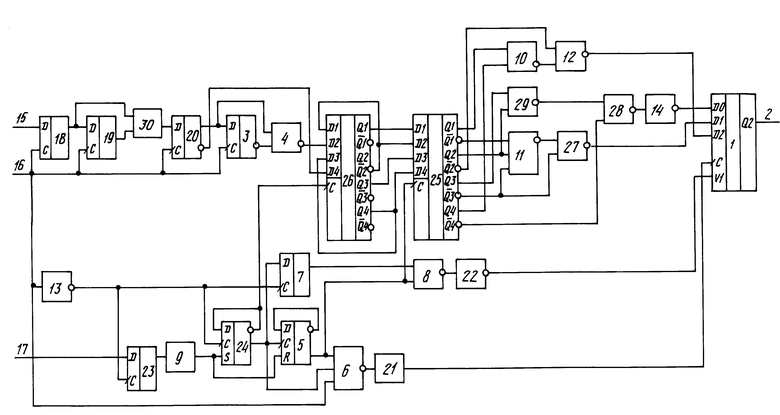

На чертеже изображен один из возможных вариантов предлагаемого преобразователя кода.

Преобразователь кода содержит регистр 1, выходную шину 2, четвертый триггер 3, первый элемент И-НЕ 4, девятый триггер 5, восьмой элемент И-НЕ 6, десятый триггер 7, девятый элемент И-НЕ 8, формирователь 9 импульсов, четвертый, пятый и третий элементы И-НЕ 10, 11 и 12, второй и первый элементы НЕ 13 и 14, входную информационную шину 15, входную шину 16 тактовых импульсов и входную шину 17 начальной установки. Преобразователь кода содержит также первый, второй и третий триггеры 18, 19 и 20, селектор 21 тактовой частоты, третий элемент НЕ 22, седьмой, восьмой, шестой и пятый триггеры 23, 24, 25 и 26, седьмой, шестой и четвертый элементы И 27, 28 и 29 и сумматор 30 по модулю два.

Работает преобразователь кода следующим образом.

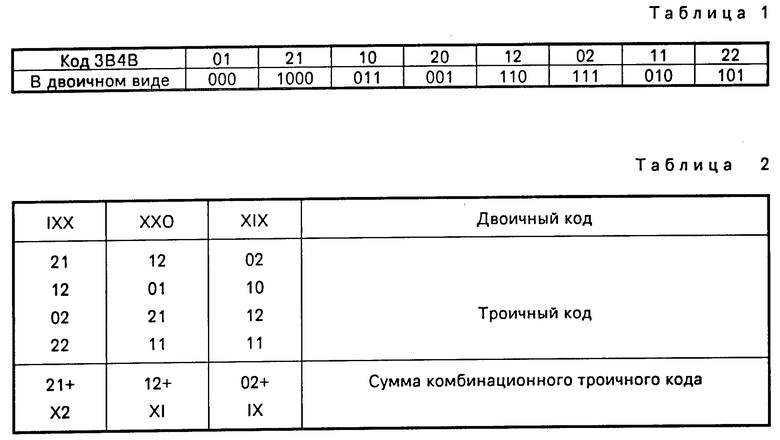

Преобразователь обеспечивает преобразование сигнала в коде 3В4В с частотой 22, 912 МГц в унитарный двоичный сигнал с частотой 17, 184 МГц. Декодирование входного рабочего сигнала происходит в соответствии с табл.1, в которой "0", "1" и "2" троичного сигнала (в коде 3В4В) описаны в табл.2.

Входной информационный сигнал, представляющий собой сигнал в коде 3В4В с частотой 22, 912 МГц, поступает по шине 15 на информационный вход триггера 18, воздействующего на информационный вход триггера 19. Сигналы с прямых выходов триггеров 18 и 19 подаются на сумматор 30 по модулю два, вырабатывающий информацию о переходах уровня от логического "0" к уровню логической "1" и наоборот во входном информационном сигнале. С выхода сумматора 30 по модулю два сигнал поступает на триггер 20, воздействующий на триггер 3. С прямого выхода триггера 20 и с инверсного выхода триггера 3 сигналы подаются на элемент И 4, выделяющий информацию о троичных двойках. С выхода элемента И 4 и с инверсного выхода триггера 20 сигналы поступают соответственно на соответствующие информационные входы триггера 26. На вход синхронизации триггера 26 поступает сигнал с инверсного выхода триггера 24, производящего деление на два сигнала тактовой частоты 22,912 МГц, проходящего с шины 16 тактовых импульсов через элемент НЕ 13. При этом на триггер 24 поступает также установочный импульс, формируемый триггером 23 и формирователем 9 импульсов из сигнала начальной установки, подаваемого на шину 17 начальной установки. Этот установочный импульс производит установку триггера 5, который обеспечивает деление на четыре частоты 22, 921 МГц. При этом на триггере 26 обеспечивается задержка на два такта входных сигналов. На прямых выходах третьего и четвертого разрядов триггера 26 формируется информация о троичных "1", а на прямом выходе первого разряда и на инверсном выходе второго разряда формируется информация о троичных "2". Информация с триггера 26 перезаписывается в триггер 25 с деленной на четыре частотой 22,912 МГц. При этом триггер 25 формирует информацию о двух троичных тактах. На прямом выходе четвертого разряда триггера 25 собирается (Х1), на прямом выходе третьего разряда - (1Х), на прямом выходе второго разряда - (Х2)3, а на прямом выходе первого разряда - (2Х)3, Х, 0, 1 или 2 в троичном коде. На инверсном выходе элемента И-НЕ 10 собираются комбинации (2Х)2 и (Х1)3, т.е. (21)3, а на элементе И-НЕ 12 - (21)3 и (Х2)3, что по табл.1 и 2 соответствует 1ХХ в двоичном коде. На инверсном выходе элемента И 29 собираются комбинации (1Х)3 и (Х2)3, что по табл.1 и 2 соответствует ХХ0 в двоичном коде.

На элементе И-НЕ 11 собираются (2Х)3, (Х2)3, (1Х), т.е. (02)3. На элементе И 27 собираются комбинации (02)3 и (1Х)3, что соответствует Х1Х в двоичном коде: ( ), ( )3 - символ троичного кода.

Сигналы с выхода элемента НЕ 14 и с инверсных выходов элементов И 27, И-НЕ 12 поступают на соответствующие информационные входы регистра 1. На управляющий вход регистра 1 с выхода элемента НЕ 22 поступает сигнал, который является результатом умножения двух частот: деленной на два частоты 22,912 МГц и деленной на четыре частоты 22,912 МГц. На вход синхронизации регистра 1 подается сигнал тактовой частоты 17,184 МГц с выхода селектора 21 тактовой частоты. С прямого выхода разряда регистра 1 на шину 2 поступает декодированный сигнал, если положительный фронт сигнала тактовой частоты приходится на середину управляющего импульса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2029431C1 |

| УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2013015C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ | 1992 |

|

RU2047870C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1990 |

|

RU2007882C1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1992 |

|

RU2029357C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 1990 |

|

RU2009617C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИИМПУЛЬСНОГО СИГНАЛА | 1992 |

|

RU2048706C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА | 1991 |

|

RU2010428C1 |

| Преобразователь кода | 1990 |

|

SU1757103A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

Изобретение относится к импульсной технике и может найти применение в цифровых системах передачи. Целью изобретения является повышение быстродействия преобразования кода. С этой целью в преобразователь кода введены дополнительные триггеры 3, 7, 23 - 26, селектор 21 тактовой частоты, дополнительный элемент НЕ 22, элементы И-НЕ 4, 6, 8, 10 - 12, и 27, 28, сумматор 30 по модулю два и формирователь 9 импульсов наряду с основными триггерами 18 - 20, основными элементами НЕ 13, 14 и регистром 1. 2 табл., 1 ил.

ПРЕОБРАЗОВАТЕЛЬ КОДА, содержащий первый триггер, информационный вход которого подключен к информационной входной шине, второй и третий триггеры, регистр, выход которого подключен к информационной выходной шине преобразователя, первый и второй элементы НЕ, отличающийся тем, что, с целью повышения быстродействия преобразователя, в него введены формирователь импульсов, селектор тактовой частоты, четвертый - десятый триггеры, элементы И - НЕ, третий элемент НЕ и сумматор по модулю два, прямой выход первого триггера соединен с первым входом сумматора по модулю два и информационным входом второго триггера, прямой выход которого соединен с вторым входом сумматора по модулю два, выход которого соединен с информационным входом третьего триггера, прямой выход третьего триггера соединен с первым входом первого элемента И - НЕ и информационным входом четвертого триггера, инверсный выход которого соединен с вторым входом первого элемента И - НЕ, выход которого и инверсный выход третьего триггера соединены соответственно с первым и вторым информационными входами пятого триггера, прямые выходы первого и третьего разрядов которого соединены с одноименными информационными входами шестого триггера, инверсные выходы второго и четвертого разрядов пятого триггера соединены соответственно с вторыми информационными входами пятого и шестого триггеров и третьим информационным входом пятого триггера и четвертым информационным входом шестого триггера, прямые выходы первого и четвертого разрядов шестого триггера соединены соответственно с первым и вторым входами второго элемента И - НЕ, инверсный выход которого соединен с первым входом третьего элемента И - НЕ, прямые выходы второго и третьего разрядов шестого триггера соединены соответственно с первыми входами четвертого и пятого элементов И - НЕ и вторым входом четвертого элемента И - НЕ, выход которого соединен с первым входом шестого элемента И - НЕ, инверсный выход первого разряда шестого триггера соединен с вторым входом пятого элемента И - НЕ, выход которого соединен с первым входом седьмого элемента И - НЕ, инверсный выход второго разряда шестого триггера соединен с вторым входом третьего элемента И - НЕ, инверсный выход третьего разряда шестого триггера соединен с третьим входом пятого элемента И - НЕ и вторым входом седьмого элемента И - НЕ, инверсный выход четвертого разряда шестого триггера соединен с вторым входом шестого элемента И - НЕ, выход которого соединен через первый элемент НЕ с первым информационным входом регистра, выходы седьмого и третьего элементов И - НЕ соединены соответственно с вторым и третьим информационными входами регистра, выход седьмого триггера через формирователь импульсов соединен с входом установки единицы восьмого триггера и входом установки нуля девятого триггера, инверсный выход которого соединен с его информационным входом, прямой выход девятого триггера соединен с синхронизирующим входом шестого триггера и первыми входами восьмого и девятого элементов И - НЕ, выходы которого соединены соответственно через селектор тактовой частоты и третий элемент НЕ с синхронизирующим и управляющим входами регистра, инверсный выход восьмого триггера соединен с его информационным входом и с синхронизирующим входом пятого триггера, прямой выход восьмого триггера соединен с вторым входом восьмого элемента И - НЕ, синхронизирующим входом девятого триггера и информационным входом десятого триггера, прямой выход которого соединен с вторым входом девятого элемента И - НЕ, выход второго элемента НЕ соединен с синхронизирующими входами седьмого, восьмого и десятого триггеров, вход второго элемента И, третий вход восьмого элемента И - НЕ и синхронизирующие входы первого - четвертого триггеров подключены к тактовой шине преобразователя, информационный вход седьмого триггера подключен к шине начальной установки преобразователя.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1462485A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-10-30—Публикация

1990-10-01—Подача