Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин и устройств дискретной автоматики.

Известен преобразователь кодов, содержащий группу последовательно соединенных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, способный формировать на выходах "пачки" единиц и нулей [1] .

Недостатком указанного устройства является невозможность подсчета количества единиц во входном поле с выдачей результата в параллельном коде.

Известен также преобразователь кодов, содержащий группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и группу элементов И [2] , способный кроме формирования "пачек" единиц и нулей формировать код с чередованием единичных значений входного кода. Этому устройству также присущ указанный выше недостаток.

Целью изобретения является расширение функциональных возможностей за счет обеспечения однотактной операции подсчета количества единиц во входном коде с выдачей результата в параллельном коде.

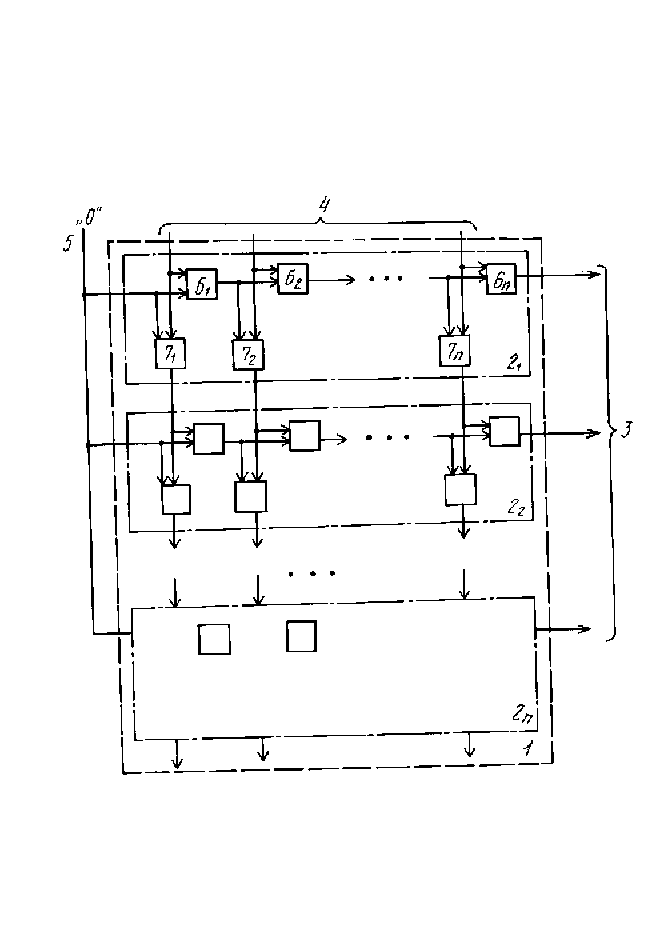

На чертеже представлена функциональная схема преобразователя с выдачей числа единиц в параллельном коде.

Преобразователь кодов выполнен в виде матрицы 1 итеративной сети, состоящей из 1 + log2n строк 2, и содержит параллельные выходы 3, информативные входы 4 и управляющий вход 5. Каждая строка 21. . . 2n содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 61. . . 6n и элементов И 71. . . 7n, выходы которых образуют выход кода с чередованием единиц преобразования кодов.

Преобразователь работает следующим образом.

Если на управляющий вход 5 подать "0", то этот "0" сохраняется на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 61. . . 6n в строках 21. . . 2n, пока на выходы каждой строки 21. . . 2n поступают нули. Если на какой-либо входной разряд поступает значение "1", то на выходе соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 61. . . 6n строки 21. . . 2n вырабатывается значение "1", которое сохраняется до встречи следующей единицы на входах строки 21. . . 2n, после чего происходит инвертирование значения, вырабатываемого элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 61. . . 6n строки 21. . . 2n, причем на выходах элементов И группы каждой строки 21. . . 2n присутствуют "1" только в позициях, соответствующих для первой строки 21 четным по порядку единицами входного кода, т. е. выполняется операция деления на два, при этом остаток в виде "1" для нечетного числа единиц или "0" для четного числа единиц поступает на выход 3 в соответствующей строке 21. . . 2n, при этом в первой строке 21 отображается младший разряд единичного разложения числа единиц и соответственно в 2i-й строке - 2i-й разряд, равный коэффициенту при 2(i-1)-множителе в двоичном разложении числа единиц. Например, если исходный код содержит пять единиц, то на выходе 3 первой строки 21 будет "1", а на входы второй строки 22 поступает код, содержащий две единицы. Тогда на выходе 3 второй строки 22 будет "0", а на входы третьей строки 23 поступает код, содержащий одну "1". На выходе третьей строки 23 будет "1", а на входах всех последующих строк 34. . . 3n - чистые нули, что влечет на выходах 3 этих строк 34. . . 3n наличие "0". Таким образом, на выходах 3 будет (log2 n+1)-значный код 000. . . 0101, что равно двоичному представлению числа пять. При этом код результата образуется в итоге срабатывания комбинационной схемы параллельно.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЗИЦИОННЫХ СУММАТОРОВ ПО МОДУЛЮ | 2002 |

|

RU2231823C2 |

| ДВУХПОРОГОВЫЙ КОМПАРАТОР ДИАПАЗОНА ДВОИЧНЫХ БИТ | 2020 |

|

RU2758205C1 |

| РАНГОВЫЙ ФИЛЬТР | 2002 |

|

RU2205449C1 |

| ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ АНАЛОГОВЫХ СИГНАЛОВ | 1994 |

|

RU2093888C1 |

| КРУГОВОЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2022 |

|

RU2785771C1 |

| Адаптивный мажоритарный блок элементов "n и более из (2n-1)" | 2023 |

|

RU2818031C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| Устройство для подсчета количества единиц в двоичном числе | 1990 |

|

SU1795455A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении цифровых вычислительных машин и устройств дискретной автоматики. Целью изобретения является расширение функциональных возможностей за счет обеспечения однотактовой операции подсчета количества единиц во входном коде с выдачей результата в параллельном коде. Преобразователь кодов выполнен в виде матрицы 1 итеративной сети, состоящей из 1+log2n строк 2, каждая из которых выполнена в виде групп элементов И 71...7n и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 61...6n и содержит управляющий вход 5, информационные входы 4 и выходы 3 числа единиц во входном коде. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ КОДОВ, содержащий первую группу элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы i-х элементов которых объединены и являются i-м входом преобразователя кодов, выход последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом первой группы элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход i-го элемента последнего из которых соединен с вторыми входами i + 1 элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ и вторые входы первых элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и являются управляющим входом преобразователя кодов, выходы элементов И первой группы образуют выход кода с чередованием единичных значений, отличающийся тем, что в преобразователь кода дополнительно введены log2n аналогичных групп элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элементов И, которые образуют выход кода с чередованием единичных значений i-й группы элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, соединены с входами элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (i + 1)-й группы элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых log2n групп объединены между собой и подключены к управляющему входу преобразователя, выходы последних элементов ИСКЛЮЧАЮЩЕЕ ИЛИ log2n групп элементов И и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют выход числа единиц во входном коде.

Авторы

Даты

1994-04-30—Публикация

1991-01-09—Подача