Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах для контроля достоверности выполнения арифметических операций.

Известно устройство (аналог) (а.с. СССР №1242961, МКИ G 06 F 11/10, БИ №25, 1986 г.), содержащее дешифратор, счетчик, группы сумматоров по модулю 2, группу триггеров, группу элементов ИЛИ, триггеры, регистры сдвига, генератор тактовых импульсов. Недостаток устройства - низкое быстродействие контроля достоверности выполнения арифметических операций в сумматорах.

Известно также устройство (аналог) (а.с. СССР №1310826, МКИ G 06 F 11/10, БИ №18, 1987 г.), содержащее блоки свертки по модулю три, вычитатель, сдвигатели, сумматор по модулю три, сумматоры по модулю два, позиционный сумматор и коммутаторы, мультиплексоры, элемент И. Недостаток устройства - низкое быстродействие контроля достоверности выполнения арифметических операций в сумматорах.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является устройство [1, с. 292], содержащее сумматор остатков, схемы вычисления остатков, схему сравнения.

Недостаток прототипа - низкое быстродействие, так как для реализации контроля по модулю в нем требуется время 2τ лэ] log2N [, ограниченное временем переключения логических элементов τ лэ, где ] • [ - символ округления в большую сторону до ближайшего целого; N - разрядность двоичного позиционного кода.

Задача, на решение которой направлено заявляемое устройство, состоит в повышении производительности перспективных образцов вычислительной техники.

Технический результат выражается в повышении быстродействия выполнения контроля арифметических операций.

Технический результат достигается тем, что в устройство, содержащее схему сравнения, выход которой является выходом устройства, введены три группы управляемых фазовращателей, генератор гармонического сигнала и фазовый детектор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя первой группы управляемых фазовращателей и первым входом первого управляемого фазовращателя третьей группы управляемых фазовращателей, при этом в каждой группе управляемых фазовращателей выход r-го управляемого фазовращателя соединен с первым входом (r+1)-го управляемого фазовращателя  выход N-го управляемого фазовращателя первой группы управляемых фазовращателей соединен с первым входом первого управляемого фазовращателя второй группы управляемых фазовращателей, при этом выход N-го управляемого фазовращателя второй группы управляемых фазовращателей соединен с первым входом фазового детектора, выход N-го управляемого фазовращателя третьей группы управляемых фазовращателей - со вторым входом фазового детектора, выход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключено эталонное напряжение, причем i-е разряды первого и второго операндов сложения

выход N-го управляемого фазовращателя первой группы управляемых фазовращателей соединен с первым входом первого управляемого фазовращателя второй группы управляемых фазовращателей, при этом выход N-го управляемого фазовращателя второй группы управляемых фазовращателей соединен с первым входом фазового детектора, выход N-го управляемого фазовращателя третьей группы управляемых фазовращателей - со вторым входом фазового детектора, выход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключено эталонное напряжение, причем i-е разряды первого и второго операндов сложения  соединены соответственно со вторыми входами i-х управляемых фазовращателей первой и второй группы управляемых фазовращателей, а i-й разряд результата арифметической операции сложения, выполненной в позиционном сумматоре, соединен со вторым входом i-го управляемого фазовращателя третьей группы управляемых фазовращателей.

соединены соответственно со вторыми входами i-х управляемых фазовращателей первой и второй группы управляемых фазовращателей, а i-й разряд результата арифметической операции сложения, выполненной в позиционном сумматоре, соединен со вторым входом i-го управляемого фазовращателя третьей группы управляемых фазовращателей.

Сущность изобретения основывается на использовании при реализации операции модульного сложения чисел свойства периодичности гармонической функции.

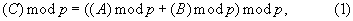

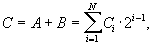

В заявляемом устройстве используется контроль по модулю, основанный на известных из теории чисел [1, с. 291-292] свойствах вычетов, сущность которого состоит в сравнении вычета результата арифметической операции, выполненной в позиционном коде, с результатом той же арифметической операции по модулю, осуществленной над вычетами операндов. При этом решение о правильном выполнении арифметической операции принимается в том случае, если

где А, В - операнды в позиционном коде; С - результат выполнения арифметической операции в позиционном коде, С=А+В; р - целое положительное число.

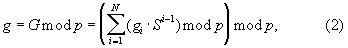

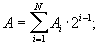

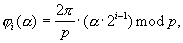

В общем случае, получение вычета g числа G осуществляется путем суммирования по модулю вычетов разрядов позиционного кода этого числа [2, с. 198, формула (7.21)]:

где gi - значение i-го разряда N - разрядного позиционного кода числа G; S - основание позиционной системы счисления (ПСС). Для двоичной ПСС: S=2.

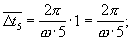

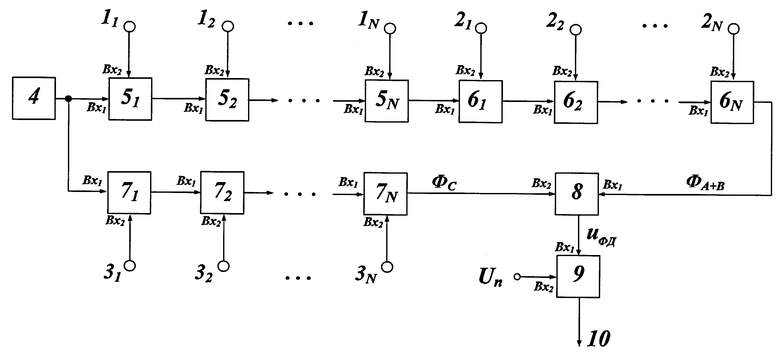

Рассмотрим принципы реализации контроля выполнения операции сложения в позиционном двоичном N-разрядном сумматоре с помощью заявляемого устройства. Устройство контроля позиционных сумматоров по модулю, как показано на фиг.1, включает в свой состав генератор гармонического радиосигнала 4, две параллельные ветви последовательно соединенных управляемых фазовращателей 51-5N, 61-6N и 71-7N, фазовый детектор 8 и схему сравнения 9 с эталонным напряжением Un. В управляемых фазовращателях этого устройства устанавливаются сдвиги фазы ϕ i(Ai), ϕ i(Bi) и ϕ i(Ci),  прямо пропорциональные значениям двоичных разрядов Аi, Bi,

прямо пропорциональные значениям двоичных разрядов Аi, Bi,  позиционных кодов чисел

позиционных кодов чисел

и

и

где

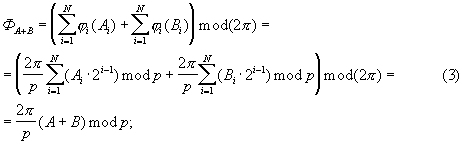

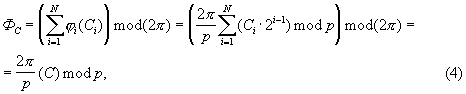

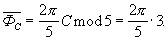

Тогда учитывая периодичность гармонической функции, суммарные сдвиги фазы сигналов на выходах управляемых фазовращателей 6N и 7N относительно фазы радиосигнала на выходе генератора гармонического сигнала соответственно будут равны

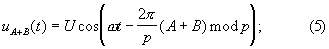

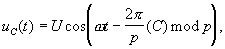

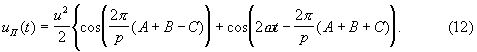

а соответствующие радиосигналы на входах фазового детектора могут быть представлены в следующем виде:

где U - амплитуда радиосигнала, ω - частота радиосигнала. В случае если в ходе сложения операндов А и В в позиционном сумматоре произойдет сбой, изменивший вычет результата на q(q=((A+B)mod p-(C)mod p)mod p), на выходе фазового детектора установится напряжение, прямо пропорциональное  которое после сравнения с эталонным напряжением Un является основанием для принятия решения об ошибочном выполнении арифметической операции.

которое после сравнения с эталонным напряжением Un является основанием для принятия решения об ошибочном выполнении арифметической операции.

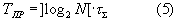

Как отмечалось выше, сложение N чисел в прототипе происходит за ]log2N[ тактов. Число тактов вытекает из формулы (2) при условии, что сумматор остатков реализует двухместную операцию сложения по модулю. Следовательно, время выполнения модульной операции в прототипе составляет

где τ Σ - суммарное время переключения цифровых логических схем в табличном вычислителе.

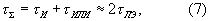

Основу узла, выполняющего операцию сложения по модулю р в табличном вычислителе прототипа, составляет матричный дешифратор [3, с.16-17], построенный на двухвходовых элементах И, расположенных в местах пересечений р горизонтальных и р вертикальных входных шин. Выходы элементов И подключены ко входу соответствующих элементов ИЛИ, число которых равно р. Таким образом, сигнал от входа к выходу в табличном вычислителе проходит через 2 логических элемента - И и ИЛИ. Поэтому

где τ лэ - время переключения логического элемента (И, ИЛИ).

Как показано в [2, с.173], время τ лэ ≈ 10-10 с является практическим пределом для логических элементов на транзисторах, которое достигается только при жидкостном охлаждении до криогенных температур.

Поэтому минимальное время выполнения модульной операции в прототипе на основании (6) и (7) составляет

ТПР ≈ 2·10-10.]log2N[, с.

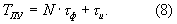

Время выполнения модульной операции в предлагаемом устройстве (Тпу) на основании вышеизложенного равно сумме времени задержки гармонического сигнала в N управляемых фазовращателях [N·τ ф), и времени интегрирования в интеграторе фазового детектора (τ u)

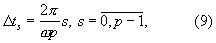

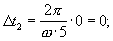

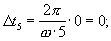

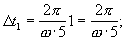

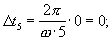

Необходимые для реализации устройства сложения N чисел по модулю р N последовательно соединенных фазовращателей должны быть управляемыми и могут быть выполнены на основе различных схемных решений. Например, в СВЧ диапазоне [4, с.102] такой фазовращатель наиболее просто реализовать на основе линий задержки (ЛЗ) на время

где ω - несущая частота гармонического сигнала.

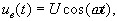

Действительно, если на входе ЛЗ на время Δ ts (9) действует гармонический сигнал

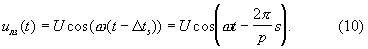

то на выходе ЛЗ с учетом (9) будет сигнал

Следовательно, подключая линию задержки в соответствии с позиционным кодом операнда s, можно получить значение фазового сдвига в управляемом фазовращателе, прямо пропорциональное величине этого операнда.

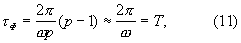

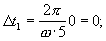

Максимальное время задержки в управляемом фазовращателе на ЛЗ, с учетом (9), будет равно

где

f - частота гармонического сигнала, Гц.

Алгоритм работы фазового детектора заключается в перемножении гармонического сигнала, снимаемого с выхода управляемого фазовращателя 6N, с сигналом, снимаемым с выхода управляемого фазовращателя 7N, и интегрировании результата перемножения. Результат перемножения гармонического сигнала с выхода управляемого фазовращателя 6N с сигналом с выхода управляемого фазовращателя 7N можно записать в виде:

После интегрирования uП(t) в интеграторе фазового детектора, получим

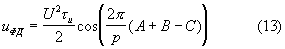

Для расчета возьмем значение τ u=3Т.

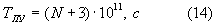

Таким образом, с учетом (8)-(10}:

ТПУ=NT+3T=T(N+3)

Уже сейчас на практике реализованы вплоть до 100... 150 ГГц типовые радиотехнические элементы (в том числе и в интегральном исполнении), из которых состоят управляемые фазовращатели и фазовый детектор.

Следовательно, при f=100 ГГц=1011 Гц

Например, при N=10 из (6) и (11) получим

ТПР ≈ 6·10-10;

ТПУ ≈ 1,3·10-10.

Таким образом, предлагаемое устройство для контроля позиционных сумматоров по модулю позволяет значительно сократить полные временные затраты на выполнение контроля арифметической операции по сравнению с прототипом и может найти применение при проектировании процессоров перспективных ЭВМ.

На фиг.1 представлена структурная схема предлагаемого устройства, где 11-1N - информационные входы устройства (операнд А), 21-2N - информационные входы устройства (операнд В), 31-3N - информационные входы устройства (результат арифметической операции С=А+В), 4 - генератор гармонического сигнала, 51-5N, 61-6N, 71-7N - группы управляемых фазовращателей, 8 - фазовый детектор, 9 - схема сравнения, 10 - выход устройства.

Информационные входы 11-1N соединены со вторыми входами управляемых фазовращателей первой группы управляемых фазовращателей 51-5N, информационные входы 21-2N соединены со вторыми входами управляемых фазовращателей второй группы управляемых фазовращателей 61-6N, а информационные входы 31-3N соединены со вторыми входами управляемых фазовращателей третьей группы управляемых фазовращателей 71-7N, при этом выход генератора гармонического сигнала 4 соединен с первым входом управляемого фазовращателя 51 и с первым входом управляемого фазовращателя 71, выход управляемого фазовращателя ki с первым входом управляемого фазовращателя k(i+1) (k=5, 6, 7)  выход управляемого фазовращателя 5N соединен с первым входом управляемого фазовращателя 61, выход управляемого фазовращателя 6N с первым входом фазового детектора 8, а выход управляемого фазовращателя 7N соединен со вторым входом фазового детектора, причем выход фазового детектора 8 соединен с первым входом схемы сравнения 9, ко второму входу которого подключено эталонное напряжение Un, при этом выход схемы сравнения 9 является выходом 10 устройства.

выход управляемого фазовращателя 5N соединен с первым входом управляемого фазовращателя 61, выход управляемого фазовращателя 6N с первым входом фазового детектора 8, а выход управляемого фазовращателя 7N соединен со вторым входом фазового детектора, причем выход фазового детектора 8 соединен с первым входом схемы сравнения 9, ко второму входу которого подключено эталонное напряжение Un, при этом выход схемы сравнения 9 является выходом 10 устройства.

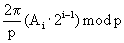

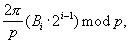

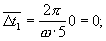

Рассмотрим работу предлагаемого устройства. На N информационных входов 11-1N устройства поступает двоичный позиционный код числа А, разряды которого равны  В соответствии со значением i-х разрядов числа A, поступающих на Вх2 соответствующих управляемых фазовращателей первой группы управляемых фазовращателей 51-5N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные

В соответствии со значением i-х разрядов числа A, поступающих на Вх2 соответствующих управляемых фазовращателей первой группы управляемых фазовращателей 51-5N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные  при

при  На N информационных входов 21-2N устройства поступает двоичный позиционный код числа В, разряды которого равны

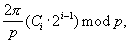

На N информационных входов 21-2N устройства поступает двоичный позиционный код числа В, разряды которого равны  В соответствии со значением i-х разрядов числа В, поступающих на Вх2 соответствующих управляемых фазовращателей второй группы управляемых фазовращателей 61-6N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные

В соответствии со значением i-х разрядов числа В, поступающих на Вх2 соответствующих управляемых фазовращателей второй группы управляемых фазовращателей 61-6N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные  при

при  На N информационных входов 31-3N устройства поступает двоичный позиционный код числа С=А+В, разряды которого равны

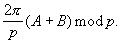

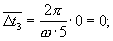

На N информационных входов 31-3N устройства поступает двоичный позиционный код числа С=А+В, разряды которого равны  В соответствии со значением i-х разрядов числа С, поступающих на Вх2 соответствующих управляемых фазовращателей третьей группы управляемых фазовращателей 71-7N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные

В соответствии со значением i-х разрядов числа С, поступающих на Вх2 соответствующих управляемых фазовращателей третьей группы управляемых фазовращателей 71-7N, в них, путем подключения коммутаторами соответствующей линии задержки, устанавливаются набеги фазы, равные  при

при  После прохождения гармонического сигнала с выхода генератора гармонического сигнала 4 последовательно через первую и вторую группы управляемых фазовращателей 51-5N и 61-6N, в соответствии с выражением (3), на выходе фазовращателя 6N суммарный набег фаз этого сигнала будет равен

После прохождения гармонического сигнала с выхода генератора гармонического сигнала 4 последовательно через первую и вторую группы управляемых фазовращателей 51-5N и 61-6N, в соответствии с выражением (3), на выходе фазовращателя 6N суммарный набег фаз этого сигнала будет равен  После прохождения гармонического сигнала с выхода генератора гармонического сигнала 4 через третью группу управляемых фазовращателей 71-7N в соответствии с выражением (4) на выходе фазовращателя 7N суммарный набег фаз этого сигнала будет равен

После прохождения гармонического сигнала с выхода генератора гармонического сигнала 4 через третью группу управляемых фазовращателей 71-7N в соответствии с выражением (4) на выходе фазовращателя 7N суммарный набег фаз этого сигнала будет равен

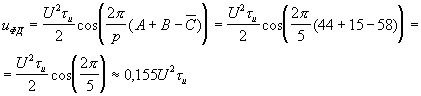

В фазовом детекторе 8 происходит сравнение фазы сигнала с выхода управляемого фазовращателя 6N, поступающего на Bx2 фазового детектора 8, с фазой гармонического сигнала, поступающего с выхода управляемого фазовращателя 7N на Вx2 фазового детектора 8. При этом из выражения (13) видно, что максимальное напряжение uФД на выходе фазового детектора 8 будет тогда, когда фазы сигналов совпадут. После сравнения напряжения uФД в схеме сравнения 9 с эталонным напряжением Un, результат сравнения поступает на выход 10 устройства.

Пример

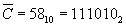

Пусть р=5, А=4410=1011002, В=1510=0011112 C=5910=1110112, N=6. Тогда:

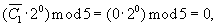

(A1·20)mod5=(0·20)mod5=0,

(A2·21)mod5=(0·21)mod5=0,

(A3·22)mod5=(1·22)mod5=4,

(A4·23)mod5=(1·23)mod5=3,

(A5·24)mod5=(0·24)mod5=0,

(A6·25)mod5=(1·25)mod5=2.

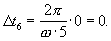

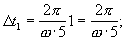

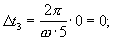

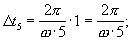

В управляемых фазовращателях 51-56 соответствующими коммутаторами подключаются линии задержки на время, которое согласно (9) равно:

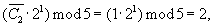

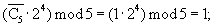

(B1·20)mod5=(1·20)mod5=1,

(B2·21)mod5=(1·21)mod5=2,

(B3·22)mod5=(1·22)mod5=4,

(B4·23)mod5=(1·23)mod5=3,

(B5·24)mod5=(0·24)mod5=0,

(B6·25)mod5=(0·25)mod5=0.

В управляемых фазовращателях 61-66 соответствующими коммутаторами подключаются линии задержки на время, равное:

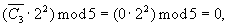

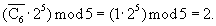

(C1·20)mod5=(1·20)mod5=1,

(C2·21)mod5=(1·21)mod5=2,

(C3·22)mod5=(0·22)mod5=0,

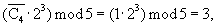

(C4·23)mod5=(1·23)mod5=3,

(C5·24)mod5=(1·24)mod5=1,

(C6·25)mod5=(1·25)mod5=2.

В управляемых фазовращателях 71-76 соответствующими коммутаторами подключаются линии задержки на время, равное:

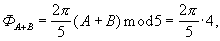

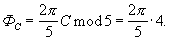

После прохождения гармонического сигнала с выхода генератора 4 последовательно через первую и вторую группы управляемых фазовращателей 51-56 и 61-66 на выходе фазовращателя 66 фаза сигнала ФA+B в соответствии с (3) будет равна  а после прохождения через третью группу фазовращателей 71-76 в соответствии с (4) фаза сигнала ФC будет равна:

а после прохождения через третью группу фазовращателей 71-76 в соответствии с (4) фаза сигнала ФC будет равна:  .

.

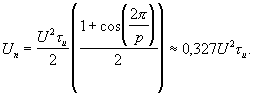

Следует отметить, что величина эталонного напряжения Un принимается равной

Тогда, поскольку uФД>Un, то на выходе схемы сравнения 9 вырабатывается сигнал о достоверности выполнения арифметической операции сложения в позиционном сумматоре.

Исходя из (13) напряжение uФД на выходе фазового детектора 8 при условии равенства фаз ФA+B=ФC будет максимальным (uФД ≈ 0,5U2τ

Пусть в сумматоре произошел сбой, изменивший правильный результат 44+15=59 на  Тогда

Тогда

В управляемых фазовращателях 71-76 соответствующими коммутаторами подключаются линии задержки на время, равное:

После прохождения гармонического сигнала с выхода генератора 4 через третью группу фазовращателей 71-76 в соответствии с (3) фаза гармонического сигнала  будет равна:

будет равна:

Напряжение uФД на выходе фазового детектора 8 согласно (13) будет равно:

Напряжение uФД сравнивается в схеме сравнения 9 с эталонным напряжением Un=0,327U2τ

Источники информации

1. Микропроцессоры: в 3 кн. Кн. 2: Средства сопряжения. Контролирующие и информационно-управляющие системы: Учеб. для техн. вузов / В.Д.Вернер, Н.В.Воробьев, А.В.Горячев и др.; Под ред. Л.Н.Преснухина. - Мн.: Выш. шк., 1987. - 303 с.

2. Акаев А.А., Майоров С.А. Оптические методы обработки информации. - М.: Высш. шк., 1988, 237 с.

3. Долгов А.И. Диагностика устройств, функционирующих в системе остаточных классов. - М.: Радио и связь, 1982, 64 с.

4. Радиоприемные устройства: Учеб. пособие для радиотехнич. спец. вызов / Ю.Т.Давыдов, Ю.С.Данилич. - М.: Высш. шк., 1989, 342 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| ФОРМИРОВАТЕЛЬ ПЕРИОДИЧЕСКИХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2003 |

|

RU2271602C2 |

| СИНТЕЗАТОР ЧАСТОТЫ | 2002 |

|

RU2237972C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2237274C2 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2006 |

|

RU2313124C1 |

| ПАРАЛЛЕЛЬНЫЙ АСИНХРОННЫЙ СУММАТОР | 1994 |

|

RU2097826C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах для контроля достоверности выполнения арифметических операций. Техническим результатом является повышение быстродействия. Устройство содержит генератор гармонического сигнала, три группы управляемых фазовращателей, фазовый детектор, схему сравнения. 1 ил.

Устройство для контроля позиционных сумматоров по модулю, содержащее схему сравнения, выход которой является выходом устройства, отличающееся тем, что в него введены три группы управляемых фазовращателей, генератор гармонического сигнала и фазовый детектор, причем выход генератора гармонического сигнала соединен с первым входом первого управляемого фазовращателя первой группы управляемых фазовращателей и первым входом первого управляемого фазовращателя третьей группы управляемых фазовращателей, при этом в каждой группе управляемых фазовращателей выход r-го управляемого фазовращателя соединен с первым входом (r+1)-го управляемого фазовращателя  выход N-го управляемого фазовращателя первой группы управляемых фазовращателей соединен с первым входом первого управляемого фазовращателя второй группы управляемых фазовращателей, при этом выход N-го управляемого фазовращателя второй группы управляемых фазовращателей соединен с первым входом фазового детектора, выход N-го управляемого фазовращателя третьей группы управляемых фазовращателей - со вторым входом фазового детектора, выход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключено эталонное напряжение, причем i-e разряды первого и второго операндов сложения

выход N-го управляемого фазовращателя первой группы управляемых фазовращателей соединен с первым входом первого управляемого фазовращателя второй группы управляемых фазовращателей, при этом выход N-го управляемого фазовращателя второй группы управляемых фазовращателей соединен с первым входом фазового детектора, выход N-го управляемого фазовращателя третьей группы управляемых фазовращателей - со вторым входом фазового детектора, выход которого соединен с первым входом схемы сравнения, а ко второму входу схемы сравнения подключено эталонное напряжение, причем i-e разряды первого и второго операндов сложения  соединены соответственно со вторыми входами i-х управляемых фазовращателей первой и второй группы управляемых фазовращателей, а i-й разряд результата арифметической операции сложения, выполненное в позиционном сумматоре, соединен со вторым входом i-го управляемого фазовращателя третьей группы управляемых фазовращателей.

соединены соответственно со вторыми входами i-х управляемых фазовращателей первой и второй группы управляемых фазовращателей, а i-й разряд результата арифметической операции сложения, выполненное в позиционном сумматоре, соединен со вторым входом i-го управляемого фазовращателя третьей группы управляемых фазовращателей.

| Микропроцессоры | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Средства сопряжения | |||

| Контролирующие и информационно-управляющие системы | |||

| ВЕРНЕР В.Д., ВОРОБЬЕВ Н.В., ГОРЯЧЕВ А.В | |||

| и др | |||

| Под ред | |||

| Л.Н.ПРЕСНУХИНА - М.: Высшая школа, 1987, с.292 | |||

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2024924C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ | 1992 |

|

RU2006912C1 |

| Устройство для контроля сумматоров | 1983 |

|

SU1242961A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| US 5121397 А, 09.06.1992 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

2004-06-27—Публикация

2002-08-20—Подача