Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единичных сигналов (см., например, фиг.1 в описании изобретения к патенту GB 2365636, кл. G 06 F 7/60, 2002 г.), которые формируют двоичный код числа единичных сигналов входного кортежа (х1, х2, х3), хi∈{0, 1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единичных сигналов, относятся ограниченные функциональные возможности, поскольку не допускается обработка кортежа (х1, ..., хn).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип параллельный счетчик единичных сигналов (см. рис.2 в статье: Новиков Л.Г. Преобразователи синхронного унитарного импульсного сигнала. // Приборы и системы. Управление, контроль, диагностика. 2002. №8. С.34-35), который содержит элемент «И», элемент «исключающее ИЛИ» и формирует двоичный код числа единичных сигналов входного кортежа (х1, ..., x7), хi∈{0, 1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, поскольку не допускается обработка кортежа (х1, ..., хn).

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода числа единичных сигналов входного кортежа (х1, ..., хn), хi∈{0, 1}.

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единичных сигналов, содержащем по одному элементу «И» и «исключающее ИЛИ», особенность заключается в том, что в него введены n-1 элементов «И», n-1 элементов «исключающее ИЛИ» и 2n D-триггеров, причем первый, второй входы i-го  элемента «исключающее ИЛИ» и тактовый вход (n+i)-го D-триггера соединены соответственно с выходом i-го элемента «И», входом данных и тактовым входом i-го D-триггера, подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу i-го элемента «И», первому и второму управляющим входам параллельного счетчика единичных сигналов, i-й информационный вход и k-й (

элемента «исключающее ИЛИ» и тактовый вход (n+i)-го D-триггера соединены соответственно с выходом i-го элемента «И», входом данных и тактовым входом i-го D-триггера, подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу i-го элемента «И», первому и второму управляющим входам параллельного счетчика единичных сигналов, i-й информационный вход и k-й ( , где [·] есть оператор выделения целой части) выход которого образованы соответственно первым входом i-го элемента «И» и неинвертирующим выходом (n+2k-1)-го D-триггера, выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход первого элемента «исключающее ИЛИ» - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с (n+1)-го, D-триггера подключен к неинвертирующему выходу последующего D-триггера, а вход данных 2n-го D-триггера соединен с выходом n-го элемента «исключающее ИЛИ».

, где [·] есть оператор выделения целой части) выход которого образованы соответственно первым входом i-го элемента «И» и неинвертирующим выходом (n+2k-1)-го D-триггера, выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход первого элемента «исключающее ИЛИ» - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с (n+1)-го, D-триггера подключен к неинвертирующему выходу последующего D-триггера, а вход данных 2n-го D-триггера соединен с выходом n-го элемента «исключающее ИЛИ».

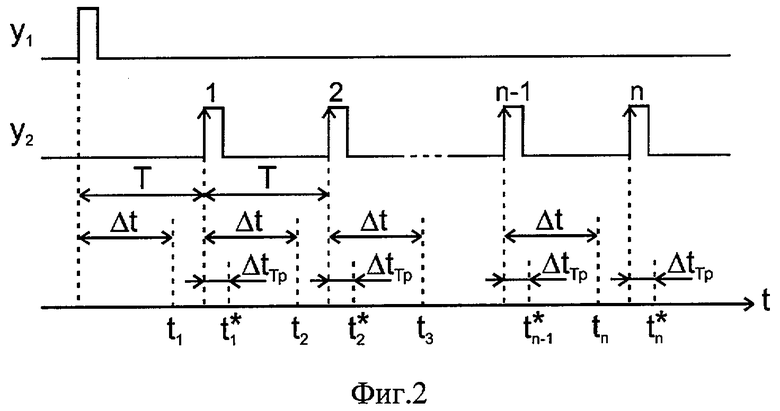

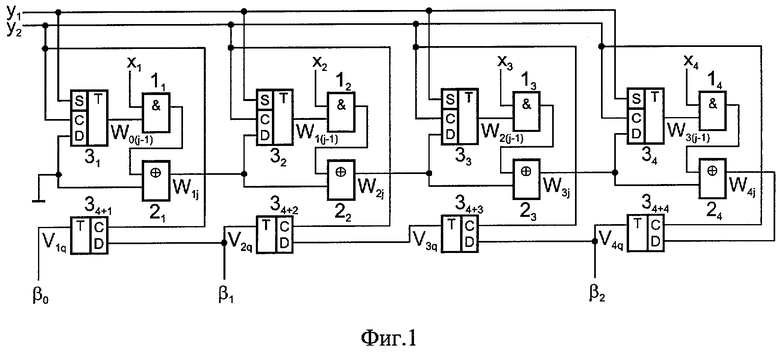

На фиг.1 и 2 представлены соответственно схема предлагаемого параллельного счетчика единичных сигналов (например, при n=4) и временные диаграммы, поясняющие принцип его работы.

Параллельный счетчик единичных сигналов содержит элементы «И» 11, ..., 1n, элементы «исключающее ИЛИ» 21, ..., 2n, D-триггеры 31, ..., 32n, причем первый, второй входы элемента 2i и тактовый вход D-триггера 3n+i соединены соответственно с выходом элемента 1i входом данных и тактовым входом D-триггера 3i подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу элемента 1i, первому и второму управляющим входам параллельного счетчика единичных сигналов, i-ый информационный вход и k-ый (

и тактовый вход D-триггера 3n+i соединены соответственно с выходом элемента 1i входом данных и тактовым входом D-триггера 3i подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу элемента 1i, первому и второму управляющим входам параллельного счетчика единичных сигналов, i-ый информационный вход и k-ый ( , где [·] есть оператор выделения целой части) выход которого образованы соответственно первым входом элемента 1i и неинвертирующим выходом D-триггера

, где [·] есть оператор выделения целой части) выход которого образованы соответственно первым входом элемента 1i и неинвертирующим выходом D-триггера  , выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход элемента 21 - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с 3n+i D-триггера, подключен к неинвертирующему выходу последующего D-триггера, а вход данных D-триггера 32n соединен с выходом элемента 2n.

, выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход элемента 21 - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с 3n+i D-триггера, подключен к неинвертирующему выходу последующего D-триггера, а вход данных D-триггера 32n соединен с выходом элемента 2n.

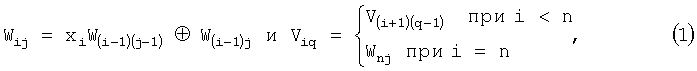

Работа предлагаемого параллельного счетчика единичных сигналов осуществляется следующим образом. На его первый, ..., n-ый информационные и первый, второй управляющие входы подаются соответственно двоичные сигналы x1, ..., xn∈{0, 1} и импульсные сигналы у1, у2∈{0,1} (фиг.2), причем период T сигнала у2 должен удовлетворять условию Т>Δt, где Δt=ΔtТр+ΔtИ+nΔtиск или, а ΔtТр, ΔtИ и Δtиск или есть длительности задержек, вносимых соответственно D-триггером, элементом «И» и элементом «исключающее ИЛИ». Тогда сигналы на выходе элемента 2i и неинвертирующем выходе D-триггера 3n+1 будут определяться рекуррентными выражениями

и неинвертирующем выходе D-триггера 3n+1 будут определяться рекуррентными выражениями

где  и q=j есть номера моментов времени tj и t* q соответственно (фиг.2); W(i-1)0=1; W0j=0; V20=...=Vn0=Θ; (Θ - неопределенное значение сигнала). В представленной ниже таблице приведены значения выражений (1) при n=4.

и q=j есть номера моментов времени tj и t* q соответственно (фиг.2); W(i-1)0=1; W0j=0; V20=...=Vn0=Θ; (Θ - неопределенное значение сигнала). В представленной ниже таблице приведены значения выражений (1) при n=4.

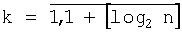

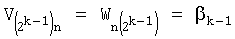

Таким образом, на k-ом ( , где [·] есть оператор выделения целой части) выходе предлагаемого параллельного счетчика единичных сигналов при q=n имеем

, где [·] есть оператор выделения целой части) выходе предлагаемого параллельного счетчика единичных сигналов при q=n имеем  , где β[log2n]...β1β0 есть двоичный код числа единичных сигналов входного кортежа (х1, ..., хn).

, где β[log2n]...β1β0 есть двоичный код числа единичных сигналов входного кортежа (х1, ..., хn).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единичных сигналов обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает формирование двоичного кода числа единичных сигналов входного кортежа (х1, ..., xn,), Xi∈{0, 1}.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260836C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2277260C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2284567C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2012 |

|

RU2504826C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2353967C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2011 |

|

RU2445679C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| СИММЕТРИЧНЫЙ МОДУЛЬ | 2003 |

|

RU2248035C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Технический результат заключается в расширении функциональных возможностей за счет обеспечения формирования двоичного кода числа единичных сигналов входного кортежа (x1, ..., xn), xi∈{0, 1}. В счетчик, содержащий по одному элементу «И» (1) и «исключающее ИЛИ» (2), введены n-1 элементов «И» (1), n-1 элементов «исключающее ИЛИ» (2) и 2n D-триггеров (3). 2 ил., 1 табл.

Параллельный счетчик единичных сигналов, содержащий по одному элементу «И» и «исключающее ИЛИ», отличающийся тем, что в него введены n-1 элементов «И», n-1 элементов «исключающее ИЛИ» и 2n D-триггеров, причем первый, второй входы i-го  элемента «исключающее ИЛИ» и тактовый вход (n+i)-го D-триггера соединены соответственно с выходом i-го элемента «И», входом данных и тактовым входом i-го D-триггера, подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу i-го элемента «И», первому и второму управляющим входам параллельного счетчика единичных сигналов, i-ый информационный вход и k-ый

элемента «исключающее ИЛИ» и тактовый вход (n+i)-го D-триггера соединены соответственно с выходом i-го элемента «И», входом данных и тактовым входом i-го D-триггера, подключенного неинвертирующим выходом, входом установки и тактовым входом соответственно к второму входу i-го элемента «И», первому и второму управляющим входам параллельного счетчика единичных сигналов, i-ый информационный вход и k-ый  где [·] есть оператор выделения целой части) выход которого образован соответственно первым входом i-го элемента «И» и неинвертирующим выходом (n+2k-1)-го D-триггера, выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход первого элемента «исключающее ИЛИ» - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с (n+1)-го D-триггера, подключен к неинвертирующему выходу последующего D-триггера, а вход данных 2n-го D-триггера соединен с выходом n-го элемента «исключающее ИЛИ».

где [·] есть оператор выделения целой части) выход которого образован соответственно первым входом i-го элемента «И» и неинвертирующим выходом (n+2k-1)-го D-триггера, выход каждого предыдущего элемента «исключающее ИЛИ» соединен с вторым входом последующего элемента «исключающее ИЛИ», а второй вход первого элемента «исключающее ИЛИ» - с шиной нулевого потенциала, вход данных каждого предыдущего, начиная с (n+1)-го D-триггера, подключен к неинвертирующему выходу последующего D-триггера, а вход данных 2n-го D-триггера соединен с выходом n-го элемента «исключающее ИЛИ».

| НОВИКОВ Л.Г | |||

| Преобразователи синхронного унитарного импульсного сигнала | |||

| В книге "Приборы и системы | |||

| Управление, контроль, диагностика" | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1971 |

|

SU428558A1 |

| СПОСОБ ПРОИЗВОДСТВА ГОРЯЧЕКАТАНОЙ ТОНКОЛИСТОВОЙ СТАЛИ | 2008 |

|

RU2365636C1 |

| СПОСОБ УСИЛЕНИЯ ЖЕЛЕЗОБЕТОННОЙ МНОГОПУСТОТНОЙ ПАНЕЛИ ПЕРЕКРЫТИЯ ЗДАНИЯ | 2009 |

|

RU2398944C1 |

| US 3898444, 05.08.1975. | |||

Авторы

Даты

2006-09-27—Публикация

2005-04-15—Подача