Изобретение относится к бионике и вычислительной технике и может быть использовано в качестве элемента нейроподобных сетей при моделировании нейрофизиологических процессов в нервной системе, в устройствах обработки, анализа и распознавания образов, в системах управления интеллектуальными работами, в цифровых нейрокомпьютерах.

Известны устройства (авт. св. СССР N 682910, кл. G 01 G 7/60, 1979; авт. св. СССР N 767788, кл. 1980), содержащие n блоков изменения синаптических весов, сумматор и пять цифровых интеграторов.

Недостатком этих устройств являются их недостаточные функциональные возможности, не позволяющие моделировать адаптивные нейроны.

Известно также устройство (авт. св. СССР N 736130, кл. G 06 G 7/60, 1980), содержащее n блоков моделирования синапса, адаптивный сумматор, три сумматора, блок сравнения и десять цифровых интеграторов. Устройство обладает более широкими функциональными возможностями и позволяет, в частности, моделировать адаптивные нейроны, но имеет высокую аппаратурную сложность.

Наиболее близким по технической сущности к заявляемому является устройство для моделирования адаптивного нейрона (авт.св. СССР N 708369, кл. G 06 G 7/60, 1980), содержащее блок суммирования синаптических весов, первые n входов которого являются входами устройства, причем выход блока суммирования синаптических весов соединен с входом переменной интегрирования первого цифрового интегратора, выход которого подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, вход подынтегральной функции которого подключен к выходу первого сумматора, выход которого подключен к первому входу второго сумматора, выход которого соединен с входом подынтегральной функции четвертого цифрового интегратора, выход которого подключен к входу блока сравнения, выход которого является выходом устройства и соединен с входом переменной интегрирования пятого цифрового интегратора, выход которого подключен к первому входу третьего сумматора, второй вход которого соединен с выходом шестого цифрового интегратора, вход переменной интегрирования которого соединен с выходом седьмого цифрового интегратора, вход подынтегральной функции которого подключен к прямому выходу третьего сумматора, инверсный выход которого соединен с вторым входом второго сумматора, выход восьмого цифрового интегратора подключен к третьему входу сумматора, четверый вход которого соединен с выходом девятого цифрового интегратора, вход переменной интегрирования которого подключен к выходу третьего цифрового интегратора, входы переменной интегрирования третьего, четвертого, седьмого и восьмого цифровых интеграторов подключены к одному управляющему входу устройства, вторые n выходов блока суммирования синаптических весов и входы подынтегральной функции первого, второго, пятого, шестого, восьмого и девятого цифровых интеграторов соединены с другими управляющими входами устройства соответственно.

Недостатками прототипа являются недостаточно широкие функциональные возможности, не позволяющие использовать его для моделирования различных известных моделей нейронов, их функциональных узлов и ансамблей, а также высокая аппаратурная сложность, затрудняющая применение современной микроэлектронной технологии. Действительно каждый цифровой интегратор в своей минимальной конфигурации (работающий по формуле прямоугольников) содержит два сумматора, два регистра, умножитель и квантователь. Учитывая, что блок суммирования синаптических весов на n входов в прототипе также реализуется на цифровых интеграторах (по одному интегратору на каждый вход), можно считать, что аппаратурные затраты на реализацию прототипа ориентировочно составляют 2(n+9)+4 сумматоров, 2(n+9) регистров, n+9 умножителей, n+9 квантователей и один блок сравнения. Такой уровень сложности не позволяет при современном состоянии микроэлектронной технологии реализовать прототип в виде большой интегральной схемы, а следовательно, делает невозможным построение моделирующей нейроподобной сети или параллельного нейрокомпьютера, достаточной для практических целей размерности 103-102элементов.

Целью изобретения является расширение функциональных возможностей и упрощение устройства.

Цель достигается тем, что в устройство, содержащее блок изменения синаптических весов (в прототипе - блок суммирования синаптических весов), первые n входов которого являются основными информационными входами устройства, а вторые n входов - установочными входами, введены n/m (m<n, n>12, m>2) сумматоров, n/m выходных блоков, коммутатор и блок адресации, причем третьи n входов блока изменения синаптических весов являются дополнительными информационными входами устройства, а n/m выходов частичных сумм подключены соответственно к первым входам каждого из n/m сумматоров, вторые m входов каждого из которых подключены соответственно к первой группе из n выходов коммутатора, выходы всех n/m сумматоров подключены к входам соответствующих n/m выходных блоков, к первой группе из n/m входов коммутатора и являются первой группой из n/m выходов устройства, первые, вторые и третьи выходы всех выходных блоков подключены соответственно к второй, третьей и четвертой группам из n/m входов коммутатора и являются соответственно второй, третьей и четвертой группами из n/m выходов устройства, а четвертые выходы всех выходных блоков подключены к третьим одиночным входам соответствующих сумматоров, вторая и третья группы из n выходов коммутатора подключены соответственно к n основным и n дополнительным информационным входам устройства, а адресные входы коммутатора подключены к выходам блока адресации, каждый выходной блок содержит первый и второй элементы И, первые входы которых соединены и являются входом выходного блока, первый и второй регистры, входы которых подключены соответственно к выходам первого и второго элементов И, и логический блок, входы которого подключены к выходам второго элемента И и второго регистра, которые наряду с выходами логического блока и первого регистра являются соответственно первым, вторым, третьим и четвертым выходами выходного блока.

Наличие отличительных признаков: n/m сумматоров, n/m выходных блоков, коммутатора и блока адресации с указанными выше связями обуславливает соответствие заявляемого технического решения критерию "новизна". Заявляемое техническое решение соответствует также критерию "существенные отличия", поскольку не обнаружено решений с признаками, сходными с признаками, отличающими заявляемое техническое решение от прототипа.

Возможность достижения цели изобретения - расширение функциональных возможностей и упрощение устройства - обуславливается наличием перечисленных отличительных существенных признаков предлагаемого технического решения. Действительно, изменяя с помощью блока адресации программу настройки коммутатора предлагаемого устройства можно, в частности, воспроизводить формально-логические модели нейронов, градуальные модели нейронов, динамические модели неадаптивных нейронов, динамические адаптивные модели нейронов с адаптацией либо по входу, либо по выходу, либо и по входу и по выходу одновременно, пространственный сумматор на n входов, вычислители скалярного произведения, цифровые интеграторы.

Заявляемое устройство, кроме того, проще прототипа. Так, при m=2, что уже достаточно для реализации всех перечисленных выше функций, оно содержит n+n/2 сумматоров, 2n+2 регистров (блок адресации - это, по существу, два адресных регистра), n умножителей, n триггеров, 3n элементов типа И(ИЛИ), один коммутатор. Полагая, например, n=12, получают для прототипа 46 сумматоров, 42 регистра, 21 умножитель, 21 квантователь, один блок сравнения, для заявляемого устройства 18 сумматоров, 26 регистров, 12 умножителей, 12 триггеров, 36 элементов типа И(ИЛИ), один коммутатор.

Наличие существенных отличительных признаков предлагаемого технического решения позволяет, расширив функциональные возможности прототипа, одновременно упростить его и тем самым достичь цели изобретения.

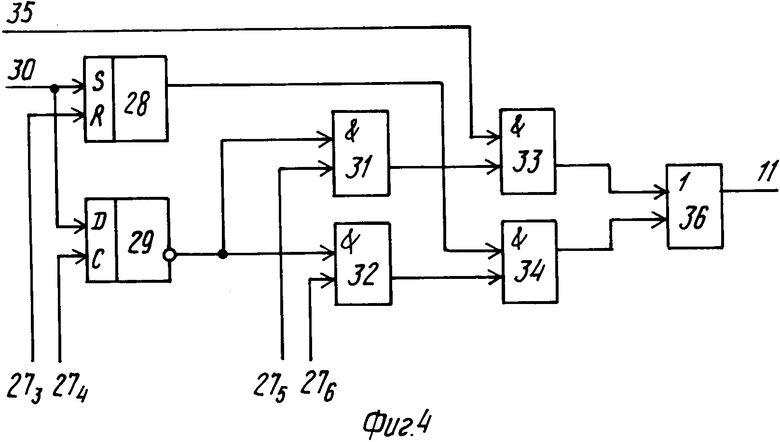

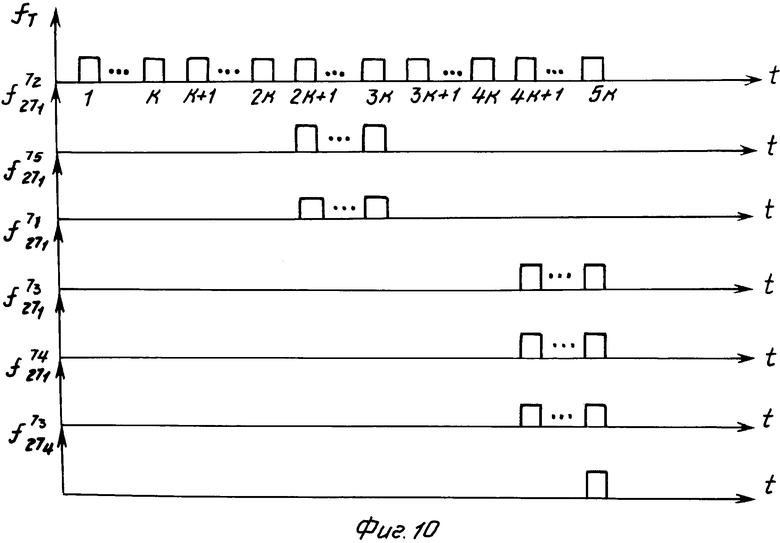

На фиг. 1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока изменения синаптических весов; на фиг.3 - структурно-функциональная схема выходного блока; на фиг.4 - функциональная схема логического блока; на фиг.5 - структурно-функциональная схема коммутатора и блока адресации.

Устройство для моделирования нейронов (фиг.1) содержит блок 1 изменения синаптических весов, который имеет n основных информационных входов 21, 22, . . . , 2n, n дополнительных информационных входов 31,32,...,3n и n установочных входов 41,42,...,4n. Выходы частичных сумм по m слагаемых каждая этого блока подключены к входам 51,52,...,5n/mкомбинационных сумматоров 61, 62, ...,6n/m. Выходы сумматоров 61,62,...,6n/m подключены к входам выходных блоков 71, 72. ..,7n/m и являются первой группой из n/m выходов 81,82,..., 8n/m устройства. Выходные блоки 71,72,...,7n/m имеют выходы 91,92,...,9n/m, 101, 102, ...,10n/m, 111,112,...,11n/m, которые составляют вторую, третью и четвертую группы из n/m выходов устройства и, кроме того, вместе с группой выходов 81, 82, . . .,8n/m подключены к одноименным входам коммутатора 12. Сумматоры 61,62,...,6n/m имеют группы по m входов 1311,1312,...,131m,1321, 1322, . . . , 132m, 13n/m1, 13n/m2,..., 13n/mm, которые подключены к одноименным выходам коммутатора 12, а также одиночные входы 141,142,...,14n/m, которые подключены к соответствующим выходам 151,152,...,15n/m выходных блоков 71, 72,...,7n/m. Основные 21,22,...,2n и дополнительные 31,32,...,3n входы устройства подключены также к одноименным выходам коммутатора 12. Адресные входы 161 и 162коммутатора 12 подключены к выходам блока 17 адресации.

Блок 1 изменения синаптических весов (фиг.2) состоит из n однотипных ячеек, каждая из которых содержит последовательно соединенные регистр 18 сдвига, сумматор 19 и умножитель 20. Выход сумматора 19 подключен к входу регистра 18 сдвига. Вторые входы умножителей 20 и сумматоров 19 составляют соответственно основные 21,22,...,2n и дополнительные 31,32,...,3n информационные входы устройства, а вторые входы регистров 18 сдвига - установочные входы 41,42,...,4n устройства. Выходы умножителей 20 по m объединяются на сумматорах 21, выходы которых являются выходами 51,52,...,5n/m частичны сумм блока изменения синаптических весов.

Выходной блок 7 (фиг.3) содержит элементы И 22, 23, первые входы которых соединены и являются входом блока 7, регистры 24, 25 сдвига, входы которых подключены к выходам элементов И 22, 23 соответственно логический блок 26, входы которого подключены к выходам элемента И 22 и регистра 24 сдвига. Вторые входы элементов И 22, 23, а также третий, четвертый, пятый и шестой входы логического блока 26 являются управляющими входами 27 устройства. Выходы элемента И 22, регистра 24 сдвига, логического блока 26 и регистра 25 сдвига являются соответственно выходами 9, 10, 11 и 15 выходного блока 7 и всего устройства.

Логический блок 26 (фиг.4) содержит триггеры 28, 29, первые входы которых соединены и являются первым входом 30 логического блока 26, который подключен к выходу элемента И 22, элементы И 31, 32, первые входы которых подключены к инверсному выходу триггера 29, элементы И 33, 34, первые входы которых подключены соответственно к выходам элементов И 31, 32, при этом второй вход элемента И 33 является вторым входом 35 логического блока 26 и подключен к выходу регистра 24 сдвига, а второй вход элемента И 34 подключен к прямому выходу триггера 28, элемент ИЛИ 36, входы которого подключены к выходам элементов И 33, 34, а выход является выходом логического блока 26 и третьим выходом 11 выходного блока 7 и всего устройства. Вторые входы триггеров 28, 29 и элементов И 31, 32 являются соответственно управляющими входами 273, 274, 275, 276логического блока 26.

Коммутатор 12 (фиг. 5) содержит матрицу 37 триггерных ключей, входы выборки которых по ося Х и Y подключены к выходам адресных дешифраторов 381, 382. Входы дешифраторов 381, 382 подключены к разрядным выходам адресных регистров 391, 392, составляющих, по существу, блок 17 адресации устройства. Информационные входы коммутатора подключены к матрице 37 триггерных ключей. Информационные выходы коммутатора 12 через буферный регистр 40 подключены к информационным выходам матрицы 37. Коммутатор 12 имеет также вход 41 управления записью программы коммутации и вход 42 управления выдачей информации. Коммутатор может быть выполнен на серийной микросхеме К1801ВП1.

Перед началом работы устройства осуществляется сброс в нулевое состояние регистров 181,...,18n и регистров умножителей 201,...,20nблока 1 изменения синаптических весов (фиг.1 и 2), регистров 24, 25 выходного блока 7 (фиг. 1 и 3), триггеров 28, 29 логического блока 26 выходного блока 7 (фиг. 1, 3 и 4), адресных регистров 391,392 блока 17 адресации (фиг.1 и 5) и буферного регистра 40 коммутатора 12 (фиг.1 и 5). После этого осуществляется настройка устройства на выбранный режим работы. Для этого в адресные регистры 391, 392 блока 17 адресации записывается требуемый код коммутации. Коммутатор 12 имеет 3n выходов и 4n/m входов, подключенных соответственно к информационным входам и через буферный регистр 40 к информационным выходам матрицы 37 триггерных ключей. Иными словами матрица триггерных ключей коммутатора имеет размерность 3nx4n/m. Чтобы образовать требуемый канал связи между i-м информационным входом и j-м информационным выходом матрицы 37 коммутатора 12, в регистры 391 и 392 записываются соответствующие коды коммутации, под действием которых на выходах дешифраторов 381 и 382появляются единичные сигналы, переводящие в единичное состояние триггерный ключ, стоящий на пересечении j-й строки и i-го столбца матрицы 37. Размерность кодов коммутации и, следовательно, разрядность регистров 391 и 392 соответственно log23n и log24n/m. Последовательно осуществляя описанным выше способом построение требуемых каналов связи, реализуют необходимую систему коммутации между информационными входами и выходами матрицы 37 триггерных ключей коммутатора 12. После задания требуемой системы коммутации в коммутаторе осуществляется настройка логических блоков 26 выходных блоков 71, . . .,7n/m (путем подачи единичного или нулевого сигнала на управляющие входы 275,276) на выполнение функций sign Pi, max{0,Pi} или отключение этих блоков, а затем запис в соответствующие регистры 181,...,18n блока изменения синаптических весов параметров реализуемых моделей нейрона. После этого устройство готово к работе.

Рассмотрим процесс настройки и работу устройства для различных режимов функционирования.

Режим работы 1: n/m формально-логических моделей нейрона на m входов каждая. В этом режиме устройство реализует ансамбль n/m не связанных между собой формально-логических нейронов на m входов каждый. При таком режиме не требуется устанавливать каналы связи между входами и выходами коммутатора 12, поэтому в регистрах 391 и 392 коммутатора хранятся нулевые коды коммутации, сформированные в них на этапе сброса всех регистров устройства в нулевое состояние. На управляющие входы 275, 276 логического блока 26 каждого выходного блока 71, . ..,7n/m подаются соответственно нулевой и единичный потенциалы, настраивающие их на выполнение функции sign Pi. Затем в регистры 181,...,18n через установочные входы 41,...,4n блока 1 изменения синаптических весов записываются начальные значения синаптических весов γ i1,..., γinmмоделей нейронa: синаптические веса γi1,..., γim для каждой из n/m моделей нейрона. После этого устройство готово к приему входных сигналов Хi1, ...Xim в каждую из n/m моделей нейрона через информационные входы 21,...,2n устройства. Работает устройство в соответствии с временной диаграммой, представленной на фиг.6. В течение первых k тактов времени осуществляются прием через основные информационные входы 21,...,2nустройства k-разрядных двоичных кодов входных сигналов Хi1,...,Xin в регистры умножителей 201, 20n блока 1 изменения синаптических весов (фиг.1 и 2) и одновременно выдача из регистров 24 через информационные выходы 111,...,11n/m выходных блоков 71,. . . , 7n/m k-разрядных двоичных кодов выходных сигналов увыхi каждой из n/m моделей нейрона. При необходимости в эти же первые k тактов времени через дополнительные информационные входы 31,...,3n могут поступать k-разрядные двоичные коды приращений Δγi4,... Δγin синаптических весов и суммироваться на сумматорах 191,...,19n блока изменения синаптических весов (фиг.1 и 2) с синаптическими весами γi-1,1,... γi-1,n, полученными на предыдущем (i-1)-м шаге работы устройства. После этого в течение последующих 2k тактов времени осуществляются умножение в умножителях 201,...,20nвходных сигналов Хi1,..., Xin на синаптические веса γi1,..., γin и затем суммирование в сумматорах 211, . ..,21n/m полученных 2k-разрядных произведений (по m произведений для каждой из n/m моделей нейрона). Полученные n/m сумм произведений с выходов блока 1 изменения синаптических весов поступают на входы 51,...,5n/m сумматоров 61,...6n/m, проходят через эти сумматоры и появляются на их выходах. Таким образом, в течение рассматриваемых 2k тактов времени на выходе каждого из сумматоров 61,...,6n/m формируется 2k-разрядный двоичный код числа

Pi= Xijγij

Xijγij

Как видно из временной диаграммы на фиг.6, под действием управляющего сигнала f271 (поступающего на управляющий вход 271 каждого выходного блока 71, ...,7n/m) старшие k разрядов (вместе со знаком) каждого из n/m чисел Pi через элементы И 22 (фиг.3) записываются в регистры 24 выходных блоков 71,. ..,7n/m. При этом перед поступлением k старших разрядов числа Pi осуществляется сброс в нулевое состояние триггеров 28 логических блоков 26 каждого выходного блока 71,...,7n/mпутем подачи в любом из k+1,...,2k (на фиг.6 в (k+1)-м такте) тактах времени управляющего сигнала f273 на управляющие входы 273 логических блоков 26 каждого выходного блока 71,...,7n/m, а в момент поступления самого старшего (знакового) разряда каждого числа Pi на управляющий вход 274 логического блока 26 каждого выходного блока 71,...,7n/m подается единичный сигнал f274 (фиг.6), под действием которого в триггер 29 логического блока 26 каждого выходного блока 71,...,7n/m записывается значение знакового разряда соответствующего числа Pi: триггер 29 переходит в состояние "1", если Pi<0, и в состояние "0", если Pi ≥ 0. Если число Pi<0, то элемент И 32 логического блока 26 каждого выходного блока 71,..., 7n/m закрыт и на выходе 11 каждого выходного блока 71,...,7n/m в течение последующих k тактов времени формируется нулевой сигнал. Если Pi=0 (т.е. среди значащих разрядов нет ни одной "1"), то триггеры 28, 29 логического блока 26 каждого выходного блока 71,...,7n/mнаходятся в нулевом состоянии элемент И 32 открыт, но элемент И 34 закрыт) и на выходе 11 каждого выходного блока 71,...,7n/m также сформирован двоичный k-разрядный код нуля. Когда Pi>0, то триггер 28 переходит в единичное состояние, элементы И 32 и 34 открыты и на выходе 11 каждого выходного блока 71,...,7n/m в течение k тактов времени формируется единичный сигнал. Таким образом, при данном режиме работы устройство реализует работу ансамбля из n/m не связанных между собой формально-логических моделей нейрона, каждый из которых выполняет следующий алгоритм:

Pi= X

X

увыхi=sign Pi.

Из данного режима работы устройства для моделирования нейронов легко осуществить переход к другому режиму: n/m связанных между собой формально-логических моделей нейрона на m входов каждая. Для этого требуется только установить требуемую структуру синаптических связей между моделями нейрона, что достаточно просто реализуется коммутатором 12 путем построения (описанным выше способом) необходимых каналов связи между входами и выходами коммутатора, которые подключены к нужным информационным выходам 111,.. .,11n/m и входам 21,...,2n устройства (фиг.1). Работа устройства в этом режиме для каждой из n/m моделей нейрона осуществляется в соответствии с временной диаграммой на фиг.6.

При необходимости можно перейти и к другому близкому режиму работы устройства: одна формально-логическая модель нейрона на n входов. В этом режиме логические блоки 26 выходных блоков 71,...,7n/m-1 отключаются путем подачи нулевых потенциалов на их управляющие входы 275, 276, а логический блок 26 выходного блока 7n/m остается настроенным на реализацию функции увыхi= sign Pi (как это было показано для основного режима 1). После этого осуществляется объединение n/m сумматоров 6 в один сумматор на n входов. Для этого в коммутаторе 12 реализуются каналы связи, соединяющие выход 8l (l= 1,2, . . . , n/m-1) каждого предыдущего сумматора 6l с одним из входов 13l+1,1, ...,13l+1,m последующего сумматора 6l+1 (фиг.1). Работа устройства в этом режиме осуществляется описанным выше способом в соответствии с временной диаграммой на фиг.6.

Режим работы 2: n/m градуальных моделей нейрона на m входов каждая. В этом режиме устройство реализует работу ансамбля из n/m не связанных между собой градуальных моделей нейрона на m входов каждая. Настройка устройства осуществляется так же, как и для режима n/m формально-логических моделей нейрона. Отличие состоит только в том, что на управляющие входы 275, 276 логического блока 26 каждого выходного блока 71,...,7n/m подаются соответственно единичный и нулевой потенциалы, настраивающие логические блоки на выполнение функции увыхi=max{0, Pi}. Работа устройства осуществляется в соответствии с временной диаграммой на фиг.6. После формирования в регистре 24 каждого выходного блока 71,...,7n/m k старших разрядов соответствующего значения величины Pi= X

X на управляющий вход 274 логического блока 26 каждого выходного блока 71,...,7n/m подается управляющий сигнал f274, под действием которого триггер 29 переходит в единичное (если Pi<0) либо в нулевое (Pi ≥ 0) состояние. Тогда, если Pi ≥ 0, то элемент И 31 открывается и величина Piс выхода регистра 24 через вход 35 и элемент И 33 логического блока 26 каждого выходного блока 71,...,7n/m (фиг.1, 3 и 4) в течение последующих k тактов времени появляется на выходе 11 выходных блоков 71,..., 7n/m. Если Pi<0, то элемент И 31 логического блока 26 каждого выходного блока 71,...,7n/m закрыт и на выходе 11 выходных блоков 71,...,7n/m в течение k тактов времени формируется нулевой сигнал. Иными словами в данном режиме устройство реализует работу ансамбля из n/m не связанных между собой градуальных моделей нейрона, каждый из которых выполняет алгоритм Pi=

на управляющий вход 274 логического блока 26 каждого выходного блока 71,...,7n/m подается управляющий сигнал f274, под действием которого триггер 29 переходит в единичное (если Pi<0) либо в нулевое (Pi ≥ 0) состояние. Тогда, если Pi ≥ 0, то элемент И 31 открывается и величина Piс выхода регистра 24 через вход 35 и элемент И 33 логического блока 26 каждого выходного блока 71,...,7n/m (фиг.1, 3 и 4) в течение последующих k тактов времени появляется на выходе 11 выходных блоков 71,..., 7n/m. Если Pi<0, то элемент И 31 логического блока 26 каждого выходного блока 71,...,7n/m закрыт и на выходе 11 выходных блоков 71,...,7n/m в течение k тактов времени формируется нулевой сигнал. Иными словами в данном режиме устройство реализует работу ансамбля из n/m не связанных между собой градуальных моделей нейрона, каждый из которых выполняет алгоритм Pi=  X

X

увыхi=max{0, Pi}.

Из этого режима работы устройства можно легко перейти к близким режимам: n/m связанных между собой градуальных моделей нейрона и одна градуальная модель нейрона на n входов. Такой переход осуществляется таким же способом, как и для описанного выше режима 1.

Режим работы 3: динамическая модель неадаптивного нейрона на n-2m входов. Для реализации этого режима в коммутаторе 12 реализуется система каналов связи между блоками устройства (каналы связи выделены) в соответствии с фиг. 7. Реализация этих каналов связи осуществляется путем задания соответствующих кодов коммутации в блоке 17 адресации и перевода в единичное состояние требуемых триггерных ключей матрицы 37 коммутатора 12, как это показано выше. В соответствии с показанной на фиг.7 коммутацией выход 101 устройства соединяется с основным информационным входом 2m+1 устройства, выход 92 устройства подключается к дополнительному информационному входу 31 устройства, а сумматоры 63,...,6n/m объединяются в один общий сумматор на n-2m входов путем соединения каждого l-го выхода 8l устройства (l=n/m,..., 3) с одним из входов 13l-1,1,...,13l-1,m предыдущего сумматора 6l-1, и выход 83последнего из этих сумматоров 63 подключается к любому одному из входов 1321,...,132m (на фиг.7 вход 132m) сумматора 62. После этого в регистр 18m+1 блока 1 изменения синаптических весов (фиг.1, 2 и 7) через установочный вход 4m+1 записывается двоичное k-разрядное значение коэффициента инерционности (- αi) модели нейрона, в регистр 182m через установочный вход 42m записывается двоичное значение порога ( θ i) модели нейрона, а в регистры 182m+1, . . . ,18n через установочные входы 42m+1,...,4n записываются двоичные значения синаптических весов γi,2m+1,..., γi,n модели нейрона. Логические блоки 26 выходных блоков 72,...,7n/m отключаются путем подачи на их управляющие входы 275, 276нулевых потенциалов, а логический блок выходного блока 71 настраивается на реализацию функции увыхi=max{0, Pi} путем подачи на его управляющие входы 275, 276 соответственно единичного и нулевого потенциалов. После этого устройство готово к приему двоичных k-разрядных значений входных сигналов Хi,2m+1 Δ t,...,Xi,n Δ t, поступающих через основные информационные входы 22m+1,...,2n устройства. Работает устройство в соответствии с временной диаграммой на фиг.8. В течение первых k тактов времени осуществляются прием через основные информационные входы 22m+1,..., 2n устройства k-разрядных двоичных значений входных сигналов Хi,2m+1 Δ t,.. .,Xi,n Δ t, которые записываются в регистры умножителей 202m+1,...,20n блока 1 изменения синаптических весов, а также выдача из регистра 24 выходного блока 71 через выход 111 устройства выходного сигнала увыхi Δ t модели нейрона и через выход 101 устройства величины мембранного потенциала (Pi-1Δ t) модели нейрона, которая по имеющемуся каналу связи (фиг.7) через информационный вход 2m+1 записывается в регистр умножителя 20m+1. На первом шаге, т. е. при i=1, величина Po Δ t=0 и формируется автоматически путем сброса всех регистров устройства в нулевое состояние. В течение первых k тактов времени осуществляется запись через информационный вход 22m в регистр умножителя 202m блока 1 изменения синаптических весов k-разрядного двоичного кода величины независимой переменной Δ t и при необходимомсти через дополнительные информационные входы 3m+1, 32m, 32m+1,..., 3n могут поступать k-разрядные двоичные коды приращений Δαi, Δθi, Δγi,2m+1,..., Δγi,n, которые суммируются в сумматорах 19m+1, 192m, 192m+1,...,19n(фиг.1, 2 и 7) с величинами αi-1, θi-1, γi-1,2m+1, ..., γi-1,n, полученными на предыдущем (i-1)-м шаге работы устройства.

В течение следующих 2k тактов работы устройства происходит умножение в умножителях 202m+1, . ..,20n блока 1 изменения синаптических весов входных сигналов Xi,2m+1 Δ t,... Xi,n, Δ t на синаптические веса γi,2m+1, ... γi,n в умножителе 20m+1 величины Pi-1 Δ t на коэффициент αi, в умножителе 202m величины порога θi на независимую переменную Δ t и суммирование на сумматорах 212,...21n/m, 6n/m,...,62полученных произведений. В результате в течение рассматривыемых 2k тактов времени на выходе сумматора 62 формируется 2k-разрядный двоичный код числа

ΔPi= -αiPi-1Δt+ Xij·Δt·γij-θiΔt

Xij·Δt·γij-θiΔt

Как видно из фиг.8, под действием уп-равляющего сигнала f 2, поступающего на управляющий вход 271 выходного блока 72, старшие k разрядов числа Δ Pi поступают (фиг.7) через выход 91, канал связи в коммутаторе 12, вход 31 на сумматор 191 блока 1 изменения синаптических весов, где суммируется с величиной Pi-1, полученной на предыдущем (i-1)-м шаге (на первом шаге при i= 1 величина Po=0 и формируется автоматически путем сброса всех регистров устройства в нулевое состояние) и хранящейся в регистре 181. Одновременно с этим через информационный вход 21 устройства осуществляется запись k-разрядного двоичного значения независимой переменной Δ t в регистр умножителя 201блока изменения синаптических весов. После этого в течение следующих 2k тактов происходит умножение в умножителе 201 величины Pi= =Δ Pi+Pi-1 на независимую переменную Δ t. Формируемое в течение этих 2k тактов времени 2k-разрядное произведение Pi Δ t проходит через сумматоры 211 и 61(фиг. 7), и в соответствии с временной диаграммой на фиг.8 под действием управляющего сигнала f

2, поступающего на управляющий вход 271 выходного блока 72, старшие k разрядов числа Δ Pi поступают (фиг.7) через выход 91, канал связи в коммутаторе 12, вход 31 на сумматор 191 блока 1 изменения синаптических весов, где суммируется с величиной Pi-1, полученной на предыдущем (i-1)-м шаге (на первом шаге при i= 1 величина Po=0 и формируется автоматически путем сброса всех регистров устройства в нулевое состояние) и хранящейся в регистре 181. Одновременно с этим через информационный вход 21 устройства осуществляется запись k-разрядного двоичного значения независимой переменной Δ t в регистр умножителя 201блока изменения синаптических весов. После этого в течение следующих 2k тактов происходит умножение в умножителе 201 величины Pi= =Δ Pi+Pi-1 на независимую переменную Δ t. Формируемое в течение этих 2k тактов времени 2k-разрядное произведение Pi Δ t проходит через сумматоры 211 и 61(фиг. 7), и в соответствии с временной диаграммой на фиг.8 под действием управляющего сигнала f 1, поступающего на управляющий вход 271, выходного блока 71, k старших разрядов этого произведения записываются в регистр 24 выходного блока 71 (фиг.1, 3 и 7). При этом в момент поступления самого старшего (знакового) разряда (на фиг.8 в 5-м такте времени) числа Pi Δ t на управляющий вход 274 логического блока 26 выходного блока 71 подается единичный управ- ляющий сигнал f

1, поступающего на управляющий вход 271, выходного блока 71, k старших разрядов этого произведения записываются в регистр 24 выходного блока 71 (фиг.1, 3 и 7). При этом в момент поступления самого старшего (знакового) разряда (на фиг.8 в 5-м такте времени) числа Pi Δ t на управляющий вход 274 логического блока 26 выходного блока 71 подается единичный управ- ляющий сигнал f 1, под действием которого в триггер 29 логического блока 26 выходного блока 71записывается значение знакового разряда величины Pi Δ t: триггер 29 переходит в состояние "1", если Pi Δ t<0, и в состояние "0", если Pi Δ t ≥ 0. Как указывалось выше, логический блок 26 выходного блока 71настроен на выполнение функции увыхi=max{0, Pi}. Таким образом, в данном режиме устройство реализует алгоритм работы динамического неадаптивного нейрона, который имеет следующий вид:

1, под действием которого в триггер 29 логического блока 26 выходного блока 71записывается значение знакового разряда величины Pi Δ t: триггер 29 переходит в состояние "1", если Pi Δ t<0, и в состояние "0", если Pi Δ t ≥ 0. Как указывалось выше, логический блок 26 выходного блока 71настроен на выполнение функции увыхi=max{0, Pi}. Таким образом, в данном режиме устройство реализует алгоритм работы динамического неадаптивного нейрона, который имеет следующий вид:

ΔPi= -αiPi-1Δt+ Xij·Δt·γij-θiΔt

Xij·Δt·γij-θiΔt

увыхi+1 Δ t=max{0, PiΔ t}.

В следующие 5k тактов времени работа устройства полностью повторяется в соответствии с временной диаграммой на фиг.8.

Режим работы 4: динамическая модель адаптивного нейрона на n-6m входов. Для реализации этого режима в коммутаторе 12 реализуется (описанным выше способом) система каналов связи между блоками устройства в соответствии с фиг. 9 (каналы связи выделены). В соответствии с показанной на фиг.9 коммутацией выход 101 устройства соединяется с основными информационными входами 2m+1 и 26m устройства, выход 92устройства подключается к дополнительным информационным входам 31 и 32m+1 устройства, выход 113 устройства подключается к основному информационному входу 25m+1, выход 101 устройства соединяется с основным информационным входом 24m+1, выход 95 устройства подключается к дополнительным информационным входам 33m и 33m+1, выход 86 устройства подключается к одному из входов 135,1. ..,135,m (на фиг.9 вход 135,m), а сумматоры 67,...,6n/m объединяются в один общий на n-6m входов путем соединения каждого l-го выхода 8 устройства (l=7,...,n/m) с одним из входов 13l+1,1,...,13l+1,m последующего сумматора 6l+1, и выход 8n/mпоследнего из этих сумматоров 6n/m соединяется с одним из входов 132,1, . . . ,132,m (на фиг.9 вход 132,m сумматора 62. После этого в регистр 18m+1 блока 1 изменения синаптических весов через установочный вход 4m+1(фиг.1, 2 и 9) записывается k-разрядный двоичный код числа - αi,1, в регистр 184m+1 через установочный вход 44m+1 - код числа - αi,2, в регистр 185m через установочный вход 45m - код числа - θ*, в регистр 185m+1 через установочный вход 45m+1 - код числа α1,4, в регистр 186mчерез установочный вход 46m - код числа - αi,3, а в регистры 186m+1,..., 18n через установочные коды 46m+1, . ..,4n - коды чисел γi,6m+1,..., γi,n. Логические блоки 26 выходных блоков 71, 72, 74,...,7n/mотключаются путем подачи на их управляющие входы 275, 276 нулевых потенциалов, а логический блок 26 выходного блока 73 настраивается на реализацию функции увыхi=max{0, Pi} путем подачи на его управляющие входы 275 и 276 соответственно единичного и нулевого потенциалов. После этого устройство готово к приему k-разрядных двоичных кодов входных сигналов Хi,6m+1 Δ t,...,Xi,n Δ t, поступающих через основные информационные входы 26m+1, . ..,2n устройства. Работает устройство в соответствии с временной диаграммой на фиг.10. В течение первых k тактов времени k-разрядные коды чисел Хi,6m+1 Δ t,...,Xi,n Δ t через основные информационные входы 26m+1,...,2n устройства записываются в регистры умножителей 206m+1, ...,20n блока 1 изменения синаптических весов (фиг.1, 2 и 9). В это же время из регистра 24 выходного блока 71 выдается код числа Pi-1 Δ t (на первом шаге при i=1 величина Po=0 и формируется автоматически путем сброса всех регистров устройства в ноль), которое через выход 101 по имеющемуся каналу связи (фиг.9) через основные информационные входы 2m+1 и 26m записывается в регистры 182m+1 и 186mблока изменения синаптических весов, из регистра 24 выходного блока 73выдается код числа увых,i-1 Δ t (на первом шаге при i=1 величина увыхо=0 и формируется автоматически при сбросе всех регистров устройства в ноль), которое через выход 113 устройства, имеющийся канал связи (фиг. 9), через вход 25m+1 записывается в регистр умножителя 205m+1, из регистра 24 выходного блока 74 выдается код числа θi-1 Δ t (на первом шаге при i=1 величина θо=0 и формируется автоматически при сбросе всех регистров устройства в ноль), которое через выход 104 по имеющемуся каналу связи (фиг.9), через основной информационный вход 24m+1записывается в умножитель 204m+1. В течение первых k тактов времени осуществляется запись через информационный вход 25m в регистр умножителя 205m кода числа Δ t и при необходимости через дополнительные информационные входы 3m+1, 34m+1, 35m+1, 36m, 36m+1, . . . ,3n могут поступать коды приращений Δαi,1, Δαi,2, Δαi,4, Δαi,3, Δγ6m+1, . . ., Δγn, которые суммируются на сумматорах 19m+1, 194m+1, 195m+1, 196m, 196m+1,...,19n блока изменения синаптических весов с величинами αi-1,1, αi-1,2, αi-1,4, αi-1,3, γi-1,6m+1,..., γi-1,n, полученными на предыдущем (i-1)-м шаге работы устройства.

В течение следующих 2k тактов работы устройства происходит операция умножения в умножителях 206m+1,...,20n величин Хi,6m+1 Δ t,...,Xi,n Δ t на γi,6m+1, ..., γi,n, в умножителе 206m величины Pi-1 Δ t на - α i,3, в умножителе 205m+1 величины увыхi-1 Δ t на - α i,4, в умножителе 205mвеличины - θ * на Δ t, в умножителе 204m+1 величины θ i-1 Δ t на -α i,2, в умножителе 202m+1 величины Pi-1 Δ t на -α i,1 и суммирование указанных 2k-разрядных произведений на сумматорах 212, 215, 216,...,21n/m, 62, 65, 66,...,6n. В результате в течение рассматриваемых 2k тактов времени на выходе сумматора 62 формируется 2k-разрядный код числа

ΔPi= -αi,1Pi-1Δt+ Xi,j·Δt·γij а на выходе сумматора 65 формируется 2k-разрядный код числа

Xi,j·Δt·γij а на выходе сумматора 65 формируется 2k-разрядный код числа

Δ θi =- α i,2 θ i-1Δ t- θ * Δ t- α i,3Pi-1 Δ t- α i,4yвыхi-1 Δ t.

Как видно из временной диаграммы на фиг.10, под действием управляющего сигнала f 2, поступающего на управляющий вход 271выходного блока 72, старшие k разрядов числа Δ Pi поступают (фиг.9) через выход 92, имеющийся канал связи, входы 31 и 32m+1 на сумматоры 191и 192m+1, где суммируются с величиной Pi-1, полученной на предыдущем шаге (на первом шаге Po=0) и хранящейся в регистрах 181 и 182m+1, а под действием управляющего сигнала f

2, поступающего на управляющий вход 271выходного блока 72, старшие k разрядов числа Δ Pi поступают (фиг.9) через выход 92, имеющийся канал связи, входы 31 и 32m+1 на сумматоры 191и 192m+1, где суммируются с величиной Pi-1, полученной на предыдущем шаге (на первом шаге Po=0) и хранящейся в регистрах 181 и 182m+1, а под действием управляющего сигнала f 5, поступающего на управляющий вход 271 выходного блока 75, старшие k разрядов числа Δθi поступают через выход 95, имеющийся канал связи (фиг.9), входы 33m и 33m+1 на сумматоры 193m и 193m+1, где суммируются с величиной θi-1, полученной на предыдущем (i-1)-м шаге (на первом шаге θ о=0) и хранящейся в регистрах 183m и 183m+1. Одновременно с этим через информационные входы 21, 22m+1, 23m, 23m+1 устройства осуществляется запись k-разрядного числа Δ t в регистры умножителей 201, 202m+1, 203m, 203m+1 блока 1 изменения синаптических весов.

5, поступающего на управляющий вход 271 выходного блока 75, старшие k разрядов числа Δθi поступают через выход 95, имеющийся канал связи (фиг.9), входы 33m и 33m+1 на сумматоры 193m и 193m+1, где суммируются с величиной θi-1, полученной на предыдущем (i-1)-м шаге (на первом шаге θ о=0) и хранящейся в регистрах 183m и 183m+1. Одновременно с этим через информационные входы 21, 22m+1, 23m, 23m+1 устройства осуществляется запись k-разрядного числа Δ t в регистры умножителей 201, 202m+1, 203m, 203m+1 блока 1 изменения синаптических весов.

После этого в течение следующих 2k тактов времени происходит умножение в умножителях 201, 202m+1, 203m, 203m+1 соответственно величины Pi=Pi-1+ Δ Pi на Δ t, величины Pi=Pi-1+Δ Pi на Δ t, величины θi= =θi-1+ Δ θ i на Δ t, величины θi= θi-1+ Δ t на Δ t, формируемые в течение этих 2k тактов времени 2k-разрядные произведения Pi Δ t, Pi Δ t, θi Δt, θi Δ t проходят через сумматоры 211, и 61, 213и 63, 214 и 64 и под действием управляющих сигналов f 1, f

1, f 3, f

3, f 4, поступающих на управляющие входы 271 выходных блоков 71, 73, 74(фиг.3 и 10), k старших разрядов величины Pi Δ t записываются в регистр 24 выходного блока 71, k старших разрядов величины Pi Δ t- θi Δ t записываются в регистр 24 выходного блока 73 и k старших разрядов величины θi Δ t записываются в регистр 24 выходного блока 74. При этом в момент поступления самого старшего (знакового) разряда величины Pi Δ t- θ i Δ t (на фиг. 10 5k такт времени) на управляющий вход 274логического блока 26 выходного блока 73 подается единичный управляющий сигнал f

4, поступающих на управляющие входы 271 выходных блоков 71, 73, 74(фиг.3 и 10), k старших разрядов величины Pi Δ t записываются в регистр 24 выходного блока 71, k старших разрядов величины Pi Δ t- θi Δ t записываются в регистр 24 выходного блока 73 и k старших разрядов величины θi Δ t записываются в регистр 24 выходного блока 74. При этом в момент поступления самого старшего (знакового) разряда величины Pi Δ t- θ i Δ t (на фиг. 10 5k такт времени) на управляющий вход 274логического блока 26 выходного блока 73 подается единичный управляющий сигнал f 3 , под дей- ствием которого в триггер 29 логического блока 26 выходного блока 73записывается значение знакового разряда числа PiΔt-θi Δ t. После этого логический блок 26 выходного блока 73 оказывается настроенным на реализацию функции увыхi= max{ 0, Pi} (функционирование блока 26 при реализации этой функции описано выше). В результате в данном режиме устройство реализует алгоритм работы динамического адаптивного по входу и выходу нейрона, который имеет следующий вид:

3 , под дей- ствием которого в триггер 29 логического блока 26 выходного блока 73записывается значение знакового разряда числа PiΔt-θi Δ t. После этого логический блок 26 выходного блока 73 оказывается настроенным на реализацию функции увыхi= max{ 0, Pi} (функционирование блока 26 при реализации этой функции описано выше). В результате в данном режиме устройство реализует алгоритм работы динамического адаптивного по входу и выходу нейрона, который имеет следующий вид:

ΔPi= -αi,1Pi-1Δt+ Xi,j·Δt·γij

Xi,j·Δt·γij

Δ θ i=- α i,2 θ i-1Δ t- θ *Δ t- α i,3Pi-1Δ t-

- α i,4 yвыхi-1Δ t;

yвыхin Δ t=max{0,(Pi Δ t- θi Δ t)}.

В следующие 5k тактов времени работа устройства полностью повторяется в соответствии с временной диаграммой на фиг.10. При необходимости реализации модели динамического адаптивного по входу нейрона достаточно положить значение α i,4= 0, а для модели динамического адаптивного по выходу нейрона требуется положить α i,3=0.

Режим работы 5: пространственный сумматор на n входов и вычислитель скалярного произведения n-компонентных векторов. Для реализации этого режима сумматоры 61, ...,6n/m объединяются в один общий сумматор на n входов. Для этой цели в коммутаторе 12 реализуется система каналов связи, при которой выход 8l (l=n/m,...,2) каждого l-го выходного блока 7l подключается к одному из входов 13l-1,1,...,13l-1, m предыдущего выходного блока 7l-1, а выход последнего выходного блока 72 подключается к любому из входов 131,1,. . . ,131,m выходного блока 71. В результате на выходе 81 выходного блока 71 можно получить 2k-разрядный двоичный код величины  Xi,jγi,j, которая является пространственной суммой или скалярным произведением векторов

Xi,jγi,j, которая является пространственной суммой или скалярным произведением векторов  и

и  . В тоже время при наличии управляющих сигналов (как это было показано на временных диаграммах фиг.8 и 10) 271 выходного блока 71, можно получить на выходе 91 или 101 k-разрядный код числа

. В тоже время при наличии управляющих сигналов (как это было показано на временных диаграммах фиг.8 и 10) 271 выходного блока 71, можно получить на выходе 91 или 101 k-разрядный код числа  Xi,jγi,j. Возможность получения скалярного произведения в виде k-разрядного и 2k-разрядного двоичного кода позволяет реализовать указанную операцию с требуемой точностью.

Xi,jγi,j. Возможность получения скалярного произведения в виде k-разрядного и 2k-разрядного двоичного кода позволяет реализовать указанную операцию с требуемой точностью.

Режим работы 6: n/m цифровых интеграторов. При реализации этого режима связи между блоками устройства отсутствуют, поэтому в регистрах блока 17 адресации хранятся нулевые коды коммутации, которые автоматически формируются при начальном сбросе всех регистров устройства в нулевое состояние. Логические блоки 26 всех выходных блоков 71,...,7n/m отключаются путем подачи на их управляющие входы 275, 276нулевых потенциалов. После этого в регистры 18lm+1 (l=0,1,...,n/m-1) через установочные входы 4lm+1 (l=0,1,..., n/m-1) блока 1 изменения синаптических весов записываются начальные значения подынтегральных функций Y0,l (l=0,1,..,n/m-1). Работа устройства в этом режиме осуществляется в соответствии с временной диаграммой на фиг.11. В течение первых k тактов времени на основные информационные входы 2lm+1устройства поступают k-разрядные двоичные коды независимой переменной Δ t, которые записываются в регистры умножителей 20lm+1 блока 1 изменения синаптических весов, а на дополнительные информационные входы 3lm+1устройства поступают k-разрядные приращения подынтегральных функций Δ Yi,l, которые суммируются в сумматорах 19lm+1 с начальными значениями этих функций (хранящихся в регистрах 18lm+1, и полученные текущие значения подынтегральных функций Yi,l=Yi-1,l+ Yi,l (l=0,1,..., n/m-1) записываются в регистры 18lm+1 (фиг.1 и 2). В это же время из регистров 24 выходных блоков 71, . ..,7n/m через выходы 101,...,10n/m считываются приращения интегралов Δ Pi-1,l, полученные на предыдущем (i-1)-м шаге. В течение следующих 2k тактов времени происходит умножение в умножителях 20lm+1 текущих значений подынтегральных функций Yi,l на независимую переменную Δ t и полученные произведения проходят через сумматоры 211, 61,...,21n/m, 6n/m. В результате на выходах сумматоров 61,...,6n/mформируются 2k-разрядные произведения Δ Pi,l= Yi-1,l+Yi,l, (l= 0,1,..., n/m-1), являющиеся значениями приращения интегралов, полученными в данном i-м шаге. При этом (фиг.11) под действием управляющих сигналов f272, 7n/m, k младших разрядов чисел Δ Pi,l записываются в регистры 25 выходных блоков 71,...,7n/m, а под действием управляющих сигналов f271,поступающих на управляющие входы 271 выходных блоков 71,...,7n/m, k старших разрядов чисел Δ Pi,l записываются в регистры 24 выходных блоков 71,...,7n/m. При поступлении новых значений входных сигналов описанная выше процедура полностью повторяется.

Технико-экономическая эффективность предлагаемого технического решения в сравнении с прототипом заключается в значительном расширении его функциональных возможностей (возможность моделирования путем перестройки структуры: формально-логического, градуального суммирующего, динамического адаптивного с адаптацией либо по входу, либо по выходу, либо и по входу и по выходу, динамического неадаптивного нейронов, пространственного сумматора, вычислителя скалярных произведений векторов, цифровых интеграторов) при одновременном упрощении, что позволяет реализовать устройства на одном кристалле БИС уже при современном состоянии отечественной микроэлектронной технологии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

| Устройство для выполнения матричных операций | 1989 |

|

SU1714617A1 |

| МАТРИЧНЫЙ КОММУТАТОР | 1994 |

|

RU2103729C1 |

Изобретение относится к бионике и вычислительной технике и может быть использовано в качестве элемента нейроподобных сетей при моделировании нейрофизиологических процессов в нервной системе, в устройствах обработки, анализа и распознавания образов, в системах управления интеллектуальными роботами, в цифровых нейрокомпьютерах. Цель изобретения - расширение функциональных возможностей и упрощение устройства. Для этого в устройство, содержащее блок изменения синаптических весов, первые n входов которого являются основными информационными входами устройства, а вторые n входов - установочными входами, введены n/m (m < n, n ≥ 12, m > 2) сумматоров, n/m выходных блоков, коммутатор и блок адресации, причем каждый выходной блок содержит первый и второй элементы И, первый и второй регистры и логический блок. При существенном упрощении устройство обладает более широкими функциональными возможностями, позволяющими моделировать, в частности, формально-логические, градуальные динамические адаптивные и неадаптивные модели нейронов, пронстранственный сумматор, вычислители скалярного произведения и цифровые интеграторы. 1 з.п. ф-лы, 11 ил.

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пуговица для прикрепления ее к материи без пришивки | 1921 |

|

SU1992A1 |

Авторы

Даты

1995-02-20—Публикация

1991-07-01—Подача