Изобретение относится к автоматике и вычислительной техники и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности.

Техническим результатом является повышение живучести и отказоустойчивости вычислительной системы.

В основу предлагаемого устройства положено многократное резервирование каналов обработки информации в вычислительной системе и последующего адаптивного мажоритирования выходных данных всех каналов обработки данных. Управление аппаратной избыточностью осуществляется в зависимости от состояния вычислительной системы аппаратно.

Наиболее близким по технической сущности является мажоритарный блок элементов, например, [1]. Согласно известных устройств мажоритирования в вычислительной системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т. д. Выбор варианта мажоритирования и переход с одного варианта на другой вариант в системе осуществляется программно.

Недостатком известного устройства мажоритирования [1] является необходимость во временной избыточности на анализ и поиск неисправного канала, а также на программный переход на нижний уровень мажоритирования.

Согласно предлагаемому блоку адаптивное мажоритирование в вычислительной системе выполняют путем принудительной засылки нуля на выход первого (не четного номера) отказавшего канала вычислительной системы и принудительной засылки единицы на выход второго (четного номера) отказавшего канала вычислительной системы, тем самым аппаратно снижается лишь только уровень мажоритирования в вычислительной системе, при этом надежная работоспособность вычислительной системы сохраняется до двух исправных каналов в вычислительной системе.

Целью заявляемого блока является повышение надежности, живучести и отказоустойчивости вычислительной системы.

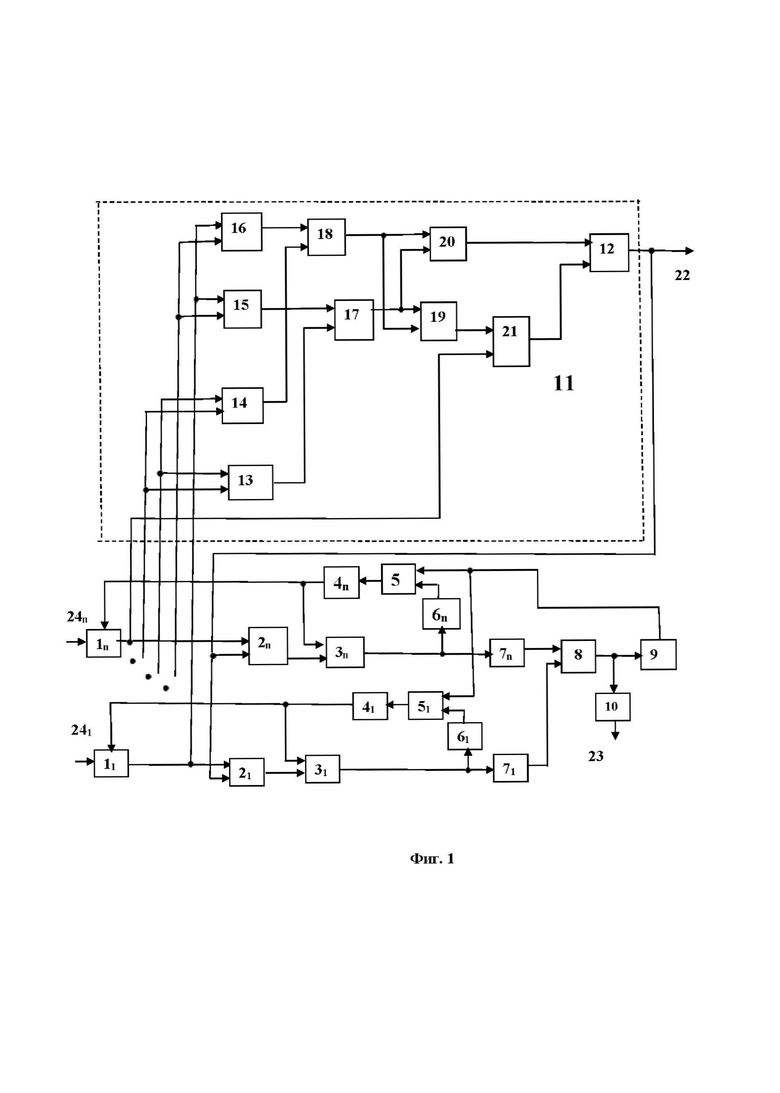

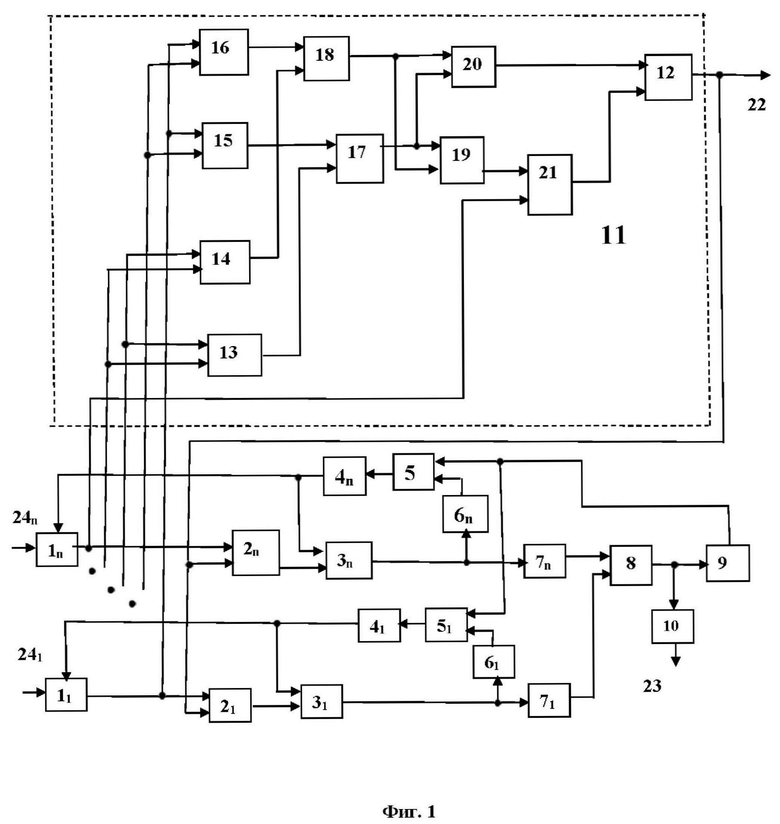

Указанная цель достигается тем, что в адаптивный мажоритарный блок, содержащий группу первых элементов ИЛИ (11, … 1n), группу элементов сложения по mod 2 (21, … 2n), группу первых триггеров (31, … 3 n), группу первых элементов И (51, … 5 n), первый элемент ИЛИ (8), счетчик (10), блок (11) мажоритарных элементов «n и более из (2n-1)», (в качестве примера «3 из 5»), второй элемент И (13), второй элемент ИЛИ (14), третий элемент И (15), третий элемент ИЛИ (16), четвертый элемент ИЛИ (17), четвертый элемент И (18), пятый элемент И (19), пятый элемент ИЛИ (20), шестой элемент ИЛИ (21), шестой элемент И (12), входы (241, … 24 n) блока подсоединены к одноименным первым входам первых элементов ИЛИ (11, … 1n), выход первого элемента ИЛИ (11) подсоединен к первому входу третьего элемента И (15) и к первому входу третьего элемента ИЛИ (16), выход второго элемента ИЛИ (12) подсоединен к второму входу третьего элемента И (15) и к второму входу третьего элемента ИЛИ (16), выход третьего элемента ИЛИ (13) подсоединен к первому входу второго элемента И (13) и к первому входу второго элемента ИЛИ (14), выход четвертого элемента ИЛИ (14) подсоединен к второму входу второго элемента И (13) и к второму входу второго элемента ИЛИ (14), выход пятого элемента ИЛИ (15) подсоединен к первому входу шестого элемента ИЛИ (21), выход второго элемента И (13) подсоединен к первому входу четвертого элемента ИЛИ (17), выход второго элемента ИЛИ (14) подсоединен к первому входу четвертого элемента И (18), выход третьего элемента И (15) подсоединен к второму входу четвертого элемента ИЛИ (17), выход третьего элемента ИЛИ (16) подсоединен к второму входу четвертого элемента И (18), выход которого подсоединен к первому входу пятого элемента И (19) и к первому входу пятого элемента ИЛИ (20), выход четвертого элемента ИЛИ (17) подсоединен к второму входу пятого элемента И (19) и к второму входу пятого элемента ИЛИ (20), выход пятого элемента И (19) подсоединен к второму входу шестого элемента ИЛИ (21), выход которого подсоединен к первому входу шестого элемента И (12), выход пятого элемента ИЛИ (20) подсоединен к второму входу шестого элемента И (12), выход которого является выходом 22 устройства, введены группа вторых триггеров (41, … 4 n), группа элементов задержки (61, … 6n), группа дифференцирующих цепочек (71, … 7 n), триггер со счетным входом (9), выходы первых элементов ИЛИ (11, … 1n) подсоединены к первым входам одноименных элементов сложения по mod 2 (21, … 2 n), выходы которых подсоединены к первым входам одноименных первых триггеров (31, … 3 n), выходы которых подсоединены к входам одноименных элементов задержки (61, … 6n) и дифференцирующих цепочек (71, … 7 n), выходы дифференцирующих цепочек (71, … 7 n) подсоединены к одноименным входам первого элемента ИЛИ (8), выход которого подсоединен к входу счетчика (10) и к входу триггера со счетным входом (9), выход которого подсоединен к первым входам первых элементов И (51, … 5 n), вторые входы которых подсоединены к выходам одноименных элементов задержки (61, … 6n), выходы первых элементов И (51, … 5 n) подсоединены к входам одноименным вторых триггеров (41, … 4 n), выходы которых подсоединены к вторым входам одноименным первых триггеров (31, … 3 n) и к вторым входам первых элементов ИЛИ (11, … 1n), выход шестого элемента И (12) подсоединен к вторым входам элементов сложения по mod 2 (21, … 2 n),

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Сущность изобретения поясняется чертежом. На фиг. 1 представлено схематичное изображение адаптивного мажоритарного блока элементов «n и более из (2n -1)».

Сущность изобретения поясняется чертежом. Адаптивный мажоритарный блок элементов «n и более из (2n -1)» (фиг. 1) содержит: группа элементов ИЛИ (11, … 1n), группа элементов сложения по mod 2 (21, … 2 n), группа триггеров (31, … 3 n), группа триггеров (41, … 4 n), группа элементов И (51, … 5 n), группа элементов задержки (61, … 6n), группа дифференцирующих цепочек (71, … 7 n), элемент ИЛИ (8), триггер со счетным входом (9), счетчик (10), блок мажоритарных элементов (11) (на примере блока элементов «3 из 5»), элемент И (12), элемент И (13), элемент ИЛИ (14), элемент И (15), элемент ИЛИ (16), элемент ИЛИ (17), элемент И (18), элемент И (19), элемент ИЛИ (20), элемент ИЛИ (21), элемент И (22), выходы (22, 23), входы (241, … 24n) вместе со связями.

Блок работает следующим образом. В исходном состоянии все триггеры (31, … 3n), триггеры (41, … 4n), триггер со счетным входом (9), счетчик (10) находятся в нулевом состоянии.

Элементы 12 – 21 реализуют функцию F мажоритарного органа (далее в качестве примера рассматривается блок «3 из 5») в соответствии с таблицей 1.

Таблица 1

При выходе из строя одного из пяти каналов (например, первого, то есть х1=0, а х2=х3=х4=х5=1) на выходе 22 мажоритарного блока 11 будет единичный сигнал, который подаётся на первые входы всех элементов сложения по mod 2 (21, … 25). На выходе элемента ИЛИ 11 будет нулевой сигнал, который подаётся на второй вход элемента сложения по mod 2 (21), с выхода которого единичный сигнал устанавливает в единичное состояние триггер (31).

Единичный сигнал с выхода триггера (31) через дифференцирующую цепочку (71) и элемент ИЛИ (8) устанавливает счетчик (10) и триггер со счетным входом (9) в единичное состояние, после чего на первом входе элемента И (51) будет единичный сигнал. Элемент задержки (61) задерживает сигнал на время надежного срабатывания дифференцирующей цепочки (71), элемента ИЛИ (8) и триггера со счетным входом (9).

Единичный сигнал с выхода элемента И 51 устанавливает триггер 41 в единичное состояние. Единичный сигнал с выхода триггера 41 сбрасывает в нулевое состояние триггер 31, а на выходе элемента ИЛИ 11 будет теперь единичный сигнал, то есть далее х1=1.

Далее при возможном выходе из строя еще одного из каналов (например, пятого, то есть х5=0, а х1=х2=х3=х4=1) на выходе мажоритарного органа (11) (выход элемента И (12)) будет единичный сигнал, который подаётся на вторые входы всех элементов сложения по mod 2 (21, … 25). На выходе элемента ИЛИ (15) будет нулевой сигнал, который подаётся на первый вход элемента сложения по mod 2 (25), с выхода которого единичный сигнал устанавливает в единичное состояние триггер (35).

Единичный сигнал с выхода триггера (35) через дифференцирующую цепочку (75) и элемент ИЛИ (8) устанавливает триггер со счетным входом (9) теперь в нулевое состояние, после чего на втором входе элемента И (55) будет нулевой сигнал. Нулевой сигнал с выхода элемента И (55) не установит триггер (45) в единичное состояние. Нулевой сигнал с выхода триггера (45) подается на второй вход элемента ИЛИ (15), поэтому на выходе элемента ИЛИ (15) будет нулевой сигнал, то есть х5=0.

Код числа отказов в системе с выхода счетчика (10) подается на выход (23) устройства.

Таким образом, при последовательном выходе из строя двух из пяти каналов мажоритарный блок элементов «3 и более из 5» будет работать исправно. Однако, на один не исправный вход мажоритарного блока элементов «n и более из (2n-1)» будет подаваться нулевой сигнал, а на второй не исправный вход – единичный сигнал, исходный адаптивный мажоритарный блок элементов «n и более из (2n-1)» автоматически перестраивается в систему мажоритарный блок элементов по рангу на ступень ниже, что существенно повышает достоверность обрабатываемой мажоритарном блоком информации.

1. АС №2716061, кл. G06F 12/14, 2020.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный мажоритарный блок элементов "3 из 5" | 2021 |

|

RU2764839C1 |

| Способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов | 2024 |

|

RU2835006C1 |

| Устройство мажоритирования с заменой | 2020 |

|

RU2726646C1 |

| КРУГОВОЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2022 |

|

RU2785771C1 |

| Устройство для передачи и приема сигналов | 1988 |

|

SU1732365A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЗИЦИОННЫХ СУММАТОРОВ ПО МОДУЛЮ | 2002 |

|

RU2231823C2 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2016 |

|

RU2628890C1 |

| МНОГОКАНАЛЬНОЕ РЕГУЛИРУЮЩЕЕ УСТРОЙСТВО | 1985 |

|

SU1329432A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| УСТРОЙСТВО ДЛЯ АВАРИЙНОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2101768C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности. Технический результат заключается в повышении живучести и отказоустойчивости вычислительной системы за счет многократного резервирования каналов обработки информации и последующего адаптивного мажоритирования выходных данных всех каналов обработки данных. Устройство содержит группу элементов ИЛИ, группу элементов И, группу элементов сложения по mod 2, счетчик, группу триггеров, группу элементов задержки, группу дифференцирующих цепочек. 1 ил., 1 табл.

Адаптивный мажоритарный блок элементов «n и более из (2n-1)», содержащий группу первых элементов ИЛИ (11, … 1n), группу элементов сложения по mod 2 (21, … 2n), группу первых триггеров (31, … 3n), группу первых элементов И (51, … 5n), первый элемент ИЛИ (8), счетчик (10), блок (11) мажоритарных элементов «n и более из (2n-1)», входы (241, … 24n) устройства подсоединены к первым входам одноименных первых элементов ИЛИ (11, … 1n), отличающийся тем, что в него введены группа вторых триггеров (41, … 4n), группа элементов задержки (61, … 6n), группа дифференцирующих цепочек (71, … 7n), триггер со счетным входом (9), выходы первых элементов ИЛИ (11, … 1n) подсоединены к первым входам одноименным элементов сложения по mod 2 (21, … 2n), выходы которых подсоединены к первым входам одноименных первых триггеров (31, … 3n), выходы которых подсоединены к входам одноименных элементов задержки (61, … 6n) и дифференцирующих цепочек (71, … 7n), выходы дифференцирующих цепочек (71, … 7n) подсоединены к одноименным входам первого элемента ИЛИ (8), выход которого подсоединен к входу счетчика (10) и к входу триггера со счетным входом (9), выход которого подсоединен к первым входам первых элементов И (51, … 5n), вторые входы которых подсоединены к выходам одноименных элементов задержки (61, … 6n), выходы первых элементов И (51, … 5n) подсоединены к входам одноименным вторых триггеров (41, … 4n), выходы которых подсоединены к вторым входам одноименным первых триггеров (31, … 3n) и к вторым входам первых элементов ИЛИ (11, … 1n), выход 22 устройства подсоединен к вторым входам элементов сложения по mod 2 (21, … 2n).

| Адаптивный мажоритарный блок элементов "3 из 5" | 2021 |

|

RU2764839C1 |

| US 7741864 B2, 22.06.2010 | |||

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "5 И БОЛЕЕ ИЗ 9" | 2016 |

|

RU2665226C2 |

| Устройство мажоритирования с заменой | 2020 |

|

RU2726646C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2701461C1 |

Авторы

Даты

2024-04-23—Публикация

2023-08-09—Подача