Изобретение относится к вычислительной технике и может быть использовано, например, в системах, построенных на базе микропроцессоров, работающих в широком диапазоне тактовых частот.

Цель изобретения - расширение области применения за счет расширения диапазона частот функционирования.

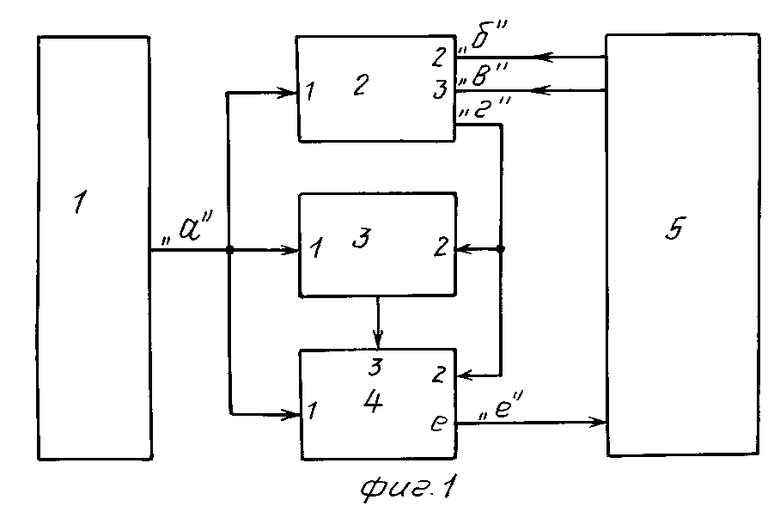

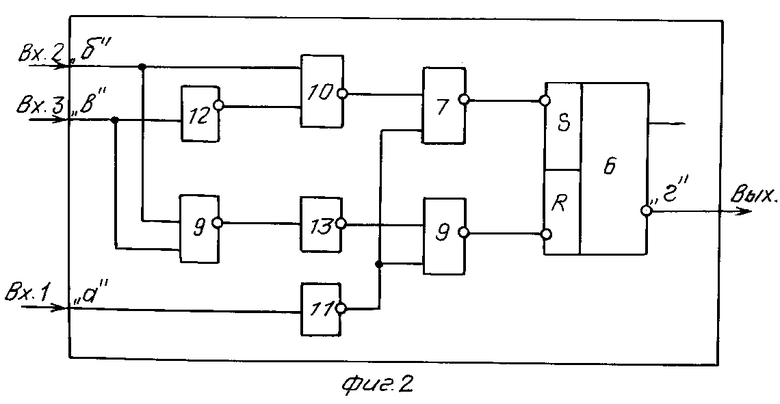

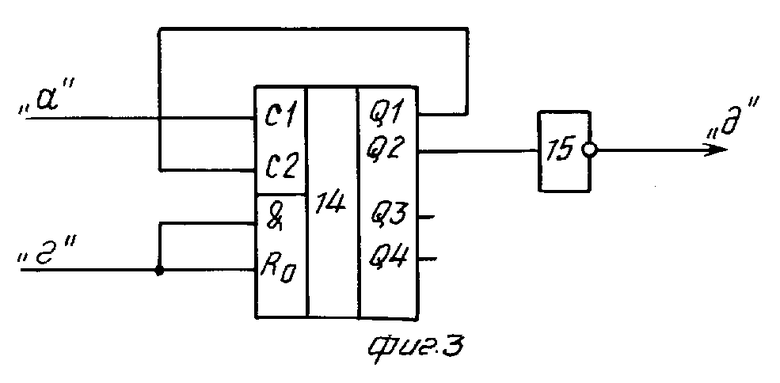

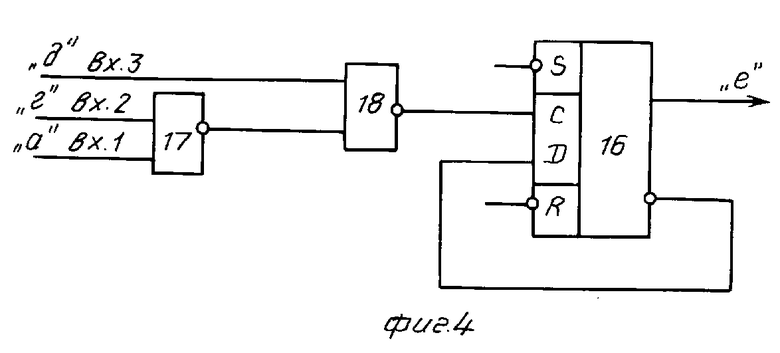

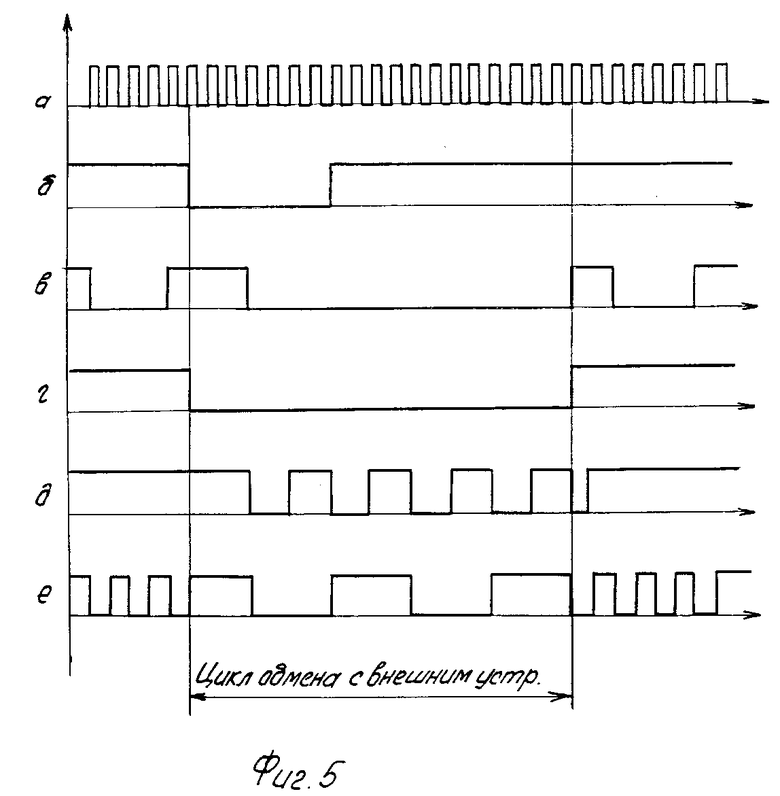

На фиг. 1 - блок-схема предложенного устройства для синхронизации работы быстродействующих микропроцессоров с внешними устройствами; на фиг. 2 - функциональная схема блока управления режимом синхронизации; на фиг. 3 - функциональная схема блока счета времени; на фиг. 4 - функциональная схема блока формирования синхроимпульсов; на фиг. 5 - временная диаграмма работы устройства.

Устройство для синхронизации работы быстродействующих микропроцессоров с внешними устройствами (фиг. 1) содержит генератор 1 тактовых импульсов, соединенный с входами блока 2 управления режимом синхронизации, блока 3 счета времени и блока 4 формирования синхроимпульсов, с выхода которого синхроимпульсы поступают на вход микропроцессора 5, который, в свою очередь, формирует управляющие сигналы, поступающие на входы блока 2 управления режимом синхронизации.

Блок 2 управления режимом синхронизации (фиг. 2) предназначен для выработки управляющего сигнала в зависимости от поступающих сигналов от микропроцессора и поступающих на вход блока 3 счета времени и блока 4 формирования синхроимпульсов, содержит RS-триггер 6, элементы И-НЕ 7-9, элемент ИЛИ-НЕ 10 и три элемента НЕ 11-13.

Блок 3 счета времени (фиг. 3) предназначен для формирования тактовых импульсов, поступающих на вход блока 4 формирования синхроимпульсов, содержит двоичный счетчик 14 и элемент НЕ 15.

Блок 4 формирования синхроимпульсов (фиг. 4) обеспечивает поступление на вход микропроцессора синхроимпульсов необходимой частоты и длительности в зависимости от управляющих сигналов и содержит D-триггер 16 и два элемента И-НЕ 17, 18.

На временной диаграмме работы устройства для синхронизации работы быстродействующих микропроцессоров с внешними устройствами (фиг. 5) обозначено: а - тактовые импульсы, поступающие от генератора 1 тактовых импульсов; б - сигнал "ВУ" на линии "Выбор устройства", поступающий от микропроцессора 5 и используемый в качестве признака обращения к периферийным устройствам; в - сигнал "ОБМ" на линии "Синхронизация обмена", вырабатываемый микропроцессором 5 для инициализации обмена; г - управляющий сигнал, вырабатываемый блоком 2 управления режимом синхронизации; д - тактовые импульсы, поступающие от блока 3 счета времени на вход блока 4 формирования синхроимпульсов; е - синхроимпульсы, поступающие на вход микропроцессора 5, используемые для синхронизации работы всех блоков микропроцессора 5.

На временной диаграмме выделен цикл обмена с внешним устройством.

Устройство для синхронизации работы быстродействующих микропроцессоров с внешними устройствами работает следующим образом.

Тактовые импульсы (фиг. 5а) с выхода генератора 1 поступают на входы блока 2 управления режимом синхронизации, блока 3 счета времени и блока 4 формирования синхроимпульсов.

От микропроцессора 5 на разрешающий вход (фиг. 5б) блока 2 управления режимом синхронизации напряжением низкого уровня поступает сигнал "Выбор устройства" ("ВУ") (фиг. 5б), используемый в качестве признака обращения к периферийным (медленно действующим) устройствам, а на другой - разрешающий вход (фиг. 5в) блока 2 управления режимом синхронизации также напряжением низкого уровня поступает сигнал "Синхронизация обмена" ("ОБМ") (фиг. 5в).

Необходимость использования двух управляющих сигналов обусловлена тем, что сигнал "ВУ", являющийся признаком обращения к медленно действующим устройствам, вырабатывается микропроцессором в соответствии с протоколом обмена только на первой стадии формирования цикла обмена (см. фиг. 5). Для завершения формирования полного цикла обмена с медленно действующим внешним устройством используется вырабатываемый микропроцессором сигнал "ОБМ".

Сигналы "ВУ" и "ОБМ" поступают на элемент ИЛИ-НЕ 10. Сигнал с выхода элемента ИЛИ-НЕ 10 поступает на вход элемента И-НЕ 7 и стробируется тактовыми импульсами от генератора 1, прошедшими через элемент НЕ 11, поступающими на второй вход элемента И-НЕ 7. С выхода элемента И-НЕ 7 сигнал поступает на управляющий вход S RS-триггера 6 и низким потенциалом устанавливает RS-триггер в единичное состояние, при этом на инверсном выходе RS-триггера 6 вырабатывается низкий уровень сигнала "Обмен с медленно действующим внешним устройством" ("ОМУ") (фиг. 5г). Сброс сигнала "ОМУ" (формирование на инверсном выходе RS-триггера 6 высокого уровня сигнала) осуществляется подачей на R-вход RS-триггера сигнала низкого потенциала. Такой сигнал формируется при прохождении сигналов "ВУ" и "ОБМ" через элемент И-НЕ 9, сигнал с выхода которого инвертируется на элементе НЕ 13 и стробируется тактовыми импульсами на элементе И-НЕ 8.

Сигнал "ОМУ" является результирующим двух сигналов "ВУ" и "ОБМ" и действует в течение всего цикла обмена с медленно действующим внешним устройством. Стробирование формирования переднего и заднего фронтов сигнала "ОМУ" тактовыми импульсами, поступающими от генератора 1, производится с целью предотвращения возможности возникновения на входе синхронизации микропроцессора 5 импульсов с параметрами по длительности или периоду, недопустимыми в качестве синхроимпульсов микропроцессоров.

Таким образом, с выхода блока 2 управления режимом синхронизации выдается (фиг. 5г) напряжением низкого уровня сигнал "ОМУ", который поступает на вторые входы блока 3 счета времени и блока 4 формирования синхроимпульсов.

Блок счета времени из тактовых импульсов, поступающих от генератора 1 на "а" вход счетчика 14, формирует тактовые импульсы, используемые в качестве синхроимпульсов для микропроцессора 5 в цикле работы с медленно действующими внешними устройствами. Формирование тактовых импульсов осуществляется с помощью двоичного счетчика 14, управляемого сигналом "ОМУ", поступающим на управляющий вход счетчика 14 устройства счета времени. Наличие на управляющем входе 2 потенциала низкого уровня (сигнала "ОМУ") разрешает счет тактовых импульсов, поступающих от генератора 1, а следовательно, и выработку тактовых импульсов блока 3 счета времени. Высокий уровень напряжения на втором входе (фиг. 5г) устанавливает счетчик 14 в исходное состояние. Для обеспечения синхронизации работы быстродействующего микропроцессора 5 с внешними устройствами, то есть для согласования временных характеристик работы микропроцессора 5 с временными характеристиками работы внешних устройств, на время цикла обмена изменением уровня (сигнала "ОМУ") осуществляется переключение сигналов "а" тактовой частоты, поступающей от генератора 1, на сигналы "д" тактовой частоты, вырабатываемые блоком 3 счета времени, при этом осуществляется снижение тактовой частоты синхроимпульсов, поступающих на вход синхронизации микропроцессора 5, для этого тактовые импульсы, вырабатываемые блоком 3 счета времени (фиг. 5д), берутся с соответствующего выхода двоичного счетчика 14.

На фиг. 3 показано, что тактовые импульсы берутся с выхода 2 счетчика 14, что приводит к снижению тактовой частоты синхроимпульсов в 4 раза. Если частотное соотношение временных диаграмм работы микропроцессора и внешнего устройства находится в другом диапазоне, то используют другой выход счетчика 14, обеспечивающий формирование соответствующей частоты. При работе с несколькими внешними устройствами, имеющими различные временные характеристики, возможно использование программно-настраиваемого счетчика времени и перестраивание временной диаграммы работы микропроцессора 5 в соответствии с временными характеристиками работы внешних устройств.

Тактовые импульсы от генератора 1 и от блока 3 счета времени поступают на вход блока 4 формирования синхроимпульсов. В зависимости от уровня управляющего сигнала ОМУ (фиг. 5г), поступающего на вход 2 блока формирования синхроимпульсов, синхроимпульсы, поступающие на вход микропроцессора 5, вырабатываются либо с использованием тактовых импульсов генератора 1, либо тактовых импульсов блока 3 счета времени.

Выбор используемых тактовых импульсов осуществляется на элементах И-НЕ 7 17, 18. При высоком уровне сигнала "ОМУ" в формировании синхроимпульсов участвуют тактовые импульсы, поступающие от генератора 1. При низком уровне сигнала ОМУ на вход D-триггера 16, формирующего синхроимпульсы для микропроцессора 5, поступают тактовые импульсы от блока 3 счета времени. На выходе D-триггера 16 формируются синхроимпульсы, обеспечивающие синхронизацию работы микропроцессора 5 в различных частотных режимах.

Таким образом, изменение частоты синхроимпульсов, поступающих на вход микропроцессора, в зависимости от управляющих сигналов приводит к изменению временной диаграммы работы микропроцессора. При этом на время работы с внешним устройством (на время действия управляющих сигналов "ВУ" и "ОБМ") осуществляется согласование временных диаграмм работы микропроцессора и внешнего устройства. Переход на более низкие тактовые частоты работы микропроцессора, определяемые характеристиками внешних устройств, осуществляется только на период работы с этими устройствами.

В остальное время микропроцессор работает на частотах синхронизации, определяемых возможностями самого микропроцессора и возможностями быстродействующих устройств (ОЗУ и ПЗУ). Это позволяет проводить обработку полученной информации на максимально возможных для систем частотах, повышает быстродействие и производительность микропроцессорных систем, повышая тем самым эффективность их работы. В ряде случаев в многопроцессорных системах с заданными характеристиками по производительности можно достигнуть сокращения числа процессоров в системах.

Внедрение устройства для синхронизации быстродействующих микропроцессоров с медленно действующими внешними устройствами позволяет легко осуществлять переход к новым более быстродействующим и производительным микропроцессорам при сохранении частотных данных прежних внешних устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации системыОбМЕНА иНфОРМАциЕй | 1979 |

|

SU847310A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для контроля больших интегральных схем | 1988 |

|

SU1672454A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Счетчик фотонов | 1988 |

|

SU1595181A1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение области применения путем расширения диапазона тактовых частот функционирования. Устройство содержит генератор тактовых импульсов, блок счета времени, блок управления режимом синхронизации и блок формирования синхроимпульсов. 5 ил.

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ РАБОТЫ БЫСТРОДЕЙСТВУЮЩИХ МИКРОПРОЦЕССОРОВ С ВНЕШНИМИ УСТРОЙСТВАМИ, содержащее генератор тактовых импульсов и блок счета времени, тактовый вход которого соединен с выходом генератора тактовых импульсов, отличающееся тем, что, с целью расширения области применения за счет расширения диапазона тактовых частот функционирования, оно содержит блок управления режимом синхронизации и блок формирования синхроимпульсов, причем выход генератора тактовых импульсов соединен с тактовым входом блока управления режимом синхронизации и первым тактовым входом блока формирования синхроимпульсов, второй тактовый вход которого соединен с выходом блока счета времени, разрешающий вход которого и вход выбора режима блока формирования синхроимпульсов соединены с выходом блока управления режимом синхронизации, первый и второй разрешающие входы которого являются входами устройства для подключения соответственно к выходам выбора устройства и синхронизации обмена микропроцессора, выход блока формирования синхроимпульсов является выходом устройства для подключения к входу синхронизации микропроцессора, причем блок управления режимом синхронизации содержит три элемента И - НЕ, три элемента НЕ, элемент ИЛИ - НЕ и триггер, инверсный выход которого является выходом блока, первый разрешающий вход блока соединен с первыми входами элемента ИЛИ - НЕ и первого элемента И - НЕ, второй разрешающий вход блока соединен с вторым входом первого элемента И - НЕ и через первый элемент НЕ - с вторым входом элемента ИЛИ - НЕ, выход которого соединен с первым входом второго элемента И - НЕ, выход первого элемента И - НЕ через второй элемент НЕ соединен с первым входом третьего элемента И - НЕ, тактовый вход блока через третий элемент НЕ соединен с вторыми входами второго и третьего элементов И - НЕ, выходы которых соединены соответственно с входами установки в "1" и в "0" триггера, причем блок формирования синхроимпульсов содержит два элемента И - НЕ и триггер, выход которого является выходом блока, первый тактовый вход и вход выбора режима блока соединены соответственно с первым и вторым входами первого элемента И - НЕ, выход которого соединен с первым входом второго элемента И - НЕ, второй вход которого является вторым тактовым входом блока, выход второго элемента И - НЕ соединен с синхровходом триггера, информационный вход которого соединен со своим инверсным выходом.

Авторы

Даты

1994-05-30—Публикация

1991-04-08—Подача