ел с

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

Изобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки больших интегральных схем /БИС/, и может быть использовано для тестового контроля БИС микропроцессорных наборов. Целью изобретения является повышение полноты контроля. С этой целью в устройство, содержащее эталонный блок, формирователь тактовых импульсов, блок сравнения, регистр индикации, задающий генератор, блок задания режимов и блок шинных формирователей, введены блок формирования начальных адресов, блок управления обменом и генератор тестов. 2 з.п. ф-лы, 8 ил., 1 табл.

Иэобретение относится к цифровой вычислительной технике, в частности к устройствам для проверки больших интегральных схем (БИС), и можег быть использовано для тестового контроля БИС микропроцессорных наборов.

Целью изобретения является повышение полноты контроля.

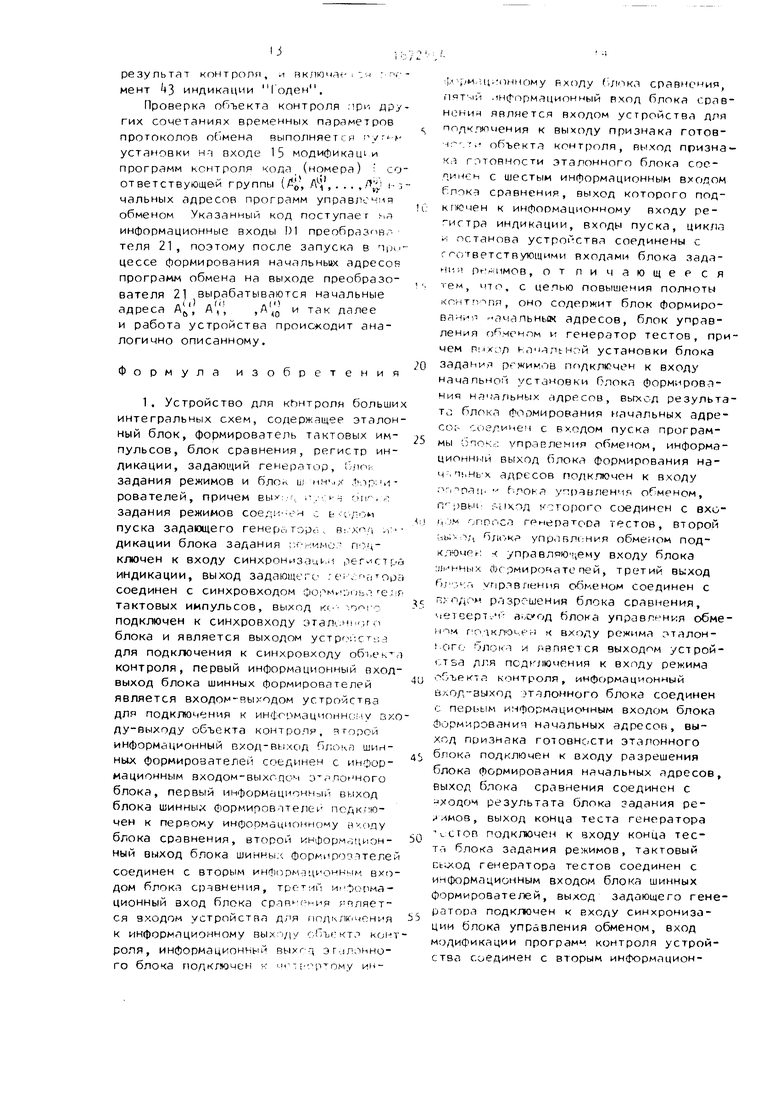

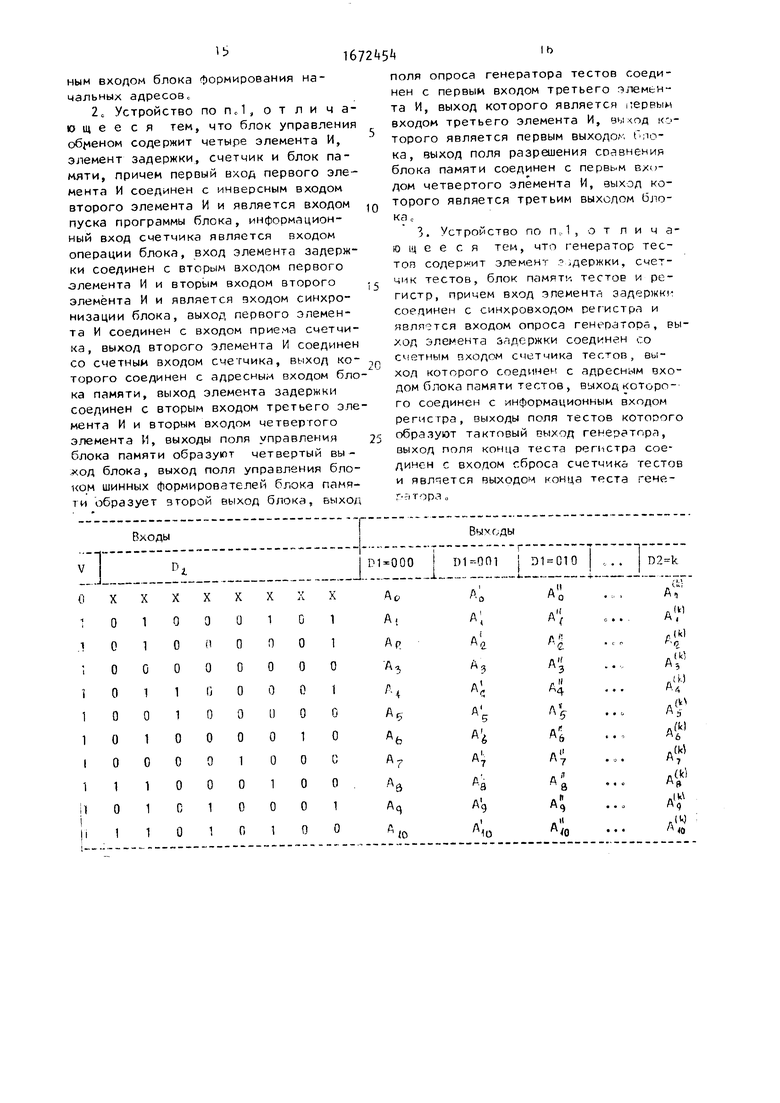

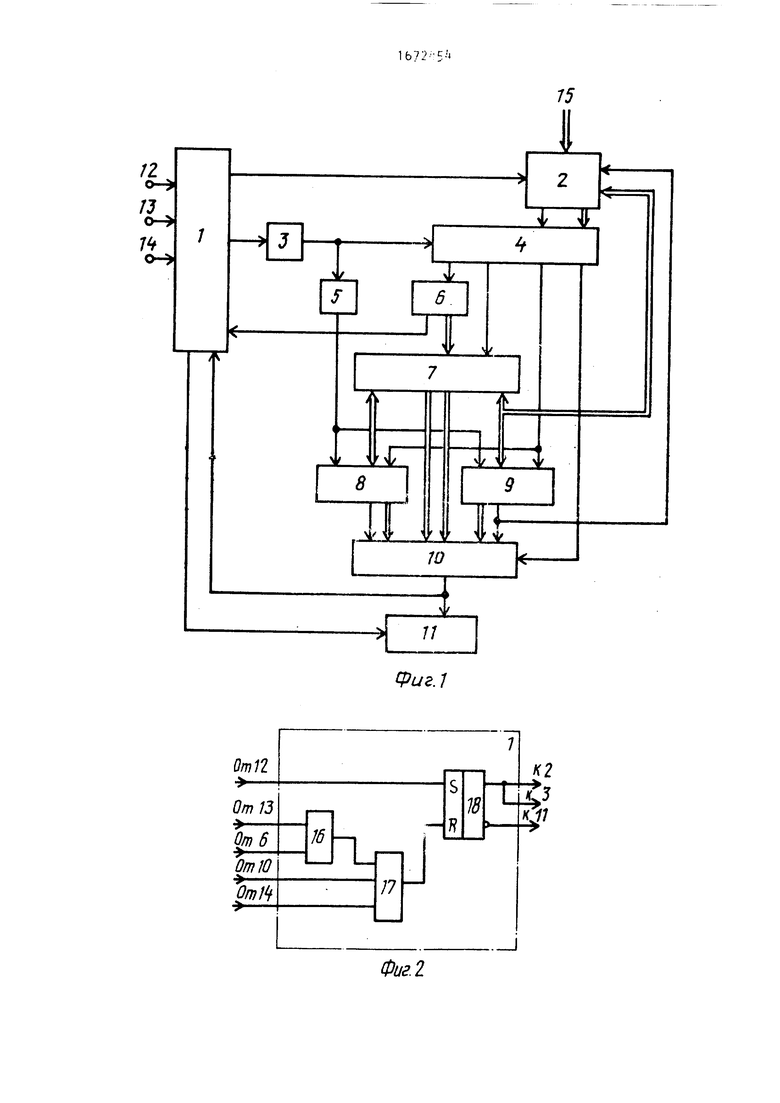

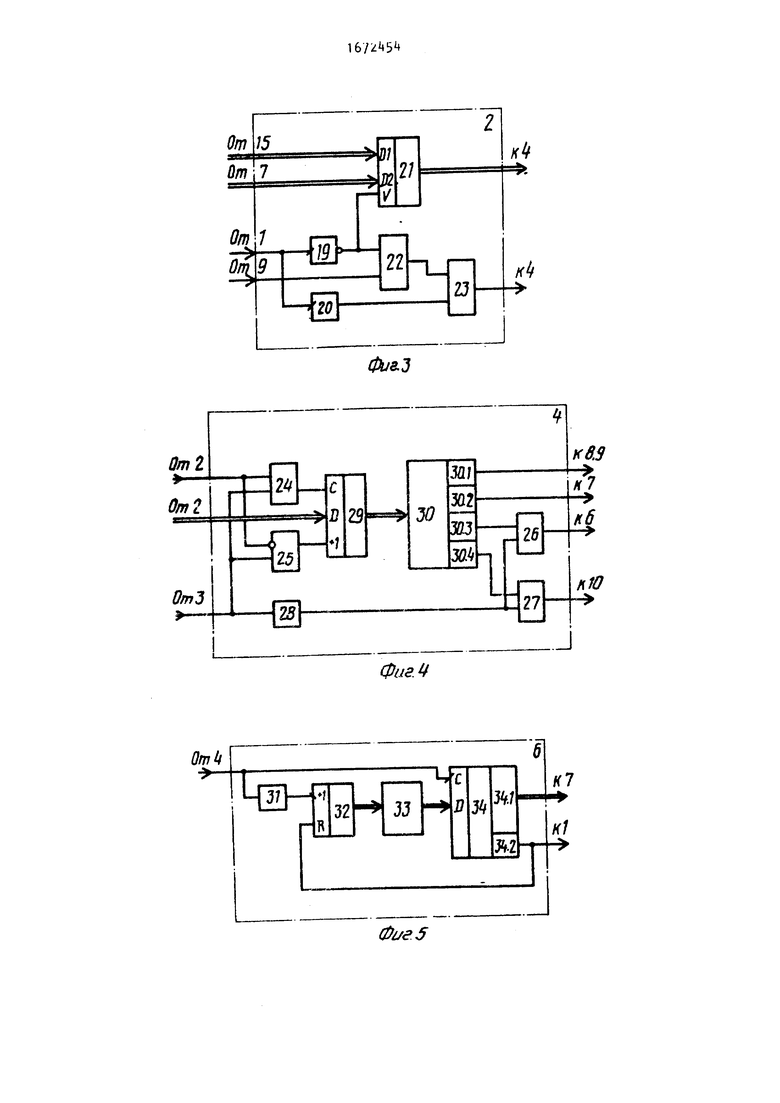

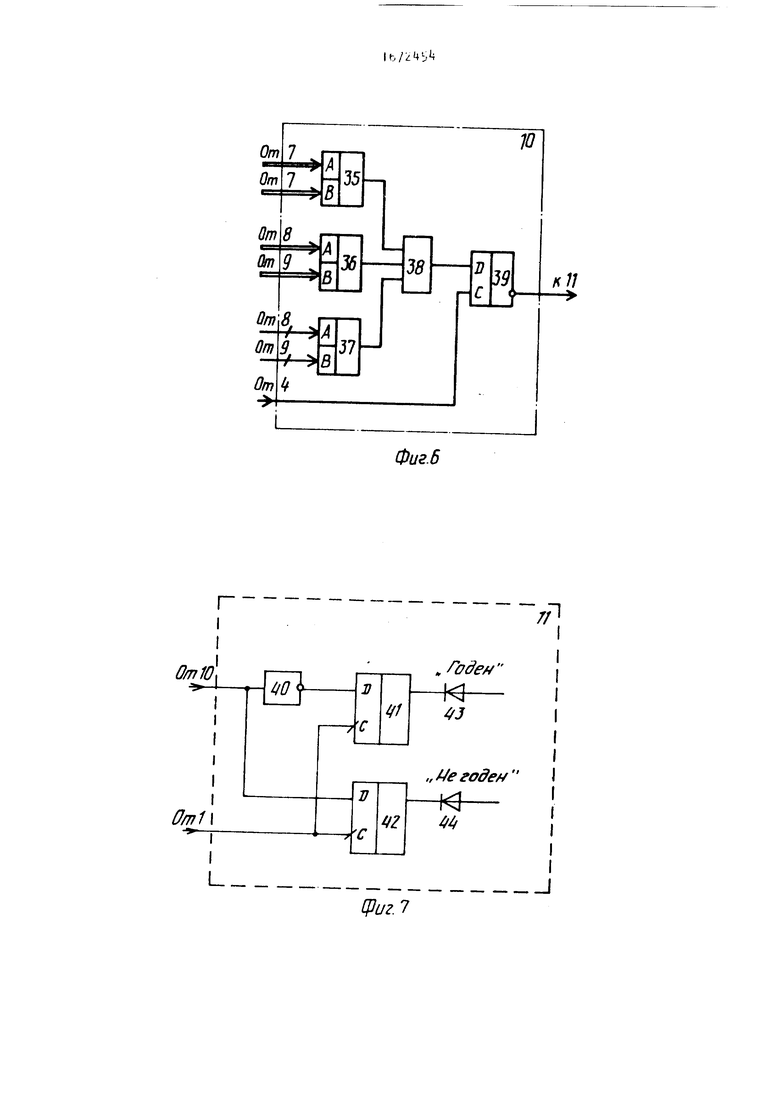

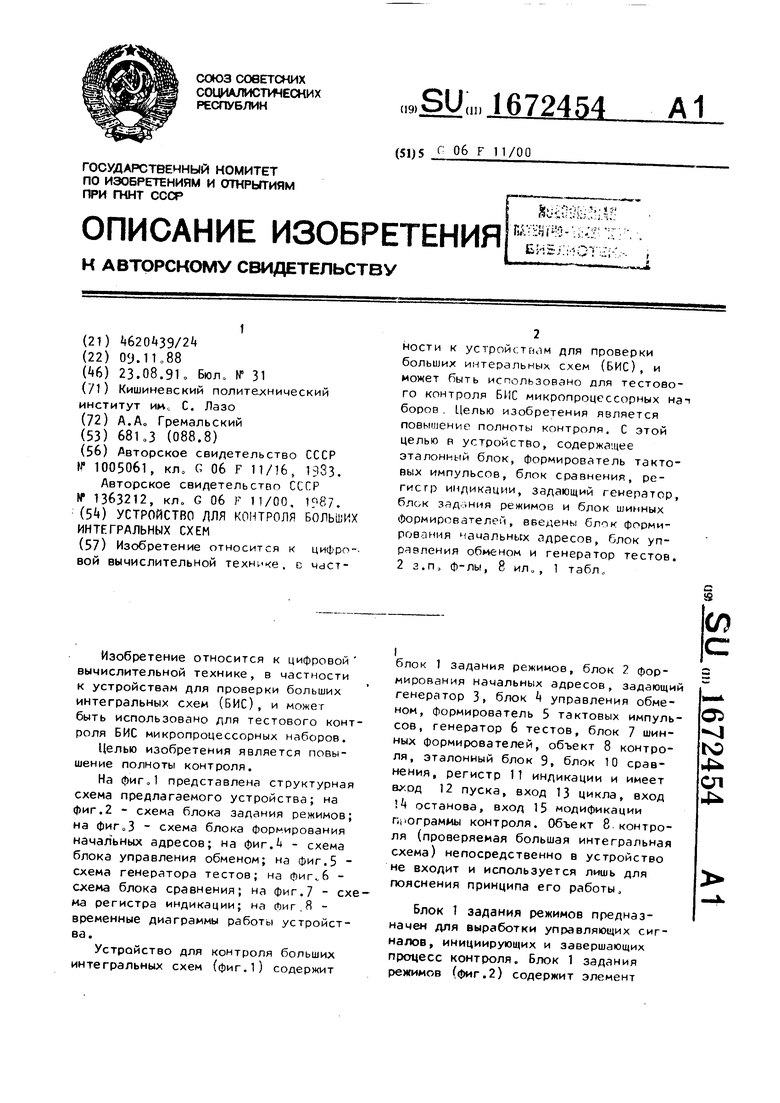

На фиг„1 представлена структурная схема предлагаемого устройства; на фиг.2 - схема блока задания режимов; на фиГоЗ - схема блока формирования начальных адресов; на фиг. 4 - схема блока управления обменом; на фиг.5 - схема генератора тестов; на фиг.6 - схема блока сравнения; на фиг.7 - схема регистра индикации; на Фиг.8 - временные диаграммы работы устройства.

Устройство для контроля больших интегральных схем (фиг.1) содержит

блок 1 задания режимов, блок формирования начальных адресов, задающий генератор 3, блок 4 управления обменом, формирователь 5 тактовых импульсов, генератор 6 тестов, блок 7 шинных формирователей, объект 8 контроля, эталонный блок 9, блок 10 сравнения, регистр 11 индикации и имеет вход 12 пуска, вход 13 цикла, вход J4 останова, вход 15 модификации программы контроля. Объект 8 контроля (проверяемая большая интегральная схема) непосредственно в устройство не входит и используется лишь для пояснения принципа его работы,

Блок 1 задания режимов предназначен для выработки управляющих сигналов, инициирующих и завершающих процесс контроля. Блок 1 задания режимов (фиг.2) содержит элемент

05 1

.Јъ СП

Дь

И 16, элемент ИЛИ 17 и триггер 18 пуска.

На фиг.З представлен пример реали зации блока 2 формирования начальных адресов применительно к проверке БИС микропроцессора КР 580 ИК 80 Блок 2 содержит первый 19 и второй 20 формирователи одиночного импульса, преобразователь 21 колов, элемент И 22 и элемент ИЛИ 23.

Формирователь 19 предназначен для выработки на своем выводе отрицательного импульса с Импульс г.ырабатывает- ся при изменении управляющего сигнала на входе формирователя с О в 1, Длительность импульса определяется числом тактов, необходимых для установки объекта 8 контроля и блока 9 в исходное состоя.ie (для БИС КР 580 ИК 80 не менее тактов). Отрицательный импульс с выхода фории рователя 19, поступая на вход разрешения преобразователя 21 кодов и на первый вход элемента И 22, логически отключает блок 2 формирования начальных адресов от блока 9 на время, необходимое для установки блока 9 в исходное состояние.

Формирователь 20 предназначен для выработки на своем выходе положительного импульса, длительность которого совпадает с длительностью сигнапа SYNC на управляющем выхоас микропроцессора КР 580 ИК Я0„ Импупьс вырабатывается при изменении ;щ.апляю- цего сигналу на входе формирователя с О в 1.

Преобразователь 21 кодоз предназначен для преобразования слова - состояния БИС микропроцессора в начальный адрес программы, реализующей соответствующий данному слову состояния протокол обмена. Преобразователь 21 кодов представляет собой комбинационную схему, реализующую следующие функции. Микропроцессор КР 580 ИК 80 имеет 10 машинных циклов,, Каждому циклу соответствует свой протокол (алгоритм) обмена с Каждый протокол обмена реализуется соответствующей программой из блока Д управления обменом

Начальный адрес конкретной программы обмена формируется на выходе преобразователя 21 кодов в зависимости от слова состояния блока 9 (вход D2) от кода на входе 15 модификации прог0

0

5

0

5

0

5

0

раммы контроля (вход D1) и от значения сигнала на выходе разрешения У.

Обозначим через А, А,. „ . ,А(, начальные адреса соответствующих программ обмена, обеспечивающие реилиэа- цию протоколов обмена при условии( что быстродействие БИС микропроцессора и быстродействие внешних по отношению к БИС устрой- тв совпадают. - Например, А.) - начальный адрес программы, соответствующий машинному циклу Ml,А,; начальны адрес программы, соотн. гствующий циклу чтения из ЗУ и т п Через Ас обозначим начальный адрес программы установки объекта 8 контроля и блока 9 в необходимое состояние Через , А ,..., обозначим начальные адреса соответствующих программ обмена, обеспечивающие реализацию протоколов обмена при условии, что быстродействие определенного возможного внешнего устройства БИС микропроцессора ниже (например, записи в ЗУ по длительности равен двум тактам синхронизации ЬИС). Через , А,.О.,А) О обозначим начальные адреса программ, обеспечивающие реализацию протоколов обмена при других временных параметрах внешних устройств (например, цикл обращения к стеку по длительности равен It тактам синхронизации БИС) 1 1 п.

Вы т) конкретной группы программ

(АО, А/, . ,), (A, А;, .. ,А;О),

(А , А(, , о ,AJ0 ) , „ „ „ выполняется с помощью кодов ня входах D1 преобра- зовате пя 21„

Чиспо групп программ определяется числом k возможных сочетаний временных параметров внешних устройств БИС микропроцессора, при которых необходимо обеспечить проверку объекта контроля. Тогда таблица истинности комбинационной схемы - преобразователя 21 имеет вид (X - безразличное значение сигнала), представленный в таблице.

В частности,преобразователь 21 может быть реализован в виде программируемой логической матрицы КР 556 РТ1 (16 входных, 8 выходных сигналов) либо в виде ПЗУ (КР 556 РТб или К РТ2) и др.

Задающий генератор 3 предназначен для формирования импульсов, синхронизирующих работу устройства. Импульсы на выходе генератора 3 вырабатываются при условии, что на его управляющем1

входе поддерживается сигнал л . . единицы

Блок Ц управления обменом предназначен для выработки входных управляющих сигналов блока 9 и объект,- контроля, сигналов управления генератором 6 тестов, управления блоком 7 шинных формирователей и управления регистром 11 индикации. Блок k управления обменом (фиг.) содержит первый 2, второй 25, третий 26 и четвертый 27 элементы И, элемент 28 задержки, счетчик 29, блок 30 памяти и имеет выходы поля управления 30.1, поля управления блоком шинных формирователей 30.2, поля опроса генераторов тестов 30.3 и поля разрешения сравнения З0.„

Блок 30 памяти предназначен для хранения программ, управляющих обменом с блоком Э и объектом 8 контроля, а также генератором 6 тестов, блоком 7 шинных формирователей и блоком 10 сравнения В зависимости от особенностей конкретного применения устройства блок 30 памяти можот быть выполнен в виде постоя ioi о либо оперативного запоминающего jjii i.

Формирователь 5 ТЛМООЫУ им. предназначен для формирования спнхю серий, подаваемых на входил , зации объекта 8 контролг 5лока 5„ Например, для БИС микроги / CCCOPJ КР 580 ИК 80 используются две -,оии синхроимпульсов - Ф1 и Ф2.

Генератор 6 тестов предналн-з (ен для выработки команд, адресов и данных, подаваемых на двунаправленные выводы объекта 8 контроля и блока 9. Генератор 6 тестов (фиг.5) содержит элемент 31 задержки, счетчик 32 тестов, блок 33 плмяти тестов, регистр 3k и имеет выходы 3.1 поля тестов и выход 3.2 поля конца госта.

Блок 10 сравнения предназначен для сравнения откликов объгкта 8 контроля и блока 9 в моменты времени определяемые сигналом на его управляющем входе. Блок 10 сравнения содержит (фиг.6) первую 35, вторую 36 и третью 37 схемы сравнения, элемент И 38 и триггер 39 результата,

Регистр 11 индикации предназначен для отображения результата контроля БИСо Регистр 11 индикации (фиг.7) содержит элемент НЕ 0, первый k и второй k2 триггеры, элемент 3 инди

0

5

0

5

0

5

0

5

одс-н и пем-jHi i ин,;;-кл ц и и Не годен.

Нд оиг,8 использованы следующие обозначения: i-1 ,, о , , 1$ - первый, второГ и так далее тактовые импульсы; , Т2 - синхросерии на выходах фор- миро ттеля 5 тактовых импульсов; RESfvT - сигнал на одном из выходов группы выходов 30,1 поля, подаваемого на управляющий вход установки объекта 8 контроля и блока 9 в исходное состояние; SYNC - сигнал на обходе блока 9, указывающий на то, что -о двунаправленным выводам юк. видается слово состояния БИС микропроцессора; А0 - начальный адрес прогртммы установки объекта 8 контроля и бл-jx,. 9 в исходное состояние; А,( - НЛ1 -, . ми - 0,;(рес программы цик ла М1 ; / - величина задержки элемента 2k задержки. Числа у временных дис: грамм от г. 8 указывают элементы, выходные сигналы которых приведены на диаграммах.

Устройство работает следующим образом .

г роп началом работы в блок 30 л. здмоуж ются программ управ- мйменом. В нулевом слове блока l n о разряде, соотретству- k. выходу ЗС.2, записывается значение 1

Нччкн,-, с адреса А, располагается npt р.змма установки объекта 8 контроля и блока 9 в исходное состояние, с лдрс.се А, - программа первого про- токого иомена (например, для БИС КР ЯО ИК 80 - программа выдачи управ- гя эщнх сигналов цикла Ml), с адреса АЈ- программа второго протокола обмена (например, программа выдачи управляющих сигналов при цикле обращения к ЗУ) и т.д, При этом каждому такту генератора 3 соответствует одно слово блока 3 памяти. В каждом . слове записывается следующая информация. В разрядах, соответствующих вы-; одам 30.1 , записываются значения вход,- |- - х управляющих сигналов объекта 8 Kiнтроля и блока 9 на рассматриваемом такте. В разряде, соответствующем выходу 30.2, записывается значение, определяющее направление передачи информации через блок 7 на рассматриваемом такте, 3 разряде, соответствующем выходу 30.3, записывается значение 1, если на рассматриваемом такте с выхода генератора 6 на двунап716

равленные выводы объекта 8 контроля и блока 9 подается тест (и О в противной случае). В разряде, соответствующем выходу 30,, записывается 1, если на рассматриваемом такте выполняется сравнение откликов объекта 8 и блока 9 (и О Б противном случае). Число слов каждой программы определяется числом тактов, необходимых для реализации соответствующего протокола обмена. Например, для БИС КР 580 ИК 80 каждый машинный цикл включает до пяти тактов.

Аналогично, начиная с адресов

АО А/,... А us, загружается вторая, с .и

адресов г,0,

A o.AV.ocjA - третья группа программ, управления обменом и т.д.

В блок 33 загружают гходные воздействия, тсе. коды , адреса и данные, подаваемые на объект 8 контроля и блок 9 в моменты времени, определяемые поступлением сигнала опроса на управляющий вход генератора 6 тестов. В исходном состоянии триггер 18 установлен в О, в счетчиках 29 и 32 записаны нули, триггер 39 результата установлен в 1, триггеры 41 и h2 установлены Е П (на фиг.1-7 устройства загрузки и сброса условно не показаны). При это генератор 3 отключен, на выходах блока 30 памяти и блока 33 памяти тестов устанавливается содержимое нулевых слов. .При этом, поскольку разряд нулевого слова, соответствующий выходу 30°2 (фиг.1), установлен в Г блок 7 настроен на прием информации с двунаправленных выводов обьекта Р контроля и блока 9. тем самым исключается влияние выход генератора 6 тестов на двунаправленные выводы до установки объекта 8 контроля и блока 9 в исходное состояние.

Предположим, что на входе 15 модификации программы контроля установлен нулевой код. При подаче на вход 12 устройства сигнала пуска триггер 18 пуска (фиг.2) устанавливается в сосУояние 1. Сигнал 1 с выхода триггера 18 пуска поступает на входы формирователей 19 и 20 (фиг.З). Одновременно рассматриваемый сигнал с прямого выхода триггера 18 пуска поступает-на вход генератора 3. Формирователь 19 одиночного импульса (фиг.З) вырабатывает отрицательный импульс длительностью (в случае БИС

0

0

5

0

5

0

5

КР 580 ИК 80) k такта. Формирователь

20одиночного импульса вырабатывает одиночный импульс (фиг.8) длительностью не более чем один такт0 Одновременно генератор 3 начинает выработку непрерывной последовательности импульсов, а формирователь 5 - выработку синхросерий 1 и 92, которые поступают на входы объекта 8 контроля и блока 9Импульс с выхода формирователя 19 поступает на вход разрешения V преобразователя 21. Поскольку V О и D1 0, на выкоде преобразователя

21устанавливается код АО - адрес начального слова программы установки объекта 8 контроля и блока 9 в исходное состояние. Одновременно рассматриваемый импульс устанавливает выход элемента 22 в Таким образом, управляющие выходы и двунаправленные выводы блока 9 логически отключены от выходов блока 2 формирования начальных адресов на время установки объекта ft контроля и блока 9

в исходное состояние.

Импульс с выхода формирователя 20 через элемент 23 покупает на вход пуска программы блока b (фиг.)о С приходом первого тактового импульса t на выходе элемента 2k появляется строб, который записывает в счетчик 13 коя с его информационного входа, т.е. значения А0. При этом запускается процесс чтения блока 30 памяти и на его выходах 30.1-30.4 появляются значения соответствующих разрядов первого слова программы. Сигналы с выходов 30 о 1 поступают непосредственно на управляющие входы объекта 8 контроля и блока 9. В случае БИС КР 580 ИК 80 входные управляющие сигналы равны нулю, за исключением сигнала RESET - установка в исходное состояние Разряд, соответствующий выходу 30.2, установлен в 1 - чтение с двунаправленных выводов объекта 8 контроля и блока 9. Разряды, соответствующие выходам 30.3 и 30.4, также установлены в 0м, т.е. опрос генератора 6 тестов и сравнения откликов объекта 8 контроля и блока 9 не выполняются,

К моменту выработки задающим генератором 3 второго тактового импульса на выходе формирователя 20 установлено значение О (фиг.8), поэтому на выходе элемента 23 устанавливается

значение О Второй тактовый пульс Ґj с выхода генератора 3 через элемент 2Г поступает на вход +1 счетчика 29 и его содержимое становится равным А о + 1 Из блоки , 1 считывается следующее слово. В т БИС КР 580 ИК 80 рассматриваемое -f - во совпадает с первым, т.е. на ляющем входе RESfT и во втором т кте подается значение 1

Аналогично с приходом третьего т «к- тового импульса , содержимое сче пика 29 становится равным 0 + 2 и иэ блока 30 памяти считывается очередное слово, которое также поддерживает на управляющем входе RISE1 значение 1.

С приходом четвертого тактового импульса ц содержимое счетчика 29 становится равным А0 + 3 (фиг.8), из блока 30 памяти считывается следующее слово, которое устанавливает сигнал RESET равным О. К этому моменту блок 9 устанавливается в исходное состояние и на его выходе устанавливается значение О. Однопр -еч- но на выходе формиров i 1 -твгрш- ется отрицательный им ,ул г и у- тнаапивается значение

iP,шая работа устройства t г (3t ,ifc) ()t тс сигналами на входах блок и Р, словом состояния.

К приходу пятого и г истовых импульсов t(, и t-f сиг -Ы -ч N м- выходах блока 9 равен О, поэ г выходы элементов 22 v 23 устан -темы в О, тактовые импульсы по ют на вход +1 счетчика 29, который последовательно формирует адреса АО + k и AQ + 5. Считываемые при этом из блока 30 памяти слора не изменяют сигналов на управляющих ДаХ объекта 8 кон роля и 9. Тем самым обеспечивается ре HIM оьида ния упраеляющих сигналов г выходов блока 9.

6 промежутке времени между шестым и седьмым тактовыми импульсами ь и ОГу блок 9 устанавливает сиг-ian SYNC в 1, указывая на то, чта по двунаправленным выводам выдается слово состояния БИС микропроцессора - блока 9. При этом на вы/оде элемента 22 появляется значение 1, которое через элемент 23 (фиг 3) поступает на вход пуска программы . Одновременно спово состояния БИС пока поступает на информационный вход

0

5

i j

0

5

0

5

-1,1If 1 Ь Т , г I

ко.1тьк на вход разрешения преоГ члэ- гэ ля 2I с выхода формирователя 19 поступает значение 1, на выходе iv-v о п5зователя 21 устанавливается А, программы обмена, соотрет- ггующей слову состояния на входе D2 tvtоГразователя. В случае БИС КР 58 и О на аходе преоСразсвателя 2| Г,С1 слово состояния цикла М1 вы- fi с чо команды, м нт его выходе вы v тывается код Л - начальный ,i;- )- г,рограммн обмена для рассматриваем и j чикла

Гед мой тактовый импульс L / через 2 Ч i тугает н синхровход счетчики 29 иг.) j описывает в нем адчес А ( 4,t iy t it. я ооцесс чтения из блокг jT n яги, -г рь хпце которого появ;/1°тся г чтс зммы оС- менр ,4пя цик 1 . i о ГЬУ гств юцис1 рг, р гь г вы-одо 30 1 -tciynaioi ьа

УПр RJ ЮЩИ З/СДь1 cf ьОКЧ, 8 И I fk u t q,fi.lXO 30 - r f/iOK 7,

с вых ;/1 p jp.i и - - первые вл°- fj ijit-M°4T о 6 ч 7 i тнетстRCHHO. / ° м, urr рпрчд, со i E e гствуп1Ц F Ч.1ДУ 3Г. , )Члеи EJ П| „Г1J pV h Ha B(CMi / TdhTOriblu

им у ,ь v. вых f(л 1л мем 28 (фчг.)

LK Р о -if т- 77 )С7} па т Не ВХОД

Рл , w исниь ( рЭ|Змеги г1 локгЭ 1 fi. При oiCf Р триггере .j |(. т. загисыГ - к-н р.Ло iT ГроВН ния .КОВ

эбге- i о Г нтром)- и Спок , выраба- тыв f- ь и лем М ijM3. n ,j. je г ipn-1Д н г нгчкоз в тоигг - pt 3 J , c 3yribT i г j,drncb Й4. ет начс- н,- i1 , в про s ) случае значсНи( ПРИ С7К1ИЧОП СОСтояь трмггерз 7Ь рсзультатз не изменяется, и пртцс ее ььн опне - 1Я лрог из рлока Т памяти ,тр(эдолжае г- ся„

К моменту при/ода . ледуюьме о, восьмого токтоаого имлугьсо 1 блок снимает сигнал 3VNC, поэтог, выходо эле- ; енпв 22 л 23 устано&гзны в О и -j ьмои тактов.1Й импульс д через эле- 25 поступает на вход +1 счетчика 29 и его содержимое становится разным At + 1. При JTOM из блока 30 памяти считывается втооое слово программы цикла Ml и на управляющие входы объекта 8 и блочз 9 подаются соответствующие сигналы. Если оазряд, соот- сзетсгьую ий выходу 30.3, ycTinoBjien в 1, через время f тактовьм импугьс

с выхода элемента 28 через элемент 26 поступает на вход опроса генератора

6тестов о При этом в регистре 3 (фиг.5) с выхода блока 33 памяти тестов записывается нулевое слово, соответствующие разряды КОТОРОГО с выходов поступают на вход блока

7и далее на объект 8 контроля и блок 9 Одновременно импульс с входа опроса через элемент 31 поступает на вход +1 счетчика тестов, увеличивая его содержимое на 1 При этом запускается процесс чтения из блока 33 памяти тестов и на его выходе устанавливается содержимое следующего слова. Таким образом, к приходу следующего сигнала опроса на информационном входе регистра 3 установлен очередной тест„

Очередной импульс генератора 3 вновь увеличивает содержимое счетчика 29, которое становится равным А + 2 и так далее до тех пор, пока

10

20

да элемента 0, а в триггер 2 - значение 1 V При этом включается элемент АЦ индикации Не годен. Нл этом процесс контроля завершен

Случай 2. При опросе генератора С тестов в регистр 3 (фиг.5) записывается код, устанавливающий выход 3.2 конца теста в I Значение 1 с выхода сбрасывает счетчик 32 тестов в нуль, подготавливая его для повторного пероПора адресов бпока 33 памяти,. При .-гом на зь ходах блока 33 памяти пояпл;:ьтся содержимое нулевого слова. Одновременно значение 1 с выхода конца теста поступает на второй ркод элемента 16 блока 1 (фиг,2).

Если на вход 13 цикла устройства подано значение 1 (режим однократной прогонки теста), выход элемента 16 устанавливается в 1 и через элемент 17 сбрасывается триггер 18 пуска с При этом блокируется работа

не завершится выполнение цикла Ml. генератора 3 и формирователя 5. Значение 1 с инверсного выхода тригге30

ра 18 пуска поступает на вход синхронизации регистра 11 и записывает в триггеры 1 и 2 результат контроля- значение 1 в триггер k и значение О Б тоиггер 2. При этом включается элемент 3 индикации Годен. На этои процесс контроля завершен.

Ее:и из вход 13 цикла устройства подано значение О (режим многократлее блок 9 вновь выставляет слово состояния и устанавливает сигнал SYNC в При этом блок 2 вновь формирует начальный адрес соответствующей программы обмена и выдает сигнал запуска программы. Путем установки соответствующих разрядов слов блока 30 памяти в О либо 1 обеспечивается подача управляющих сигналов на объект 8 и блок 9, управление блоком 7, опрос генератора 6 тестов, иой прогонки теста), выход элемента решение блока 10 сравнения,.16 остается в муле независимо от знаПри выполнении программ обмена аоз- чения сигнала конца теста и триггер ножны следующие случаи,18 пуска не изменяет своего состояния Процесс контроля продолжается, причем с приходом очередного сигнала опроса генератора 6 тестов (фиг.5) в регистр 3 с выхода блока 33 памяти тестов записывается нулевое слово. При этом соответствующий разряд с выхода снимает сигнал сброса счетчика 32, а сигнал опроса через

Случай 1 о При выполнении сравнения

обнаружено несовпадение откликов объекта 8 и блоков 9« При этом-хотя бы одна из схем 35 -.37 (фиг„6) вырабатывает на своем выходе значение О, которое через элемент 38 записывается, если сравнение в данном такте разрешено, в триггере 39 результата Значение 1 с инверсного выхода триггера 39 поступает на вход результата блока 1 и через элемент 17 (фиг„2) сбрасывает триггер 18 пуска в Сигнал с. прямого выг хода триггера 18 пуска блокирует работу генератора 3 и формирователь 5

40

45

50

задержку, задаваемую элементом 31, увеличивает содержимое счетчика 32 на единицу и т.д.

В режиме многократной прогонки тестов процесс контроля можно прекратить, подав на вход останова устройства значение При этом си|- нал 1 через элемент 17 (фиг.2)

В режиме многократной прогонки тестов процесс контроля можно прекратить, подав на вход останова устройства значение При этом си|- нал 1 через элемент 17 (фиг.2)

прекращает выработку синхросерий. Сиг-...

нал 1 с инверсного выхода триггера - сбрасывает триггер 18 пуска в О,

18 пуска поступает на вход синхрони-при этом работа генератора 3 и формизации регистра 11 (фп,7) и записыва-розателя 5 блокируется, а в регистр

ет в триггер И значение О с выхо11 аналогично описанному заносится

0

да элемента 0, а в триггер 2 - значение 1 V При этом включается элемент АЦ индикации Не годен. Нл этом процесс контроля завершен

Случай 2. При опросе генератора С тестов в регистр 3 (фиг.5) записывается код, устанавливающий выход 3.2 конца теста в I Значение 1 с выхода сбрасывает счетчик 32 тестов в нуль, подготавливая его для повторного пероПора адресов бпока 33 памяти,. При .-гом на зь ходах блока 33 памяти пояпл;:ьтся содержимое нулевого слова. Одновременно значение 1 с выхода конца теста поступает на второй ркод элемента 16 блока 1 (фиг,2).

Если на вход 13 цикла устройства подано значение 1 (режим однократной прогонки теста), выход элемента 16 устанавливается в 1 и через элемент 17 сбрасывается триггер 18 пуска с При этом блокируется работа

ра 18 пуска поступает на вход синхронизации регистра 11 и записывает в триггеры 1 и 2 результат контроля- значение 1 в триггер k и значение О Б тоиггер 2. При этом включается элемент 3 индикации Годен. На этои процесс контроля завершен.

Ее:и из вход 13 цикла устройства подано значение О (режим многократиой прогонки теста), выход элемента 16 остается в муле независимо от зна40

45

50

задержку, задаваемую элементом 31, увеличивает содержимое счетчика 32 на единицу и т.д.

В режиме многократной прогонки тестов процесс контроля можно прекратить, подав на вход останова устройства значение При этом си|- нал 1 через элемент 17 (фиг.2)

...

- сбрасывает триггер 18 пуска в О,

11 аналогично описанному заносится

результат контроля, и нключт и мент 3 индикации 1оден.

Проверка объекта контроля pt других сочетаниях временных параметров протоколов обмена выполняет и / установки Hi входе 15 модификаш и программ контроля кодт (номера) соответствующей группы (Ј о, , . . . , rtjv i j чальных адресов программ управг обменом Указанный код поступает т информационные входы 1)1 преобрази теля 21, поэтому после запуска в IP цессе формирования начальный адресе программ обмена на выходе преобразо- вателя 2} вырабатываются начальные адреса , А ,, ,А( и так далее и работа устройства происходит аналогично описанному.

ж

Формула изобретения

ИНФОРМАЦИОННЫЙ Пг О JJHHных формирователей соединен с информационным ВХОДОМ-ВЫХГ qe i f ПОГ НОГО блока, первый информационный выход блока шинных Формитв ттелс - пс дк юЧ6Н К ПерРОКу ИНфСОМаЦИ )ННОму В iqy

блока сравнения, втором информ ,и JH- ный выход бпока шиниы фпр иро ттеге) соединен с вторым IMI дом блок срнвнения, и t( пма- ционный вход блока CPTR НИР пляет- ся /отрпйства д я под к ж ния к информационному вы л/ i ъ кт контроля, информационнь выхг-( эг я энного блока подключен м ртому ин

5

О j

5

i (м ц пнному входу f ;шкт сравнения, пат i- 1Нфпрмационнь1й вход блока i pas- Hi нин является входом устройства для пгдчтючения к выходу признака готовi объекта контроля, выход призна- чз г тонности эталонного блока сое- пин н с шестым информационнь м вхслом Глокч сравнения, выход которого под- кпючен к информационному входу ре- истра индикации, входы пуска, цик/п останова устройства соединены с rrt гветствующими входами блока зада- HI режимов, от ли чающееся ем, U7o. с цепью повышения полноты чр тг r,,i, оно содержит блок формиро- ва-«и ч пьнык адресов, блок управления огмен м v генератор тестов, причем п ix л i-а и установки блока заданит ргжим ш подключен к входу начапьнои vcTdHoekn блока формировт- ния на1 альнчх адресов, результа- TL, блокт Формирования начальных адре- г (. i с входом пуска программы т. управления обменом, информа- ционнии выход блока формирования на- ч rv чь х адресов подключен к входу i f он neHMq , г вьи w - opoio соединен с вхо- i i г грнератсга тестов, второй

ь - бл КР упрпвл( ния обмег(ом под- к ЮЧРг управляю ,ему входу блока

-ннн/ vin эмирочате пей, третий выход (ч ( /пртвпения обменом соединен с ои р i sp-шения блока сравнения, четесрт ч в о од блока yпpaвг н я обме- i м г дк то ег к вх л,У режима талон Г( Л К Ч И )РПЯ€ТСЯ 9ЫХОДОМ УСТРОЙ

iтьа лгя псд люмгния к режима ъектр контроля, информационный ь/ог выход ттлонного блока соединен i перьым и нформационным входом блока Формирование начальных адресов, вы- х д признака готовнссти эталонного блокп подключен к входу разрешения блока Формирования начальных адресов, выход бпока сравнения соединен с - ходом результата блока задания ре- и 1мов, выход конца теста генератора стоп подключен к входу конца тес- Ti лока задания ре-кимов, тактовый генератора тестов соединен с информационным входом блока шинных фэрмирователей, выход задающего гене- рзгорт подключен к РХГДУ синхронизации блока управления обменом, вход м; дификации програм контроля устройства соединен с вторым информацией

1Ь16

ным входом блока формирования начальных адресов с

2С Устройство по п«1, от ли чающее с я тем, что блок управления обменом содержит четыре элемента И, элемент задержки, счетчик и блок памяти, причем первый вход первого элемента И соединен с инверсным входом второго элемента И и является входом пуска программы блока, информационный вход счетчика является входом операции блока, вход элемента задержки соединен с вторым входом первого элемента И и вторым входом второго элемента И и является входом синхронизации блока, выход первого элемента И соединен с входом приема счетчика, выход второго элемента И соединен со счетный входом счетчика, выход которого соединен с адресным входом блока памяти, выход элемента задержки соединен с вторым входом третьего элемента И и вторым входом четвертого элемента И, выходы поля управления блока памяти образуют четвертый вы- .ход блока, выход поля управления блоком шинных формирователей блока памяти образует второй выход блока, выход

0

5

поля опроса генератора тестов соединен с первым входом третьего элемента И, выход которого является первым входом третьего элемента И, выход которого является первым выходок (пока, выход поля разрешения сравнения блока памяти соединен с первым входом четвертого элемента И, выход которого является третьим выходом блока с

а

t

Ьгпф

Ј-гпф

02,

и

|2

%

51

шд Щ

7 77/9L

г

I

дгпф

7/41

Фиг. 8

| Устройство для контроля цифровых узлов | 1981 |

|

SU1005061A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| . | |||

Авторы

Даты

1991-08-23—Публикация

1988-11-09—Подача