(Л

00

tc

со оо

OKf

внешних устройств разного быстродействия. Цель достигается тем, что в устройство, соединенное с интерфейсной магистралью 1 внешних устройств и содержащее группы шинных формирователей адреса 2 и данных 6, генератор 3 тактовых сигналов, элемент И, регистр 5 состояния, дешифраторы адреса 7 и управляющих сигналов 8, узел 9 формирования сигнала готовности, включающий первый триггер 13, введены в узел 9 формирования сигнала готовности второй триггер 14 и три элемента ИЛИ 11,12 и 15. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системах обработки данных для связи микропроцессора с внешними устройствами, подключенных к интерфейсной магистрали. Цель изобретения - расширение области применения устройства за счет обеспечения возможности подключения к интерфейсной магистрали

1

Изобретение относится к вычислительной технике, в частности к средствам микропроцессорного управления, и может быть использовано в системах обработки даных и управления.

Цель изобретения - расширение области применения устройства за счет обеспечения возможности использования в системе внешних устройств разного быстродействия.

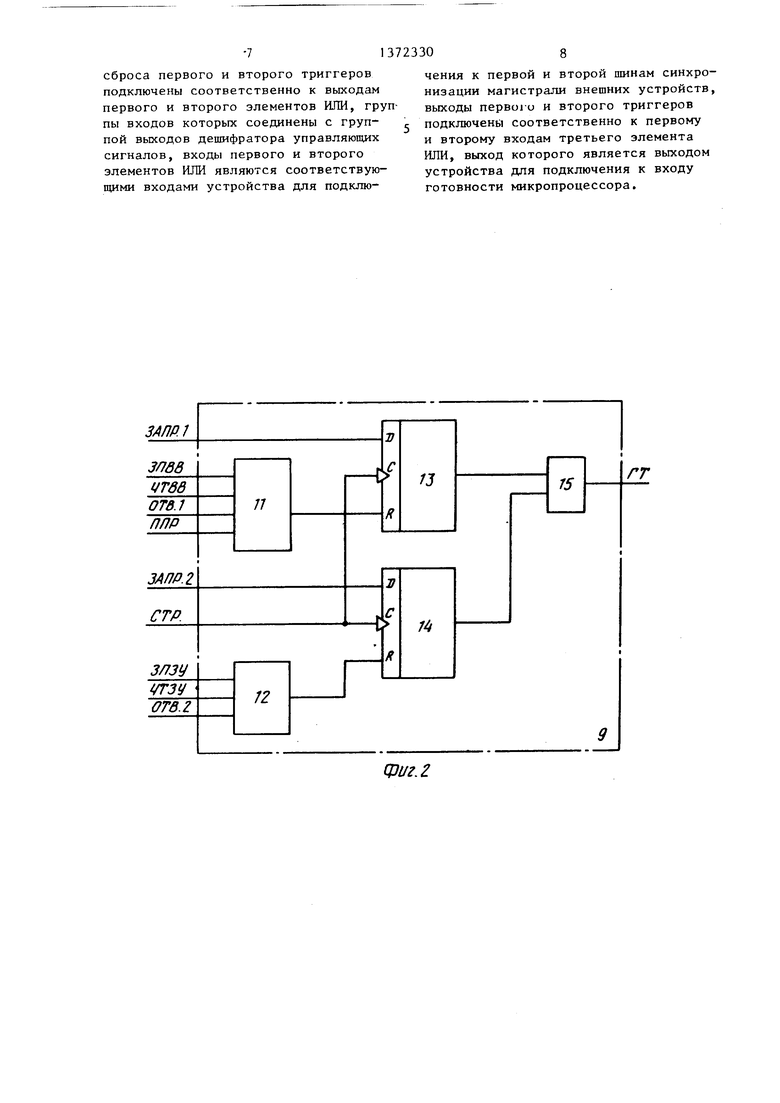

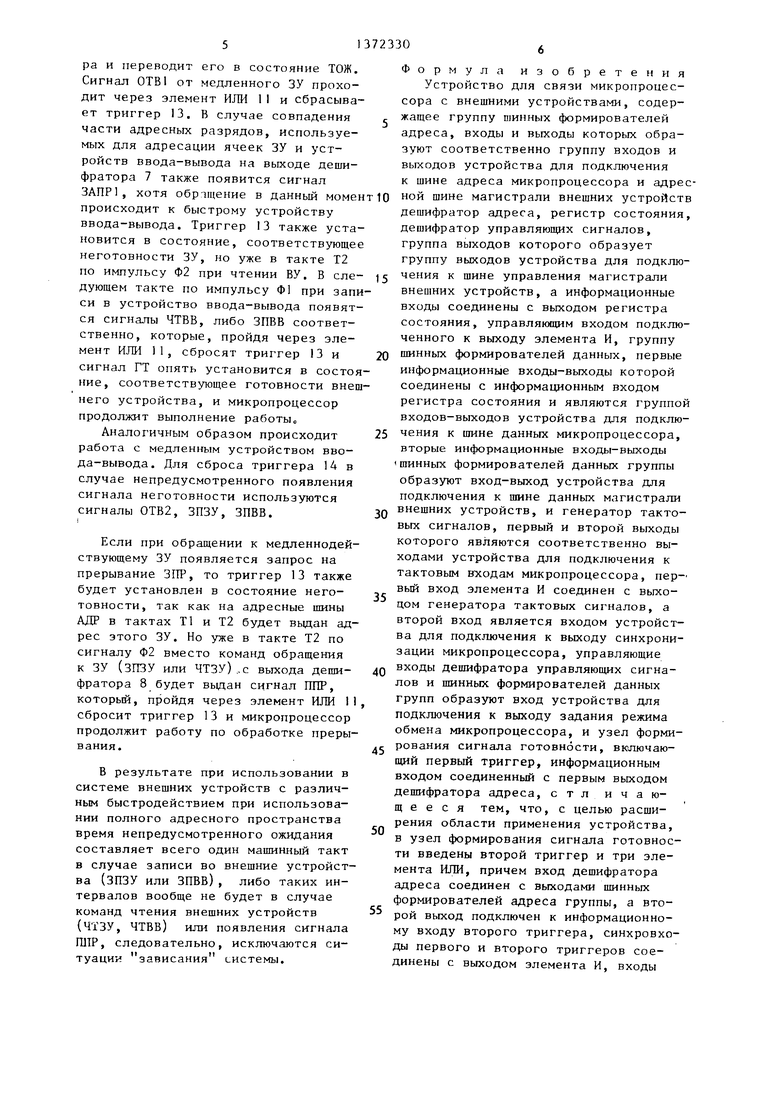

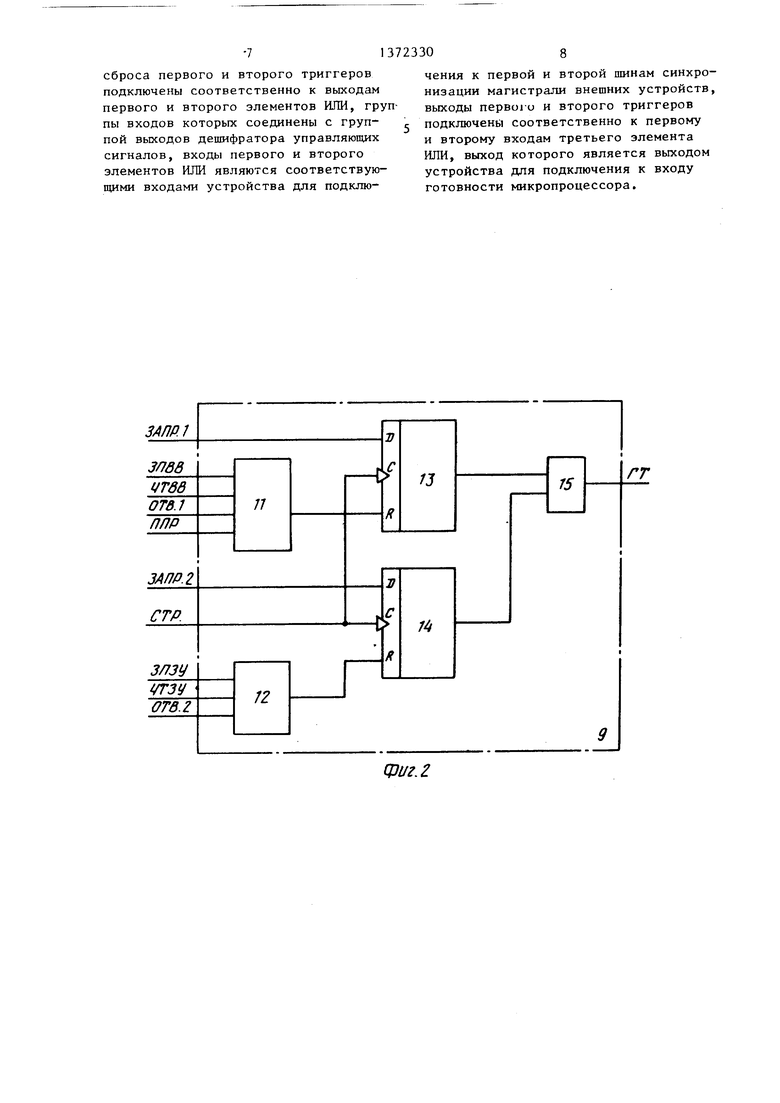

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональна схема узла формирования готовности; на фиг.З - временная диаграмма работ устройства.

Устройство соединено с интерфейсной магистралью I внешних устройств и содержит (фиГоО группу шинных формирователей 2 адреса, генератор 3 тактовых сигналов, элемент И 4, регистр 5 состояния, группу шинных формирователей 6 данных, дешифратор 7 адреса, дешифратор 8 управляющих сигналов и узел 9 формирования сигнала готовности о К интерфейсной магистрали 1 подключены внешние устройства 10, которые представляют собой либо ЗУ, либо устройства ввода-вьшода, том числе и медленнодействукяцие, требующие работы в режиме ожидания.

В качестве медленнодействующего ЗУ может быть использовано, например постоянное запоминающее устройство с многократным перепрограммированием с электрической записью и стиранием информации типа KI60IPP1, в качестве медленнодействующего устройства ввода-вывода - электрическая пишущая машинка типа Консул,

Узел 9 формирования сигнала готовности (фиг.2) содержит элементы ИЛИ

o

5

0

5

0

5

0

11 и 12, триггеры 13 и 14 и элемент ИЛИ 15.

Для связи с внешними устройствами ввода-вывода и устройствами памяти используются следующие сигналы интерфейсной магистрали 1:АДР - адресные, указывающие адрес ячейки памяти или устройства ввода-вьюода; ИНФ - информационные, служащие для передачи данных, команд, состояний и др.; ЧТЗУ - чтение памяти, указывает, что производится считывание информации (команд, данных и т.д.) из устройства памяти; ЗПЗУ - запись в память, указывает, что производится запись информации в устройства памяти; ЧТВВ - чтение устройства ввода- вывода, указывает, что производится считывание информации из внешних устройств ввода-вывода; ЗПВВ - запись в устройства ввода-вывода, указывает, что производится запись во внешние устройства ввода-вывода; ОТВ - ответ, сообщающий, что указанная операция вьтолнена; ЭПР - запрос прерывания; ППР - подтверждение прерывания.

Устройство использует следующие сигналы микропроцессора (580ВМ80): АО-А15 - адресные, указывающие адрес ячейки памяти или адреса внешнего устройства ввода-вывода; ДО-Д7 - данных, предназначенных для передачи данных команд, состояний; СИНХР - синхронизирующий, указьшающий начало каждого машинного цикла микропроцессора; ПРИЕМ - указывает , что шины данных ДО-Д7 находятся в режиме ввода информации в микропроцессор; ВЫДАЧА - указывает, что шины данных находятся в режиме вывода информации из микропроцессора; ГТ - сигнал готовности, указывающий, что на шинах данных имеется информация;,Ф1, Ф2 - тактирующие и тульсы..

Устройство для связи и обмена информацией по и)1терфейсной магистрали 1 обеспечивает программный режим под воздействием микропроцессора и режим организации связи и обмена информа- цией по прерыванию.

В начале каждого машинного цикла в такте Т1 микропроцессор вырабатывает синхронизирующий сигнал СИНХР. В этом же такте микропроцессор устанавливает на адресных шинах АО-А15 код адреса ячейки памяти или устройства ввода-вывода. Адрес остается постоянным до появления импульса Ф2 в такте, который слегует за тактом ТЗ данного цикла, В такте Т1 на шины данных выдается 8-разрядное управляющее слово.

В такте Т2 по импульсу Ф2 сигнал СИНХР снимается и выставляется сигна ПРИЕМ, микропроцессор переходит в режим приема информации. В такте Т2 по заднему фронту импульса Ф2 также осуществляется анализ сигнала ГТ.

В зависимости от значения этого сиг

нала производится либо переход к такту ТЗ машинного цикла, либо переход в состояние ТОЖ, выход из которого виз- можен только при наличии на входе ГТ микропроцессора сигнала, соответствующего готовности ЗУ или внешнего устройства ввода-вьшода.

В такте ТЗ данные из ЗУ или внешнего устройства ввода-вывода принимаются на шину данных, по импульсу Ф снимается сигнал на выходе ПРИЕМ,

В тактах Т4 и Т5, если они необходимы, выполняются действия над операндами. По импульсу Ф2 цикла Т4 значение адреса на шине адреса изменяет- ся и его значение является неопределенным до появления импульса Ф2 такта Т1 следующего цикла.

Диаграмма работы микропроцессора при выдаче информации отличается от рассмотренной лишь тем, что сигнал ВЫДАЧА появляется по импульсу Ф2, в такте, следующем за тактом Т2, а снимается по импульсу Ф1 такта Т4.

В последнем такте последнего цикла команды проверяется уровень сигнала на входе ЗПР микропроцессора. При высоком уровне этого сигнала и установленном ранее внутреннем триггере

JQ

20

25

30

35

,-

.

50

5

РАЗРЕШЕНИГ. ПРЕРЫВАНИЯ микропроцессор по тактовому импульсу Ф2 данного такта устанавливает внутренний трип-ер ПРЕРЫВАНИЕ. След тощий цикл будет циклом ПРЕРЫВАНИЕ. В этом цикле в управляющем слове устанавливается разряд Подтверждение запроса прерывания. После дешифрации управляющего слова этому коду будет соответствовать сигнал ППР (подтверждение прерывания)о Устройство, выдавшее запрос на прерывание, воспринимает его и вьщает на информационные щины ИНФ код вектора прерывания.

Таким образом, из описания временной диаграммы работы микропроцессора можно сделать выводы: есть периоды, когда разряды адресной шины находятся Б неопределенном состоянии; сигнал готовности должен быть определен до появления командных сигналов на шине управления; между анализом сигнала ЗШ и выдачей управляющего сигнала ППР микропроцессор проверяет сигнал ГТ.

Устройство работает следующим образом.

По сигналу СИНХР и импульсу Ф2 через элемент И 4 в регистр 5 заносится код управляющего слова, опреде- ляюп1ий режим работы микропроцессора в данном цикле. Разряды управляющего слова поступают на вход дешифратора 8, где производится декодирование и формирование по сигналам микропроцессора ПРИЕМ или ВЫДАЧА одного из сигналов управления интерфейсной магистрали ЗПЗУ, ЧТЗУ, ЗПВВ, ЧТЬВ, ППР.

При обращении микропроцессора к медленному устройству (внешнему ЗУ, либо устройству ввода-вывода) на выходе дешифрато ра 7 вырабатываются сигналы запроса на ожидание ЗАПР1 или ЗАПР2, которые соответствуют либо обращению к медленному ЗУ (ЗАПР1), либо обращение к медленному ВВ (ЗАПР2)о Сигналы ЗПР1 и ЗАЛР2 поступают соответственно на входы триггеров 13 и 14.

Работа схемы в случае обращения к медленному ЗУ осуществляется следующим образом. По сигналу СИНХР и импульсу Ф1 на выходе триггера 13 установится сигнал, соответствующий неготовности ЗУ. Через элемент ИЛИ 15 он поступает на вход микропроцессоpa и переводит его в состояние ТОЖ. Сигнал ОТВ1 от медленного ЗУ проходит через элемент ИЛИ 1I и сбрасывает триггер 13. В случае совпадения части адресных разрядов, используемых для адресации ячеек ЗУ и устройств ввода-вывода на вькоде дешифратора 7 также появится сигнал ЗАПР1, хотя обращение в данный момен происходит к быстрому устройству ввода-вывода. Триггер 13 также установится в состояние, соответствующее неготовности ЗУ, но уже в такте Т2 по импульсу Ф2 при чтении ВУ. В еле- дующем такте по импульсу Ф1 при записи в устройство ввода-вывода появятся сигналы ЧТВВ, либо ЗПВВ соответственно, которые, пройдя через элемент ИЛИ 11, сбросят триггер 13 и сигнал ГТ опять установится в состояние, соответствующее готовности внешнего устройства, и микропроцессор продолжит выполнение работы

Аналогичным образом происходит работа с медленным устройством ввода-вывода. Для сброса триггера 14 в случае непредусмотренного появления сигнала неготовности используются

сигналы ОТВ2, ЗПЗУ, ЗПВВ.

I

Если при обращении к медленнодействующему ЗУ появляется запрос на прерывание ЗГТР, то триггер 13 также будет установлен в состояние него- товности, так как на адресные шины АДР в тактах Т1 и Т2 будет выдан адрес этого ЗУ. Но уже в такте Т2 по сигналу Ф2 вместо команд обращения к ЗУ (ЗПЗУ или ЧТЗУ)„с выхода деши- фратора 8 будет выдан сигнал ППР, который, пройдя через элемент ИЛИ 1 сбросит триггер 13 и микропроцессор продолжит работу по обработке прерывания.

В результате при использовании в системе внешних устройств с различным быстродействием при использовании полного адресного пространства время непредусмотренного ожидания составляет всего один машинный такт в случае записи во внешние устройства (ЗПЗУ или ЗПВВ), либо таких интервалов вообще не будет в случае команд чтения внешних устройств (ЧТЗУ, ЧТВВ) или появления сигнала Ш1Р, следовательно, исключаются ситуации зависания системы.

Формула изобретения Устройство для связи микропроцессора с внешними устройствами, содержащее группу шинных формирователей адреса, входы и выходы которых образуют соответственно группу входов и выходов устройства для подключения к шине адреса микропроцессора и адресной шине магистрали внешних устройств дешифратор адреса, регистр состояния, дешифратор управляющих сигналов, группа выходов которого образует группу выходов устройства для подключения к шине управления магистрали внешних устройств, а информационные входы соединены с выходом регистра состояния, управляюо1им входом подключенного к выходу элемента И, группу шинных формирователей данных, первые информационные входы-выходы которой соединены с информационным входом регистра состояния и являются группой входов-выходов устройства для подключения к шине данных микропроцессора, вторые информационные входы-выходы «шинных формирователей данных группы образуют вход-выход устройства для подключения к шине данных магистрали внешних устройств, и генератор тактовых сигналов, первый и второй выходы которого являются соответственно выходами устройства для подключения к тактовым входам микропроцессора, пер- вый вход элемента И соединен с выходом генератора тактовых сигналов, а второй вход является входом устройства для подключения к выходу синхронизации микропроцессора, управляющие входы дешифратора управляющих сигналов и шинных формирователей данных групп образуют вход устройства для подключения к выходу задания режима обмена микропроцессора, и узел формирования сигнала готовности, вк1пючаю- щий первый триггер, информационным входом соединенный с первым выходом дешифратора адреса, отличающееся тем, что, с целью расширения области применения устройства, в узел формирования сигнала готовности введены второй триггер и три элемента ИЛИ, причем вход дешифратора адреса соединен с выходами шинных формирователей адреса группы, а второй выход подключен к информационному входу второго триггера, синхровхо- ды первого и второго триггеров соединены с выходом элемента И, входы

сброса первого и второго триггеров подключены соответственно к выходам первого и второго элементов ИЛИ, группы входов которых соединены с группой выходов дешифратора управляющих сигналов, входы первого и второго элементов ИЛИ являются соответствующими входами устройства для подклюЗАПР.1

ЗЛвЗ

ijTee

отел

/7

ЗА ПР. 2

СТР.

ЗЛЗУ

чения к первой и второй шинам синхронизации магистрали внешних устройств, выходы nepBoi o и второго триггеров подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого является выходом устройства для подключения к входу готовности микропроцессора.

/J

75

ГТ

/

Фиг. 2

DO-If7 CuHxp

Фиг.З

| Устройство микропроцессорной связи | 1981 |

|

SU934466A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-07—Публикация

1986-08-27—Подача