Изобретение относится к электросвязи, к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне.

Цель - упрощение устройства путем исключения дополнительного оборудования и повышения степени ослабления временных флюктуаций тактовых импульсов.

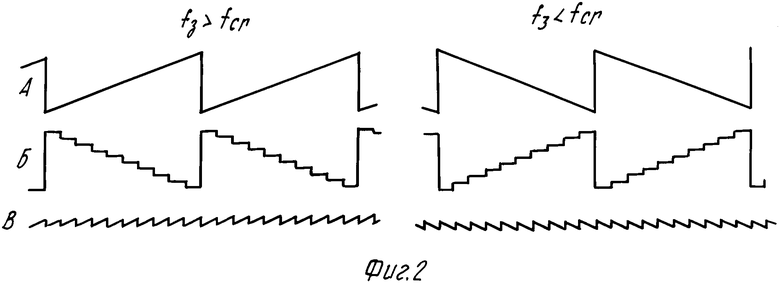

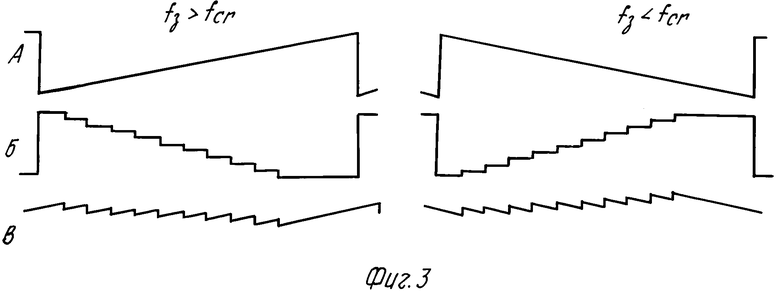

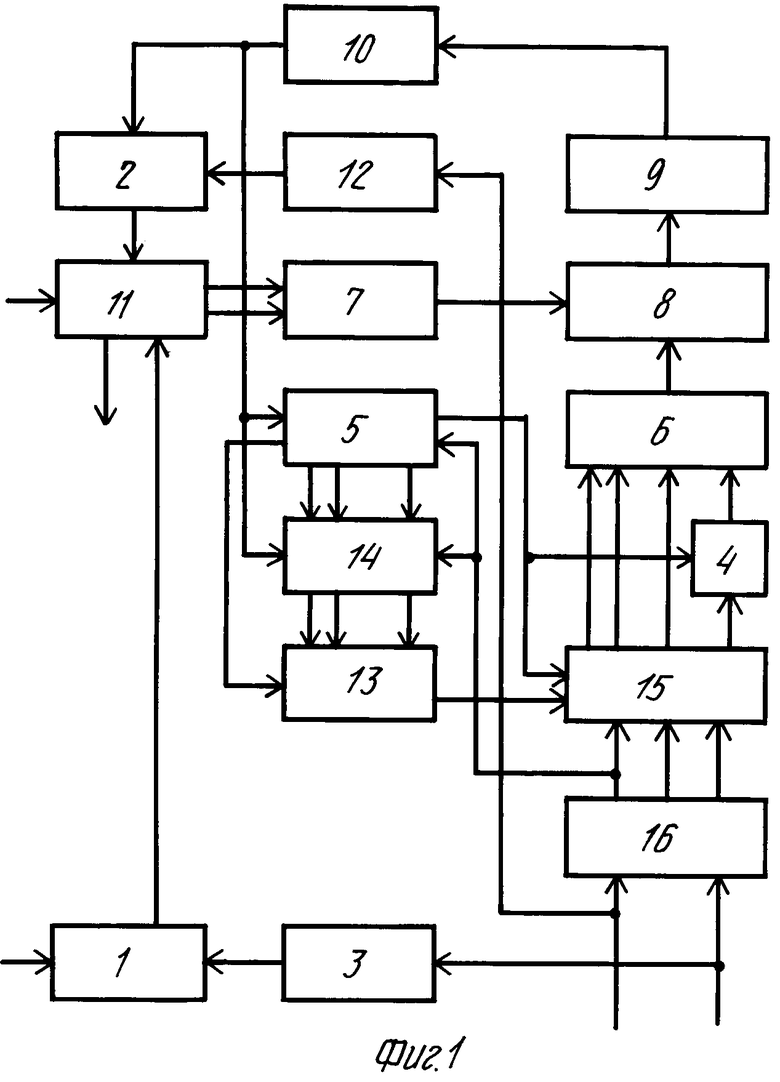

На фиг. 1 изображена функциональная схема устройства цифровой фазовой автоматической подстройки частоты; на фиг. 2 и 3 - временные диаграммы устройства цифровой фазовой автоматической подстройки частоты.

Устройство цифровой фазовой автоматической подстройки частоты содержит первый элемент И 1, второй элемент И 2, первый инвертор 3, элемент ИЛИ 4, счетчик 5 импульсов, цифроаналоговый преобразователь (ЦАП) 6, временной детектор 7, сумматор 8, фильтр 9 нижних частот, генератор 10 тактовых импульсов, блок 11 динамической памяти, второй генератор 12, делитель 13 частоты с переменным коэффициентом деления, преобразователь 14 кода, реверсивный счетчик 15, блок 16 управления.

Устройство цифровой фазовой автоматической подстройки частоты работает при условии равенства номинальных значений частот записи и считывания fз.ном = fсч.ном. , но так как генераторы тактовых импульсов записи и считывания не синхронизированы, то реальные значения частот отличаются одна от другой и от номинального значения на величину, не превышающую допустимого значения.

На первый вход блока 11 поступает информационный сигнал. Тактовые импульсы записи через первый элемент И 1 поступает на второй вход блока 11, с помощью которых осуществляется поочередная запись символов информационного сигнала в ячейки памяти. Если в информационном сигнале присутствуют положительные вставки, на первый вход блока 16 и вход первого инвертора 3 одновременно с названными вставками поступают импульсы положительных вставок, имеющие положительную полярность и длительность один тактовый интервал. Указанные импульсы через первый инвертор 3 поступают на второй вход первого элемента И 1 и запирают его на время одного тактового интервала. При этом на второй вход блока 11 тактовый импульс не поступает и символ положительной вставки в память не записывается.

Считывание информационного сигнала происходит с помощью тактовых импульсов, поступающих с выхода генератора 10 через второй элемент И 2 на третий вход блока 11. Если в информационном сигнале присутствуют отрицательные вставки, на второй вход блока 16 и вход второго инвертора 12 одновременно с названными вставками поступают импульсы отрицательных вставок, имеющие положительную полярность и длительность один тактовый интервал. Указанные импульсы через второй инвертор 12 поступают на второй вход второго элемента И 2 и запирают его на время одного тактового интервала. При этом на третий вход блока 11 тактовый импульс не поступает и на первый выход блока 11 проходит символ информационного сигнала из предыдущего тактового интервала. На второй и третий выходы блока 11 поступают импульсы с распределителей записи и считывания соответственно, так как частоты записи и считывания не равны, то временной интервал между моментами записи и считывания изменяется после каждого считывания на величину Δt = Tз - Tсч, где Тз = 1/fз, Тсч = 1/fсч, на эту же величину изменяется временной сдвиг между импульсами на втором и третьем выходах блока 11. Названные импульсы поступают на первый и второй входы временного детектора 7. Временной интервал между импульсами на втором и третьем выходах блока 11 изменяется по линейному закону в следующих пределах. В установившемся (рабочем) режиме на величину Тсч. , а при срыве синхронизма - на величину LTсч, где L - количество ячеек памяти в блоке 11. В тех же пределах изменяется длительность импульсов на выходе временного детектора 7, а усредненное значение напряжения изменяется от 0 до амплитудного значения этих импульсов, спадает до нуля и снова нарастает, т. е. изменяется по пилообразному закону с периодом 1L/ fз-f

fз-f . Названные импульсы поступают на первый вход сумматора 8. С выхода сумматора 8 эти импульсы поступают на вход фильтра 9. Частоты упомянутых импульсов значительно выше частоты среза фильтра 9, т. е. за полосой пропускания. Поэтому на выход фильтра 9 проходит только усредненное значение напряжения этих импульсов - пилообразный сигнал, и поступают на вход генератора 10, состоящего из последовательно соединенных усилителя постоянного тока, генератора управляемого напряжением и компаратора. Тактовые импульсы с выхода генератора 10 через второй элемент И 2 поступают на третий вход блока 11. Описанная часть устройства является аналоговой петлей подстройки частоты.

. Названные импульсы поступают на первый вход сумматора 8. С выхода сумматора 8 эти импульсы поступают на вход фильтра 9. Частоты упомянутых импульсов значительно выше частоты среза фильтра 9, т. е. за полосой пропускания. Поэтому на выход фильтра 9 проходит только усредненное значение напряжения этих импульсов - пилообразный сигнал, и поступают на вход генератора 10, состоящего из последовательно соединенных усилителя постоянного тока, генератора управляемого напряжением и компаратора. Тактовые импульсы с выхода генератора 10 через второй элемент И 2 поступают на третий вход блока 11. Описанная часть устройства является аналоговой петлей подстройки частоты.

В зависимости от значения частоты согласования (частоты следования импульсов вставок) fс имеют место три случая: 1 - при fc > fп; 2 - при fп > fc > fн; 3 - при fc < fн, где fп - частота согласования, при которой происходит переключение режима работы устройства; fн - минимальная частота согласования, ниже которой наблюдается увеличение временных флюктуаций тактовых импульсов 1/fн = 2i+п, К≈ max .

В первом случае fc > fп. Это характеризуется тем, что переменные составляющие спектра управляющего сигнала эффективно подавляются с помощью фильтра 9 и временные флюктуации тактовых импульсов имеют пренебрежимо малые значения.

На (m+2)-м выходе счетчика 5 формируется потенциал логической "1", которым реверсивный счетчик 15 устанавливается в состояние логического "0". Потенциал логической "1" с (m+2)-го выхода счетчика 5 через элемент ИЛИ 4 поступает на n-й вход ЦАП 6, на остальные входы которого поступают потенциалы логического "0", в результате чего на входах преобразователя устанавливается комбинация вида 10. . . 0, а на выходе его - потенциал, равный среднему значению диапазона изменения выходного напряжения, который поступает на второй вход сумматора 8. В сумматоре 8 на этот потенциал накладывается сигнал, поступающий на первый его вход. Полученный суммарный сигнал через фильтр 9, с помощью которого подавляются переменные составляющие спектра этого сигнала, поступает на вход генератора 10 и управляет его частотой.

Во втором случае fп > fc > fн. Это характеризуется недостаточным подавлением переменной составляющей сигнала, формируемого временным детектором 7. С целью обеспечения необходимого подавления переменной составляющей названного сигнала формируется ступенчатый сигнал, который складывается в сумматоре 8 с управляющим сигналом в противофазе. При этом на выходе сумматора 8 формируется управляющий сигнал с меньшим значением переменной составляющей и более высокой частотой.

Если fз > fсч, где fз и fсч - частоты записи и считывания соответственно, на выходе временного детектора 7 формируются импульсы переменной длительности с изменяющимся по величине усредненным значением напряжения. На первый вход блока 16 поступают импульсы положительных вставок, на втором выходе которого формируется потенциал логического "0", а на третьем выходе - логической "1". Импульс вставки с первого выхода поступает на (m+1)-й вход преобразователя 14 кода, записывая в его буферный регистр число, присутствующее на его m входах, на второй вход счетчика 5, устанавливая его в состояние логического "0", и на первый вход реверсивного счетчика 15, устанавливая его в состояние логической "1".

На выходах преобразователя 14 формируется код, устанавливающий необходимый коэффициент деления (К≈ ) делителя 13 с переменным коэффициентом деления. Коэффициент деления (К ≈ ) выбирается таким образом, чтобы от одного импульса вставки до другого на выходе делителя 13 сформировалось 2n - γ импульсов, где γ имеет значения 0,2,2,3. . . и ограничивается значением дискретизации коэффициента деления К≈. При этом на выходе делителя 13 формируются импульсы частотой fсч/2LoK≈ и поступают на счетный вход реверсивного счетчика 15, который осуществляет счет на уменьшение числа на выходах от значения 11. . . 1 до γ . С выходов реверсивного счетчика 15 текущее число поступает на соответствующие входы цифроаналогового преобразователя 6, на выходе которого формируется ступенчатый сигнал и поступает на второй вход сумматора 8 формируется управляющий сигнал, амплитуда переменной составляющей которого в γ /2n-γ раз меньше значения переменной составляющей на выходе при отсутствии ступенчатого сигнала, а частота выше во столько же раз. Переменная составляющая этого сигнала эффективно подавляется фильтром 9.

При fз < fсч на второй вход блока 16 поступают импульсы отрицательных вставок, на втором выходе которого формируется потенциал логической "1", а на третьем - логического "0".

Преобразователь 14, делитель 13 и счетчик 5 работают как описано выше (при fз >fсч). Реверсивный счетчик 15 осуществляет счет от значения 00. . . 0 до 2n- γ. На выходе ЦАП 6 формируется ступенчатый сигнал, а на выходе временного детектора 7 - импульсы с переменной скважностью, имеющие усредненное значение, изменяющееся по пилообразному закону со спадающей пологой частью. На выходе сумматора 8 сигнал имеет треугольную форму со спадающей пологой частью с амплитудой, уменьшенной в 2n- γ/γ раз и во столько же раз увеличенной частотой. Это переменная составляющая эффективно подавляется с помощью фильтра 9.

В третьем случае fc < fн устройство работает аналогично работе его во втором случае. Отличие состоит в том, что компенсация пилообразной составляющей управляющего сигнала становится нe полной и счетчик 5 и реверсивный счетчик 15 досчитывают до конечных значений (счетчик 5 - до значения 11. . . 1, а реверсивный счетчик 15 - до 11 1 или 00. . . 0, в зависимости от соотношения частоты (fз и fсч) останавливаются в названных значениях до прихода очередного импульса вставки. В этом случае делитель 13 имеет максимальное значение коэффициента деления (К ≈ max). При остановке реверсивного счетчика 15 на входы ЦАП 6 поступают постоянные потенциалы и на его выходе формируется постоянный потенциал (см. фиг. 3, Б), а на выходе временного детектора 7 - пилообразный сигнал. На выходе сумматора 8 формируется импульс треугольной формы (В), который не может быть эффективно сглажен фильтром 9. Указанные отличия приводят к возрастанию временных флюктуаций тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОСИТЕЛЬНЫХ УРОВНЕЙ ПОБОЧНЫХ КОЛЕБАНИЙ РАДИОПЕРЕДАТЧИКОВ | 1990 |

|

RU2033618C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Генератор синусоидальных сигналов | 1990 |

|

SU1734189A1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

Использование: в электросвязи, а именно в системах передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне. Сущность изобретения: для формирования ступенчатого сигнала и использования его для компенсации переменной составляющей управляющего сигнала устройство содержит первый, второй элементы И 12, первый, второй инверторы 3, 12, элемент ИЛИ 4, счетчик 5 импульсов, цифроаналоговый преобразователь 6, временной детектор 7, сумматор 8, фильтр 9 нижних частот, генератор 10 тактовых импульсов, блок 11 динамической памяти, делитель 13 частоты с переменным коэффициентом деления, преобразователь 14 кода, реверсивный счетчик 15, блок 16 управления. Устройство обеспечивает упрощение путем исключения дополнительного оборудования и повышения степени ослабления временных флоктуаций тактовых имплуьсов. 3 ил.

УСТРОЙСТВО ЦИФРОВОЙ ФАЗОВОЙ АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ, содержащее первый и второй элементы И, элемент ИЛИ, первый инвертор, счетчик импульсов, цифроаналоговый преобразователь (ЦАП) и последовательно соединенные временной детектор, сумматор, фильтр нижних частот (ФНЧ) и генератор тактовых импульсов (ГТИ), отличающееся тем, что в него введены блок динамической памяти, блок управления и последовательно соединенные преобразователь кода, делитель частоты с переменным коэффициентом деления и реверсивный счетчик, n - 1 выходов которого подключены к одноименным входам цифроаналогового преобразователя (ЦАП), а n-й выход через элемент ИЛИ к n-му входу ЦАП, выход которого подключен к второму входу сумматора, первый вход блока динамической памяти является информационным входом устройства, второй и третий входы подключены к выходам первого и второго элементов И соответственно, первый выход является информационным выходом устройства, второй и третий выходы подключены к первому и второму входам временного детектора соответственно, первый вход первого элемента И являются тактовым входом устройства, а второй вход подключен к выходу первого инвертора, вход которого объединен с первым входом блока управления и является входом сигналов положительных вставок устройства, второй вход блока управления объединен с входом второго инвертора и является входом сигнала отрицательных вставок устройства, первый, второй и третий управляющие выходы блока управления подключены к одноименным входам реверсивного счетчика, импульсный вход которого объединен с вторым входом второго элемента ИЛИ и подключен к (m + 2)-му выходу счетчика импульсов, тактовый вход которого объединен с тактовым входом преобразователя кода, выходом ГТИ и первым входом второго элемента И, управляющий вход счетчика импульсов объединен с одноименным входом преобразователя кода и подключен к первому управляющему выходу блока управления, счетный выход счетчика импульсов подключен к одноименному входу делителя частоты с переменным коэффициентом деления, выход второго инвертора подключен к второму входу второго элемента И, m выходов счетчика импульсов подключены с соответствующим m-входам преобразователя кода.

Авторы

Даты

1994-05-30—Публикация

1991-06-22—Подача